优秀的 Verilog/FPGA开源项目介绍

https://zhuanlan.zhihu.com/p/423332071

https://github.com/YosysHQ/picorv32

picoRiscV

这个其实不需要过多介绍了,小巧且完善的RISC-V。

PicoRV32 是实现RISC-V RV32IMC 指令集的 CPU 内核。它可以配置为 RV32E、RV32I、RV32IC、RV32IM 或 RV32IMC 内核,并可选择包含内置中断控制器。

特点:

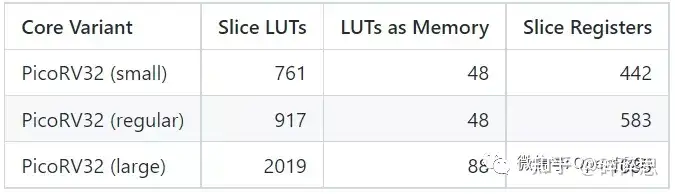

- 小型(7 系列 Xilinx 架构中的 750-2000 个 LUT)

- 高 fmax(7 系列 Xilinx FPGA 上为 250-450 MHz)

- 可选择的本机内存接口或 AXI4-Lite 主控

- 可选的 IRQ 支持(使用简单的自定义 ISA)

- 可选的协处理器接口

- 该 CPU 旨在用作 FPGA 设计和 ASIC 中的辅助处理器。由于其高fmax,它可以集成到大多数现有设计中,而无需跨越时钟域。当在较低频率下运行时,它会有很多时序裕量,因此可以添加到设计中而不会影响时序收敛。

浙公网安备 33010602011771号

浙公网安备 33010602011771号