ZYNQ学习笔记

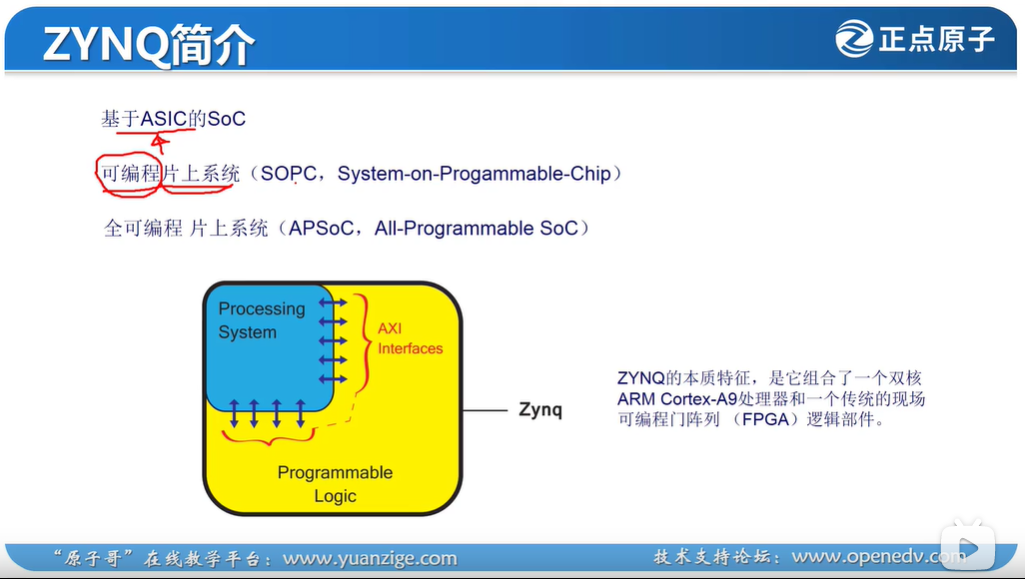

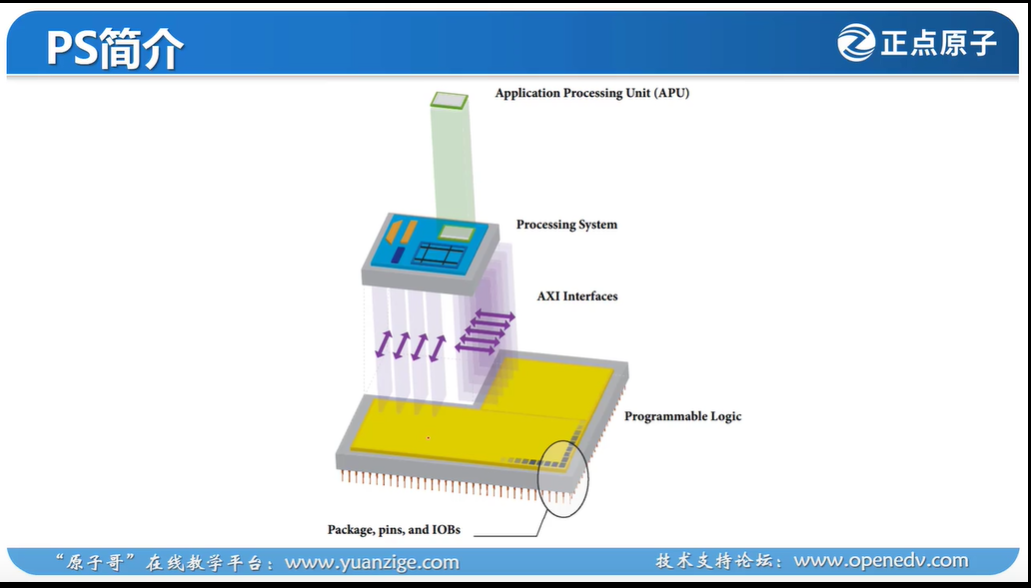

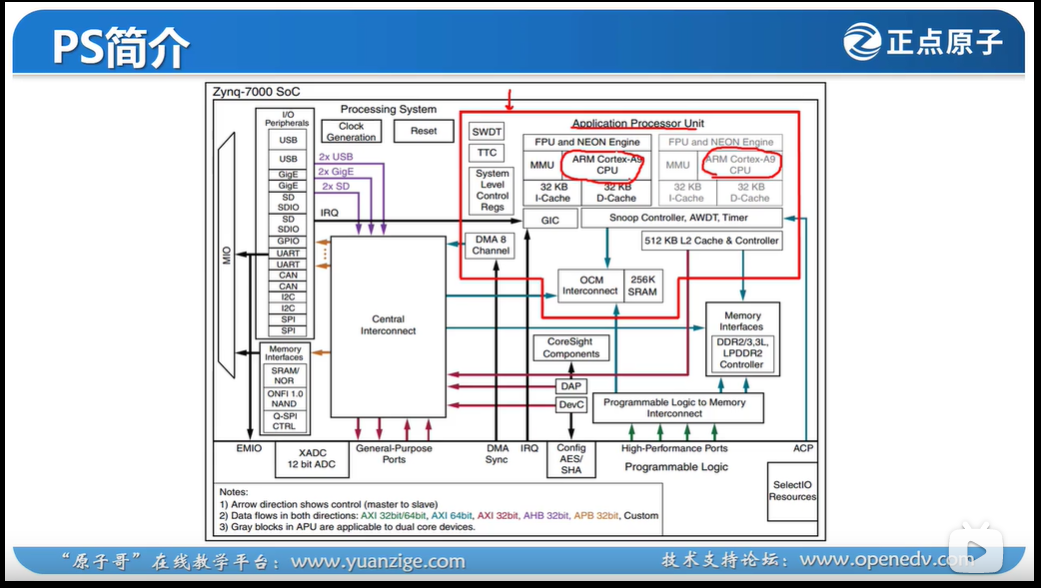

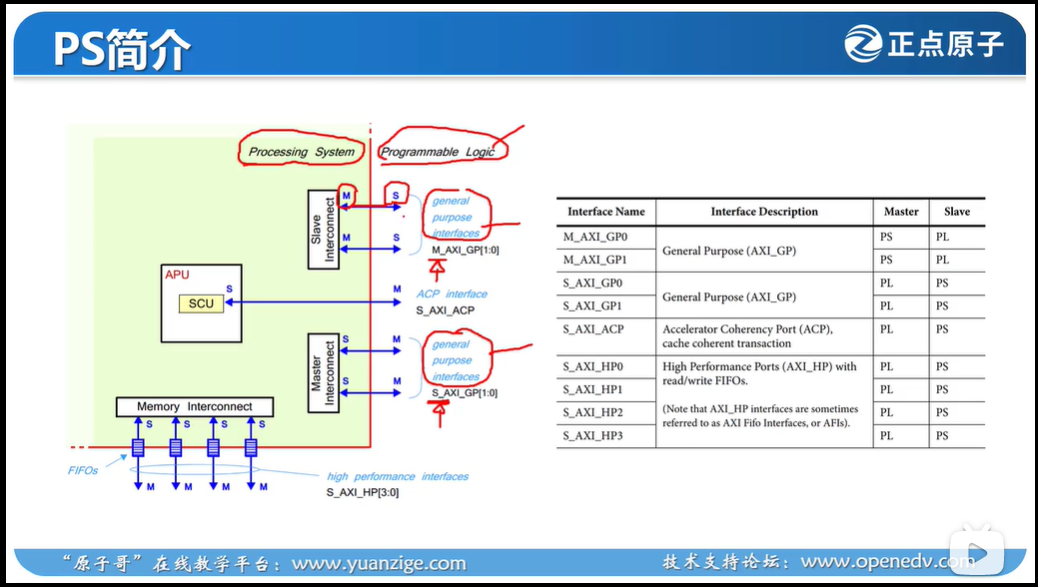

ZYNQ=PS+PL

PS:processing system 处理器系统

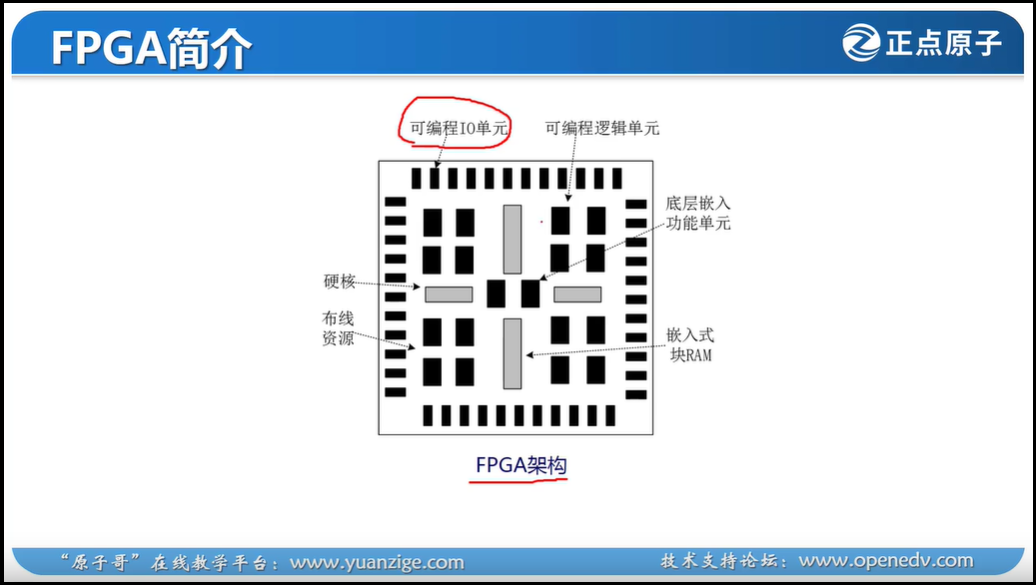

PL:programmable logic 即FPGA

cache:高速缓冲存储器

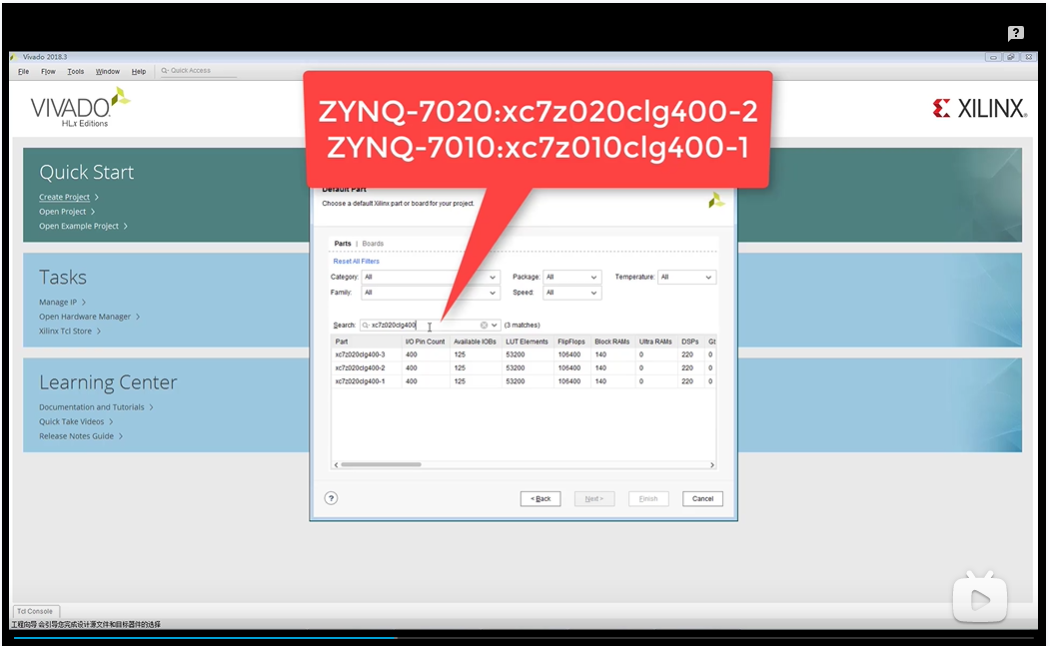

VIVADO软件可以看成是 ISE14.7 的升级版, 两者都是xilinx FPGA的IDE。 ISE已经停止更新了。

vivado2020.1及以后都叫做VITIS,功能更强大,包含了vivado.

Quartes是Altera(另一家FPGA厂商)的IDE,Altera已经被Intel收购。

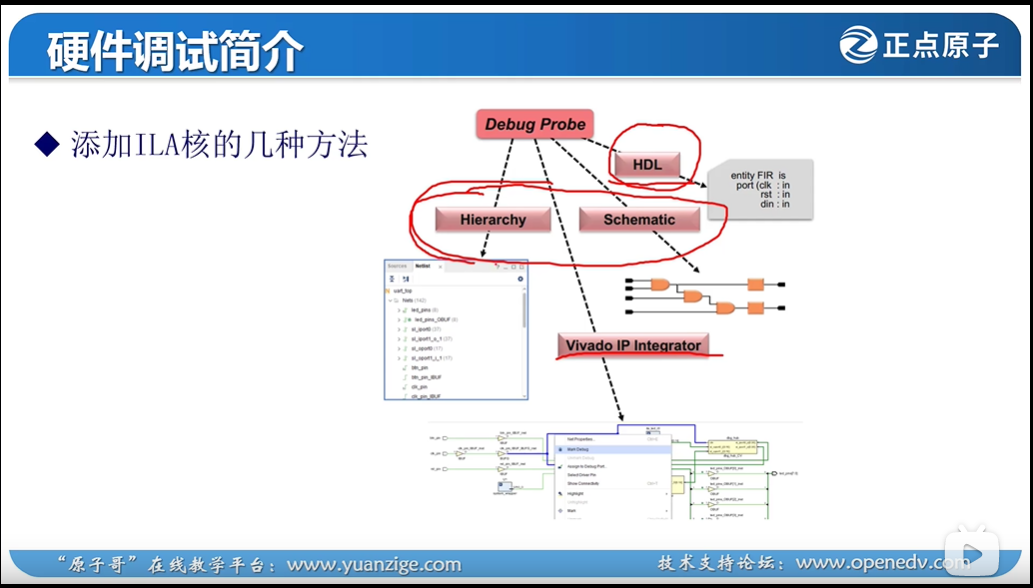

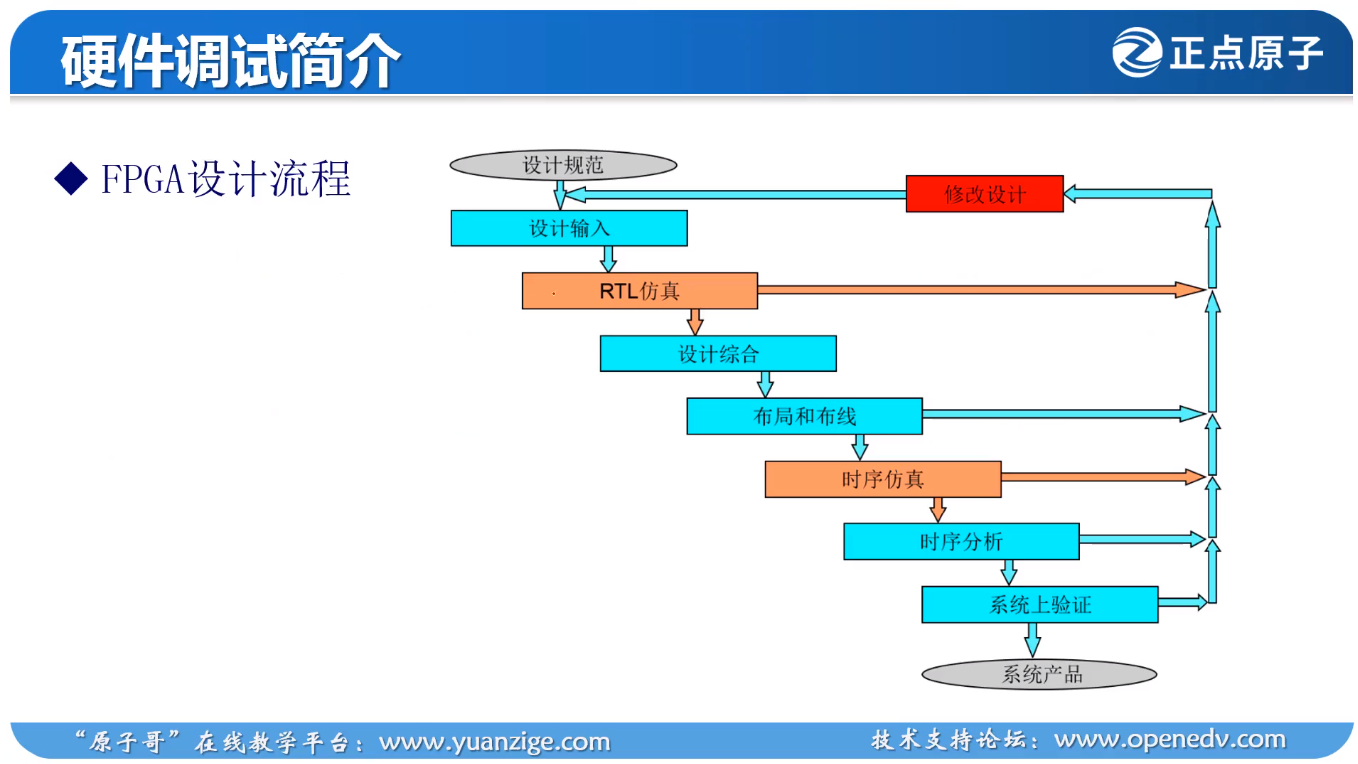

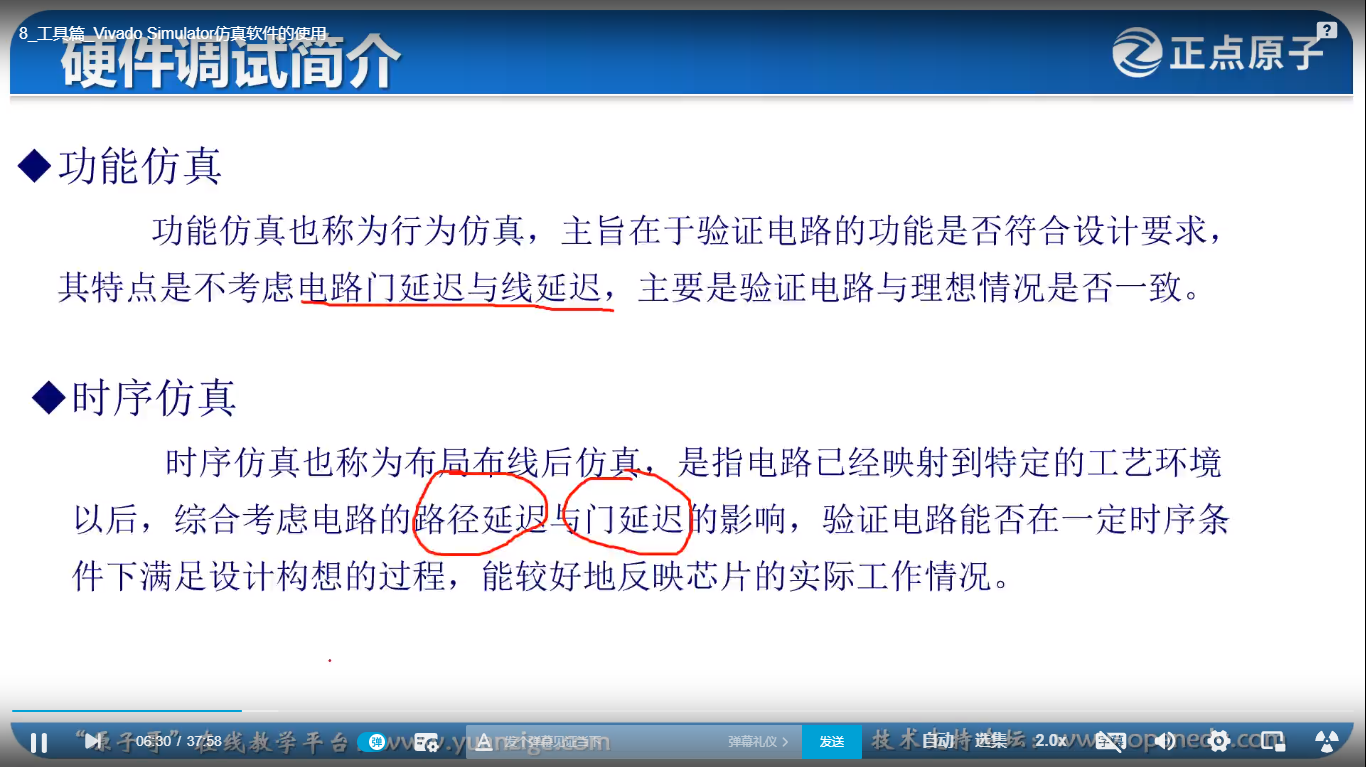

硬件调试:

ILA:逻辑分析器

hierarchy:等级

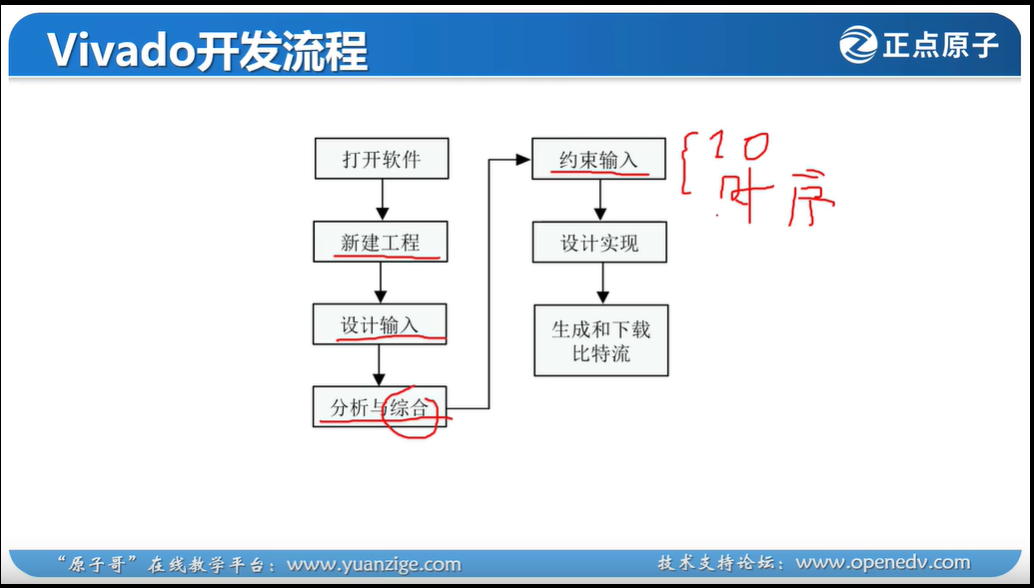

XXX.xpr ---VIVADO工程文件

XXX.xdc ---VIVADO约束文件

XXX.bit ---VIVADO比特流文件,可以下载进板子

PLD包括 CPLD和FPGA。

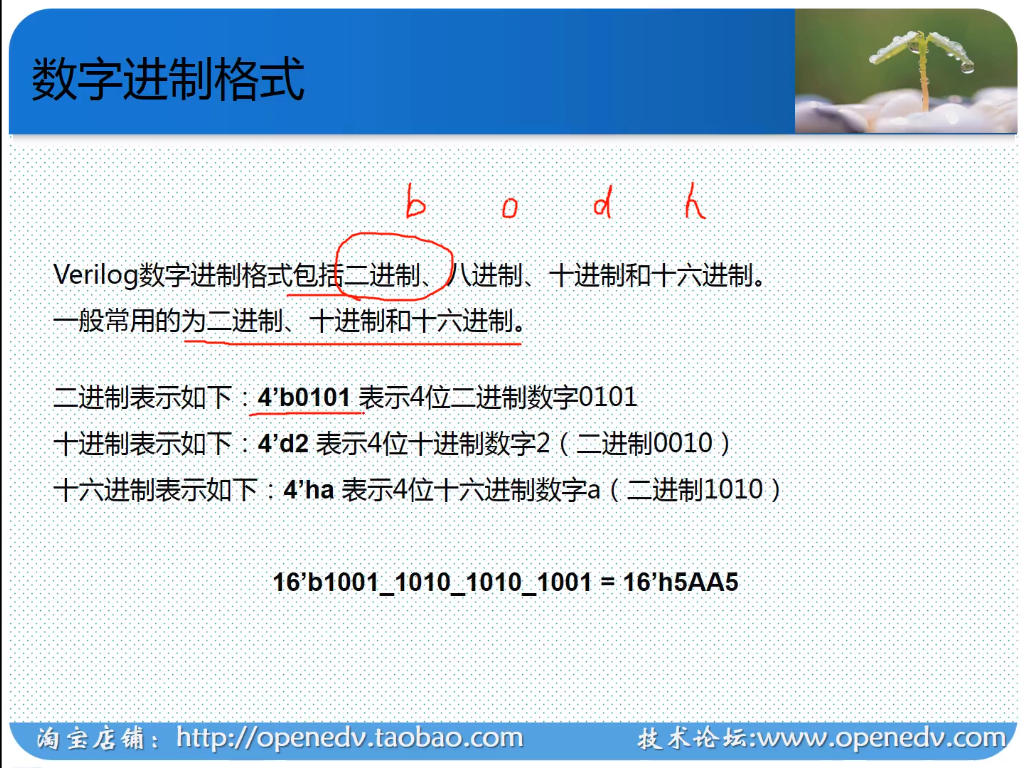

4为位宽,没有4,就默认32位宽。缺省为十进制,32位宽。32"d

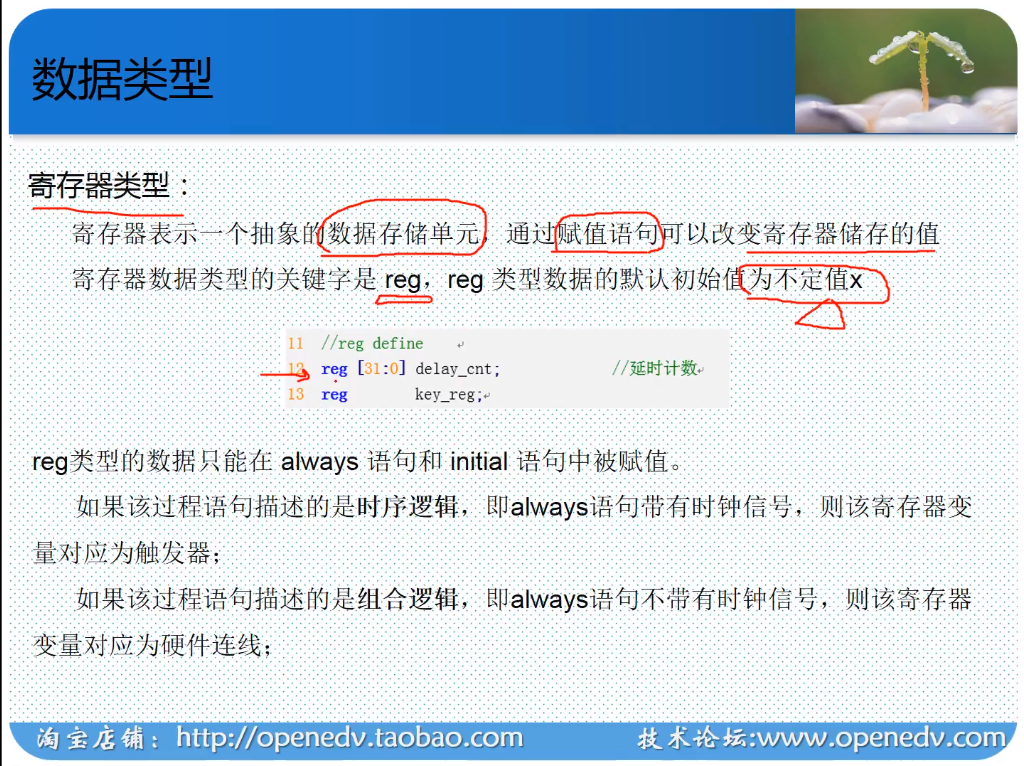

reg [31:0] delay_cnt; // [31:0]表示0到31位, 格式【高位:低位】 ,从低位到高位

wire:1位位宽

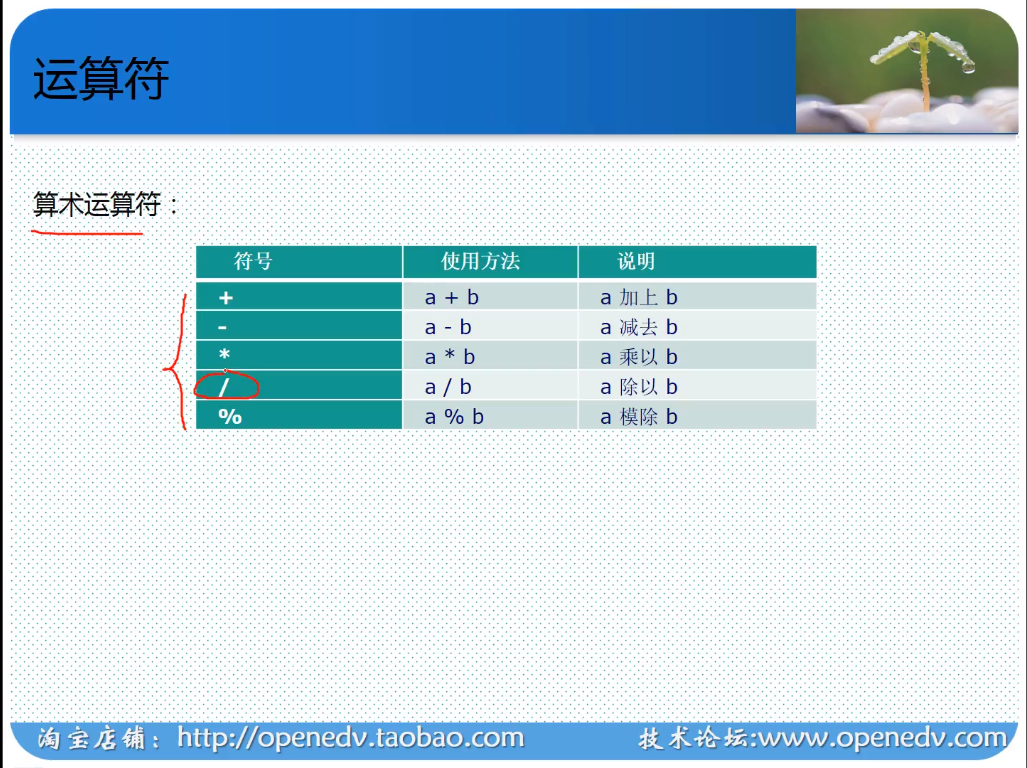

/:整除 %:取余

假设a,b各为8位,那么 拼接:a为高8位,b为低4位。

推荐左边的写法。

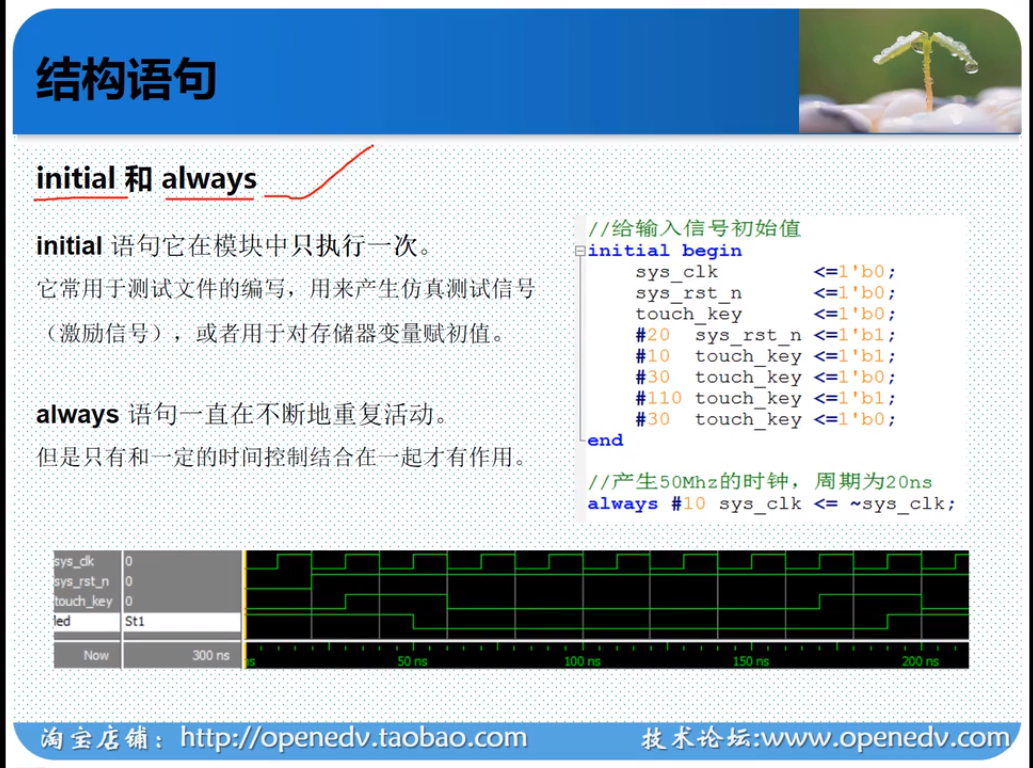

#表示延时 ; #10表示延时10个单位的时间 默认1ns/1ps ,1个单位为1ns,精度为1ps

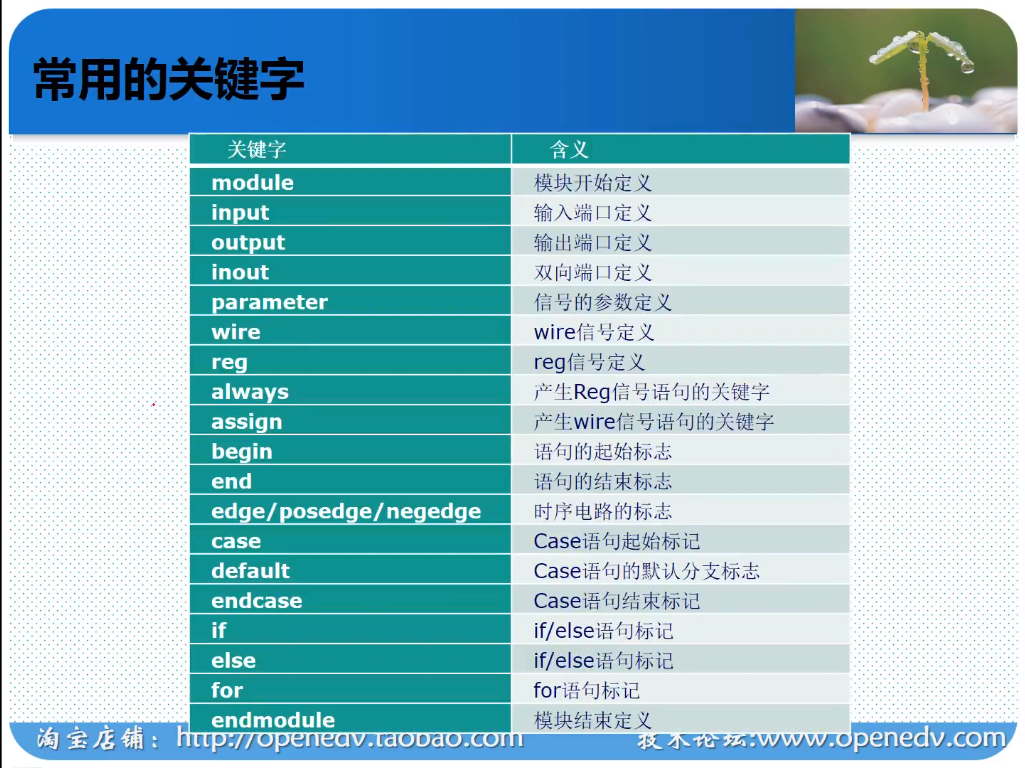

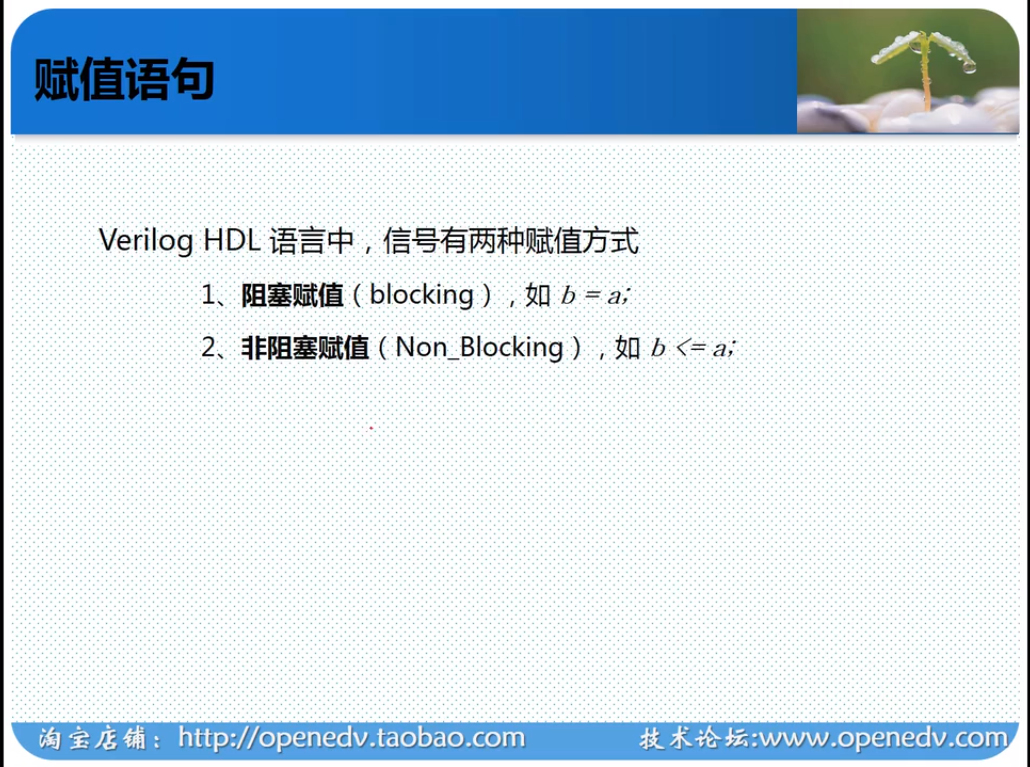

《= 赋值

RHS:right hand side 右手侧

LHS:left hand side 左手侧

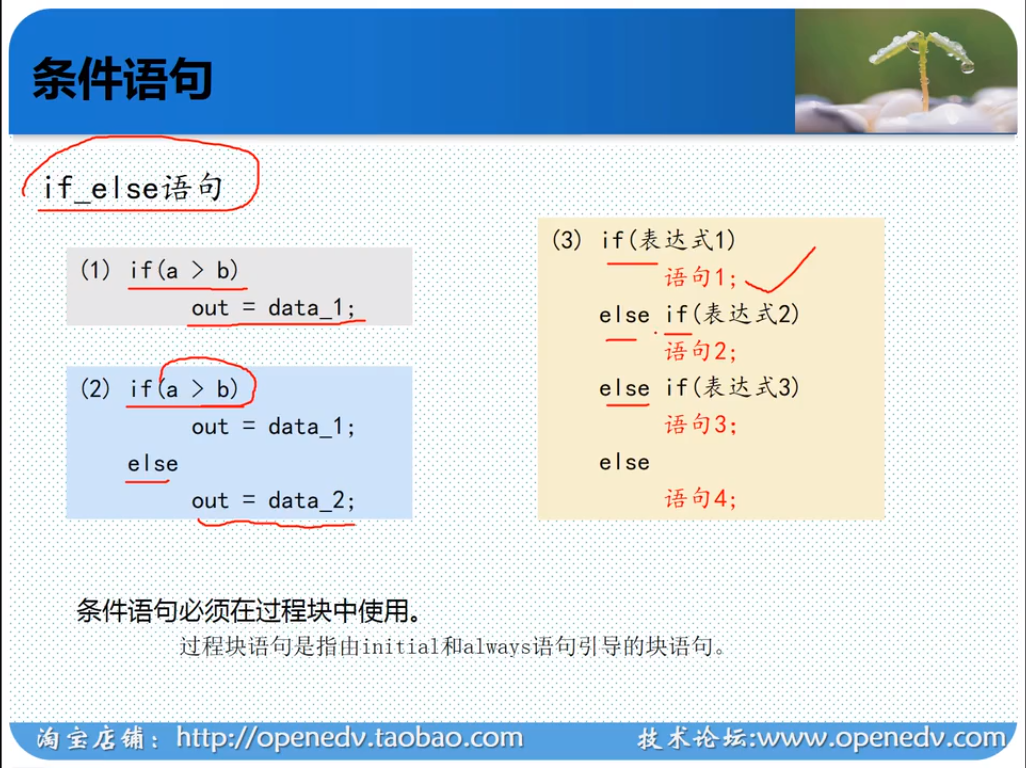

这里的begin...end相当于C语言里面的{ .... }大括号

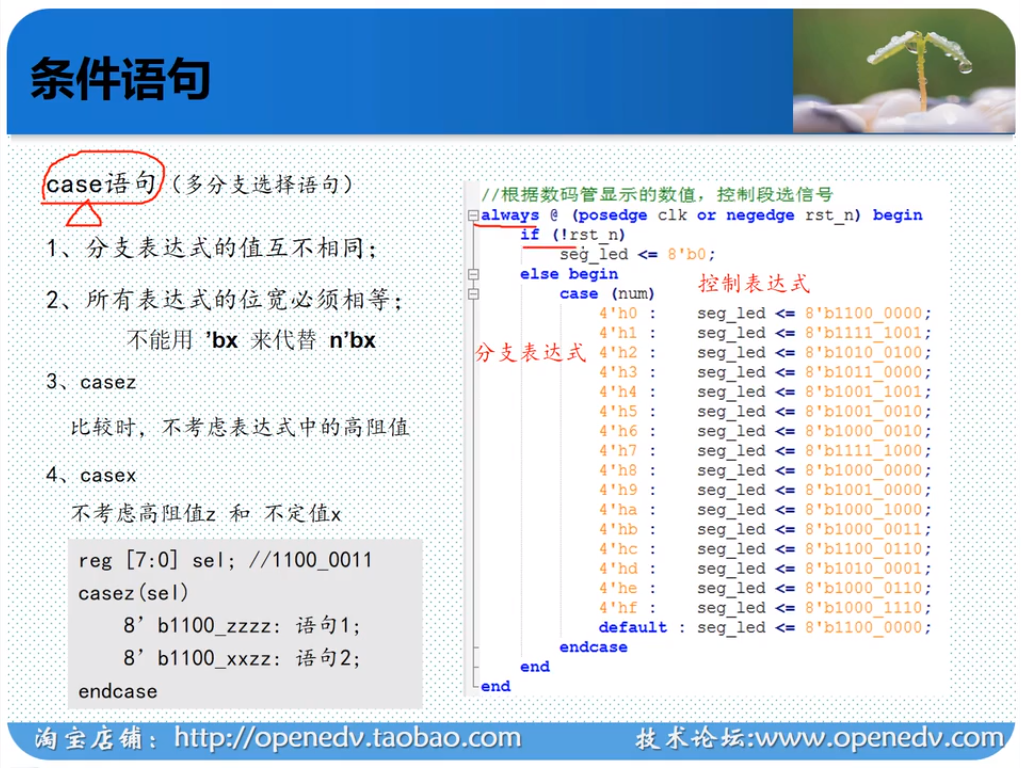

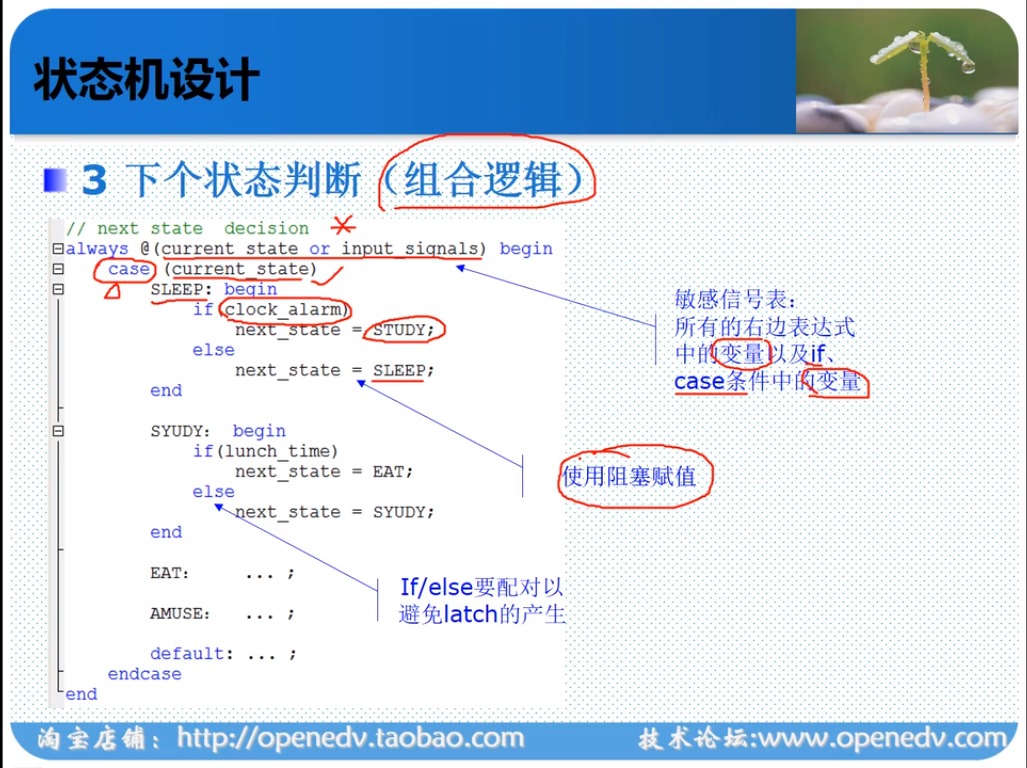

case....endcase 不用break

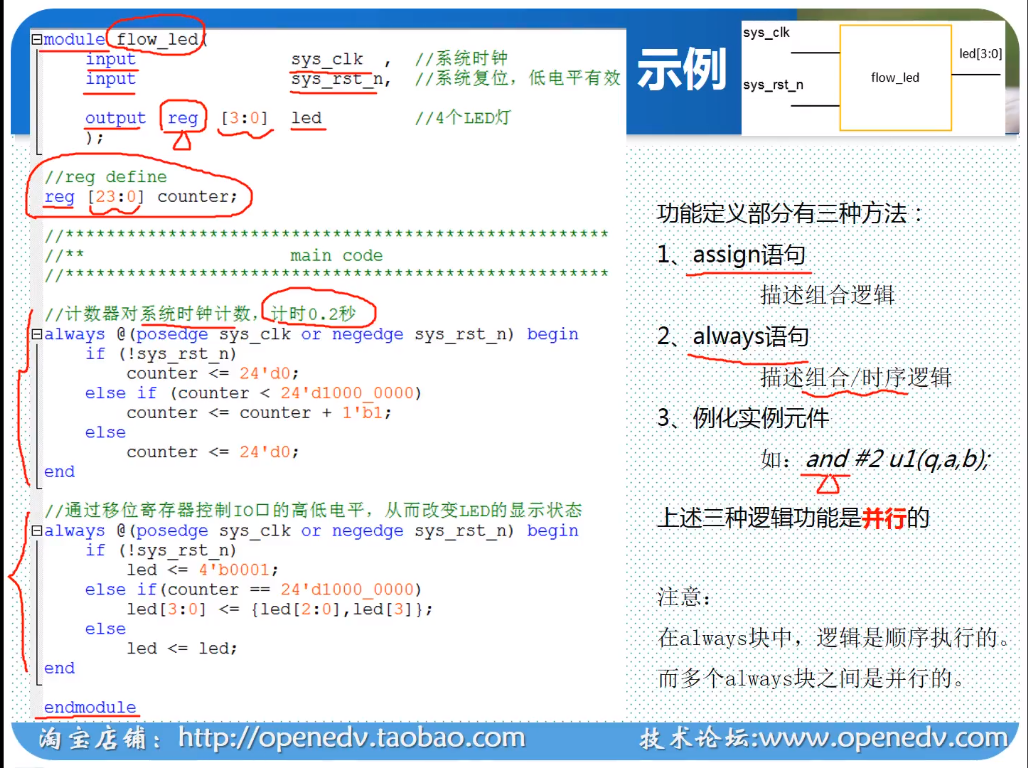

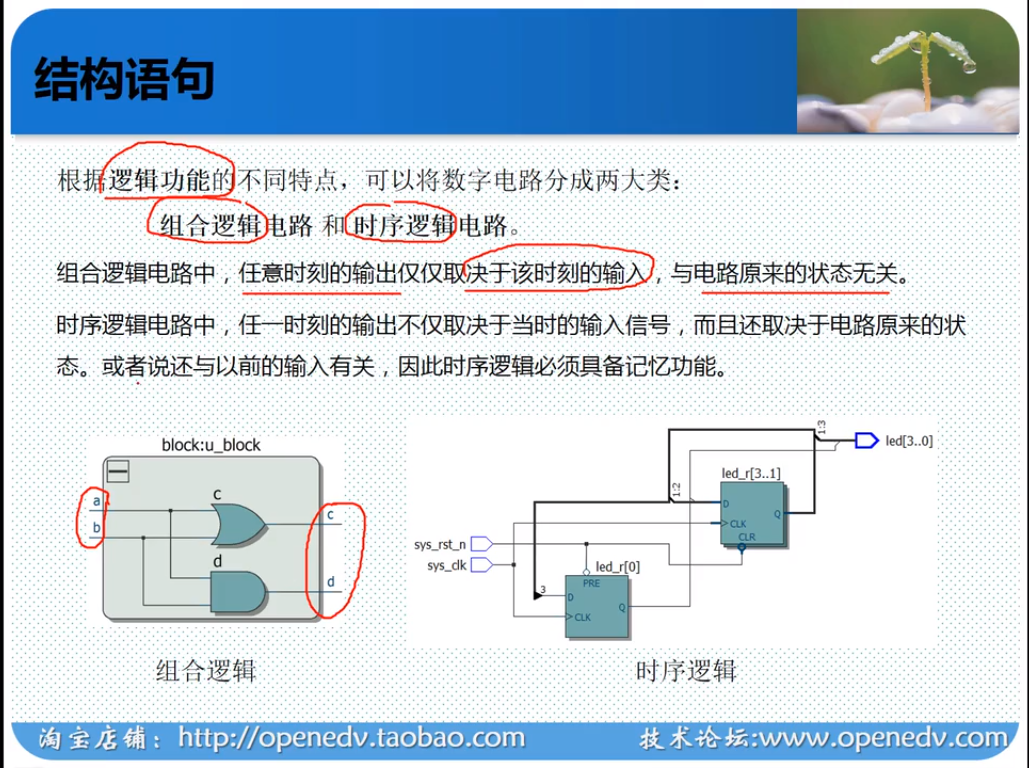

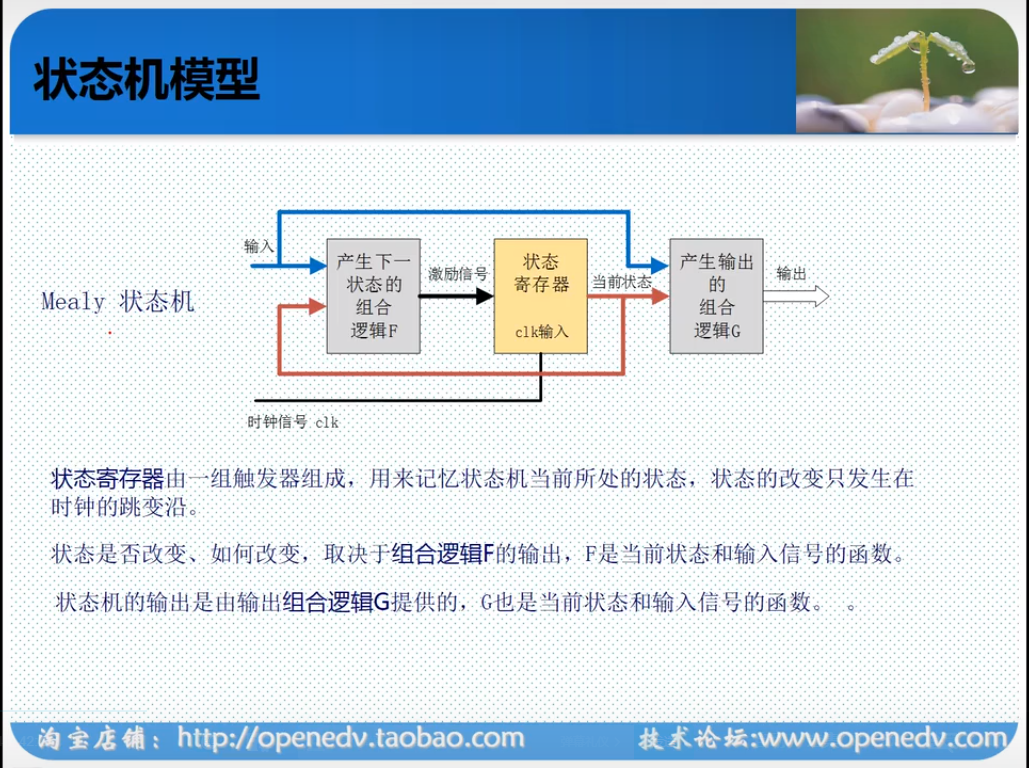

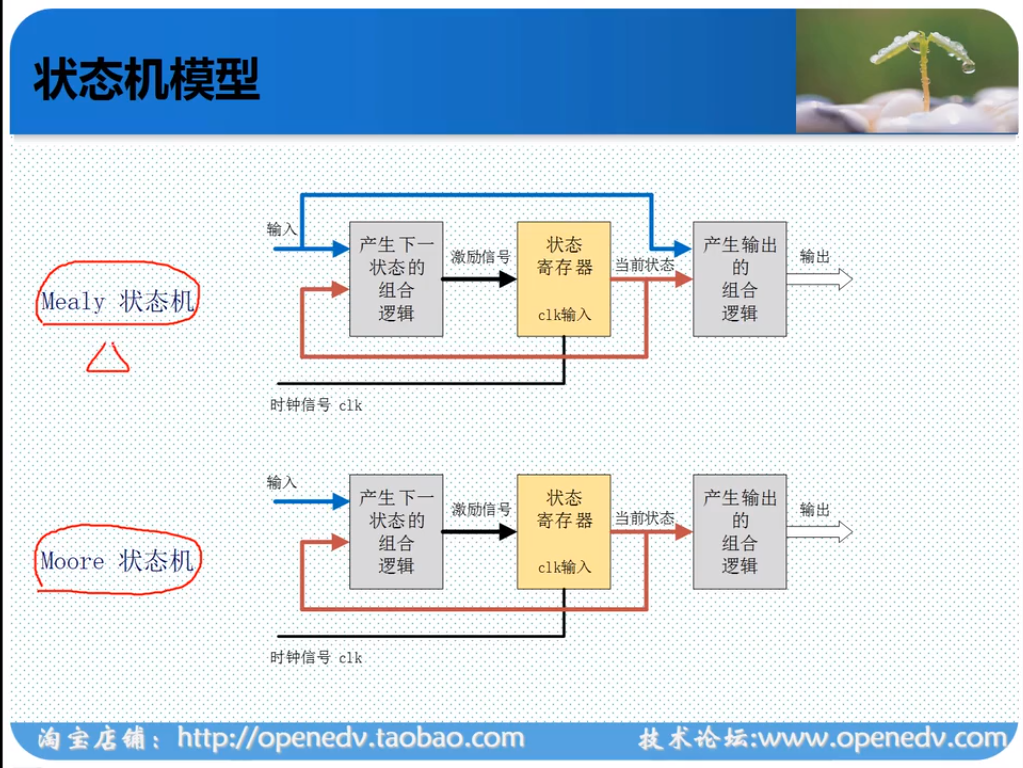

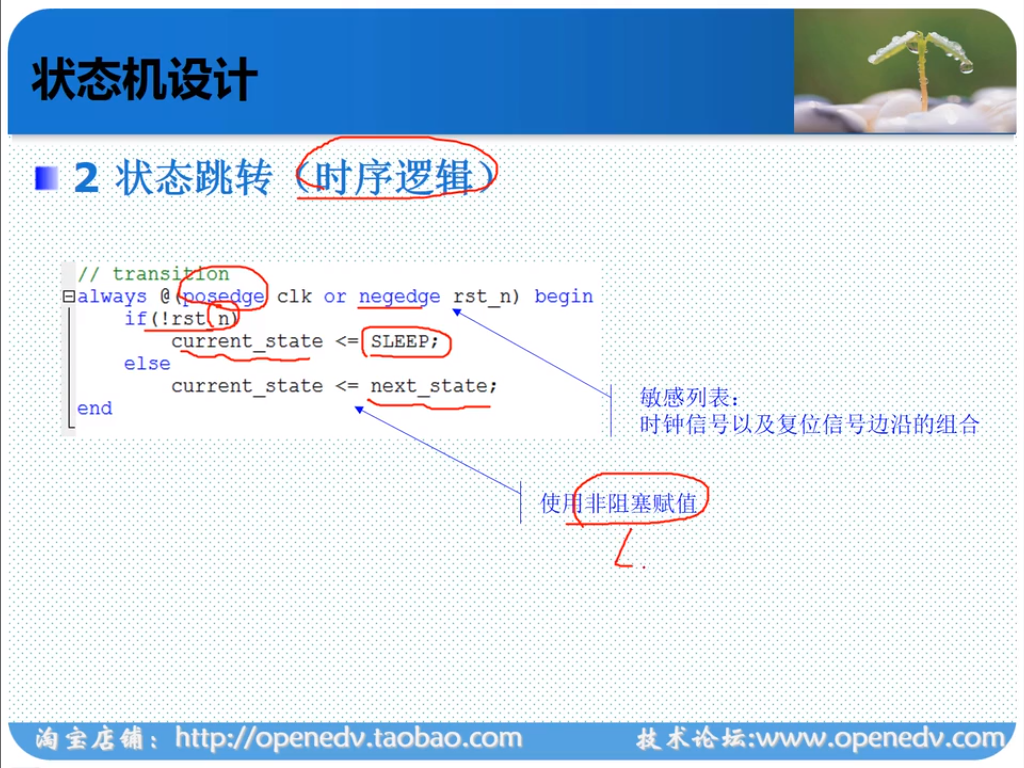

组合逻辑使用阻塞赋值,时序逻辑使用非阻塞赋值。

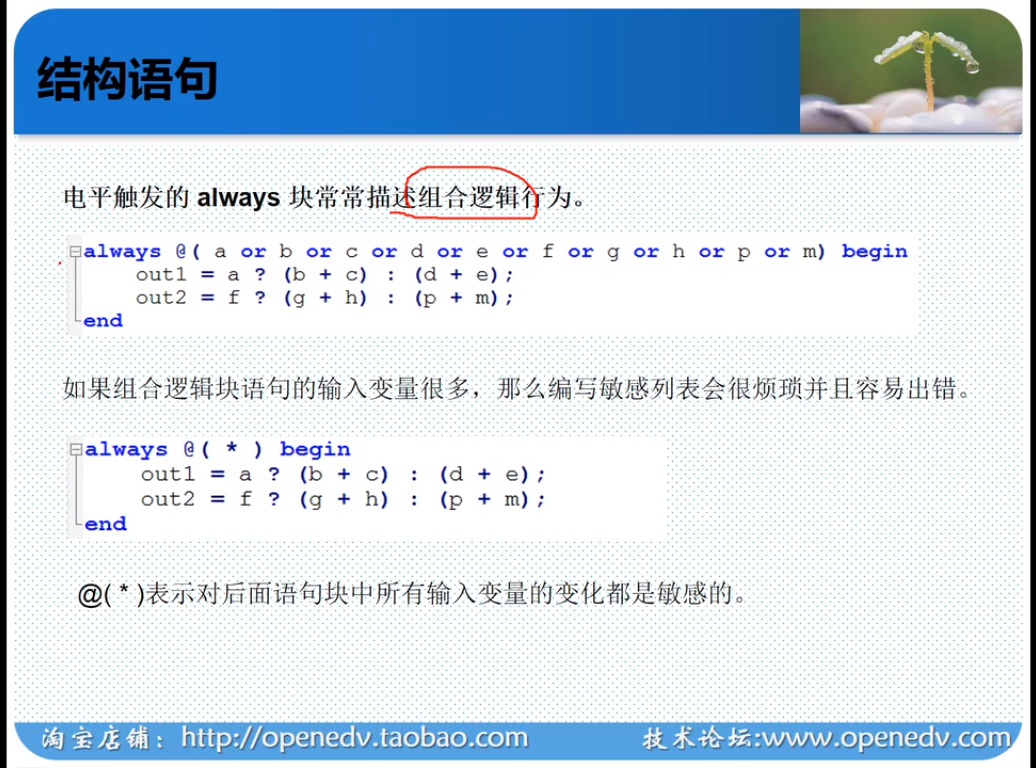

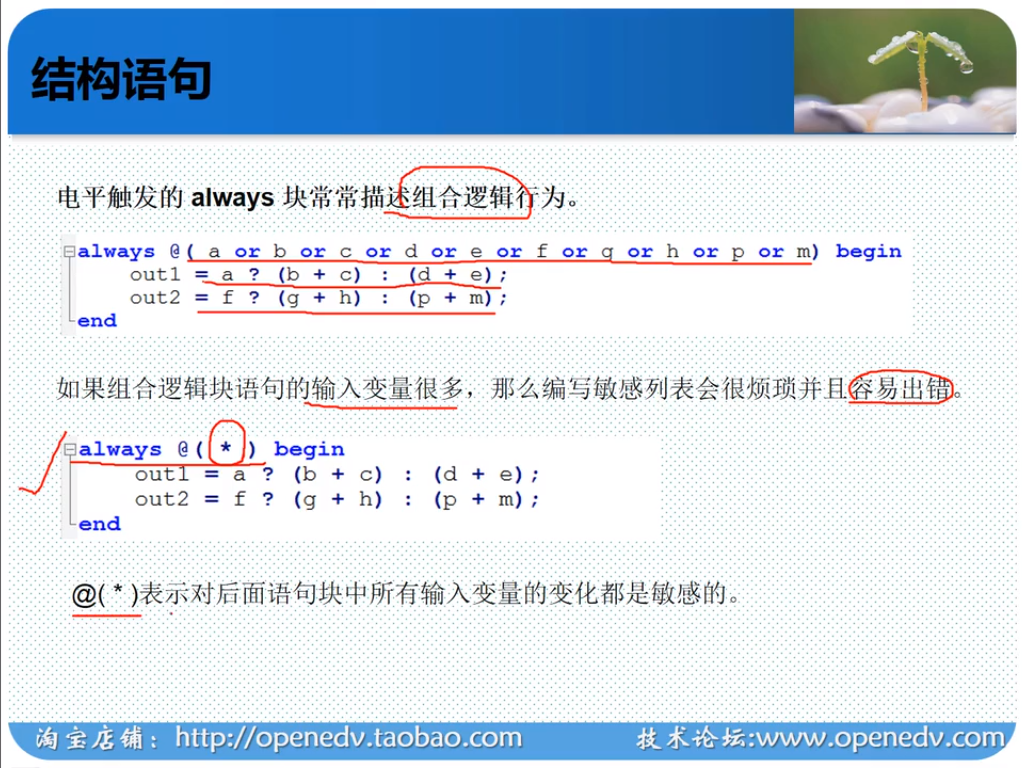

边沿触发的always通常描述时序逻辑;电平触发的always通常描述组合逻辑。

浙公网安备 33010602011771号

浙公网安备 33010602011771号