static ulong get_PLLCLK(int pllreg) { S3C24X0_CLOCK_POWER* const clk_power = S3C24X0_GetBase_CLOCK_POWER(); ulong r, m, p, s; if (pllreg == MPLL) r = clk_power->MPLLCON; else if (pllreg == UPLL) r = clk_power->UPLLCON; else hang(); m = ((r & 0xFF000) >> 12) + 8; p = ((r & 0x003F0) >> 4) + 2; s = r & 0x3; if(gd->bd->bi_arch_number == MACH_TYPE_SMDK2410) return((CONFIG_SYS_CLK_FREQ * m) / (p << s)); else { // return ((CONFIG_SYS_CLK_FREQ * m * 2)/(p<<s)); return (CONFIG_SYSPLL_CLK_FREQ/(p<<s))*m*2; } }

注意 这里面

return ((CONFIG_SYS_CLK_FREQ * m * 2)/(p<<s)); 这个会超过32位造成溢出 所以改成

return (CONFIG_SYSPLL_CLK_FREQ/(p<<s))*m*2;

流程:

1.首先执行的是uboot 文件夹最外层的makefile,编译make XXXX_Config 会在include/config 文件夹里面出现一个此平台的设置文件 可以剪裁此uboot 然后执行make all 会进行编译和连接。

2. 完成1 之后 请看CPU文件夹下面的start.S 这个文件的汇编程序会执行以下的功能:1. 关闭看门狗, 2 使能SDRAM 3. 代码重定位, 分配栈、全局变量、中断的空间。然后调用board文件夹下面的C文件 (board.c)里面会含有各种初始化的程序。

Makefile_Uboot => CPU.Start.S=>lib/arm=>start_armboot=>board/makefile=>board.c

注意include

以下是如何兼容2440的步骤:

1. 修改总的make file 使他能执行 make 100ask24x0_Config (<board_name>_config 这个名字可以随意起)

100ask24x0_config : unconfig

@$(MKCONFIG) $(@:_config=) arm arm920t 100ask24x0 NULL s3c24x0

2. 在board 目录下赋值smdk2410 改名字成100ask24x0 里面的c文件也改名成100ask24x0.c

3. 在include/config/smdk2410.h 复制一个叫100ask22X0.h其中里面是硬件的一些设置

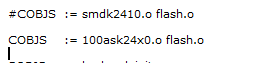

4. 在board/100ask24x0/Makefile 修改

5. 下面需要改变SDRAM的驱动程序 这部分程序是在lowlevel_init.S文件里面

6. 修改时钟

S3C2410 FCLK 运行的是200Mhz而在S3C2440上面运行的是400Mhz所以说我们的分频的比例应该从1:2:4 变成1:4:8 还将UPLL设置成为48Mhz 即UCLK为48Mhz

修改100ask24X0.c的board.c 函数

此外board_Init 函数需要更改

int board_init (void) { S3C24X0_CLOCK_POWER * const clk_power = S3C24X0_GetBase_CLOCK_POWER(); S3C24X0_GPIO * const gpio = S3C24X0_GetBase_GPIO(); /* set up the I/O ports */ gpio->GPACON = 0x007FFFFF; gpio->GPBCON = 0x00044555; gpio->GPBUP = 0x000007FF; gpio->GPCCON = 0xAAAAAAAA; gpio->GPCUP = 0x0000FFFF; gpio->GPDCON = 0xAAAAAAAA; gpio->GPDUP = 0x0000FFFF; gpio->GPECON = 0xAAAAAAAA; gpio->GPEUP = 0x0000FFFF; gpio->GPFCON = 0x000055AA; gpio->GPFUP = 0x000000FF; gpio->GPGCON = 0xFF95FFBA; gpio->GPGUP = 0x0000FFFF; gpio->GPHCON = 0x002AFAAA; gpio->GPHUP = 0x000007FF; if((gpio->GSTATUS1 == 0x32410000)||(gpio->GSTATUS1 == 0x32410002)) { clk_power->CLKDIVN = S3C2410_CLKDIV; _asm_( "mrc p15, 0, r1, c1, c0, 0\n" "orr r1, r1, #0xc0000000\n" "mcr p15, 0, r1, c1, c0, 0 \n" :::"r1" ); clk_power->LOCKTIME = 0xFFFFFFFF; clk_power->MPLLCON = S3C2410_MPLL_200MHZ; delay(4000); clk_power->UPLLCON = S3C2410_UPLL_48MHZ; delay(8000); /* arch number of SMDK2410-Board */ gd->bd->bi_arch_number = MACH_TYPE_SMDK2410; } else { clk_power->CLKDIVN = S3C2440_CLKDIV; _asm_( "mrc p15, 0, r1, c1, c0, 0\n" "orr r1, r1, #0xc0000000\n" "mcr p15, 0, r1, c1, c0, 0 \n" :::"r1" ); clk_power->LOCKTIME = 0xFFFFFFFF; clk_power->MPLLCON = S3C2440_MPLL_400MHZ; delay(4000); clk_power->UPLLCON = S3C2440_UPLL_48MHZ; delay(8000); gd->bd->bi_arch_number = MACH_TYPE_S3C2440; } /* adress of boot parameters */ gd->bd->bi_boot_params = 0x30000100; icache_enable(); dcache_enable(); return 0; }

6. 下面是设置波特率 好让串口工作 其文件在start_armboot 函数中 这个函数会调用serial_init 函数 与这个函数相关的还有get_HCLK get_PLLCLK 这些函数在cpu/arm920t.s3c24x0/speed.c中

/*for S2c2440*/ #define S3C2440_CLKDIVN_PDIVN (1<<0) #define S3C2440_CLKDIVN_HDIVN_MASK (3<<1) #define S3C2440_CLKDIVN_HDIVN_1 (0<<1) #define S3C2440_CLKDIVN_HDIVN_2 (1<<1) #define S3C2440_CLKDIVN_HDIVN_4_8 (2<<1) #define S3C2440_CLKDIVN_HDIVN_3_6 (3<<1) #define S3C2440_CLKDIV_UCLK (1<<3) #define S3C2440_CAMDIVN_CAMCLK_MASK (0XF<<0) #define S3C2440_CAMDIVN_CAMCLK_SEL (1<<4) #define S3C2440_CAMDIVN_HCLK3_HALF (1<<8) #define S3C2440_CAMDIVN_HCLK4_HALF (1<<9) #define S3C2440_CAMDIVN_DVSEN (1<<12) /* return HCLK frequency */ ulong get_HCLK(void) { S3C24X0_CLOCK_POWER * const clk_power = S3C24X0_GetBase_CLOCK_POWER(); unsigned long clkdiv; unsigned long camdiv; int hdiv = 1; if(gd->bd->bi_arch_number == MACH_TYPE_SMDK2410) return((clk_power->CLKDIVN & 0x2) ? get_FCLK()/2 : get_FCLK()); else { clkdiv = clk_power->CLKDIVN; camdiv = clk_power->CAMDIVN; switch(clkdiv & S3C2440_CLKDIVN_HDIVN_MASK) { case S3C2440_CLKDIVN_HDIVN_1: hdiv = 1; break; case S3C2440_CLKDIVN_HDIVN_2: hdiv = 2; break; case S3C2440_CLKDIVN_HDIVN_4_8: hdiv = (camdiv & S3C2440_CAMDIVN_HCLK4_HALF) ? 8 : 4; break; case S3C2440_CLKDIVN_HDIVN_3_6: hdiv = (camdiv & S3C2440_CAMDIVN_HCLK3_HALF)? 6 : 3; break; } return get_FCLK()/hdiv; } } /* return PCLK frequency */ ulong get_PCLK(void) { S3C24X0_CLOCK_POWER * const clk_power = S3C24X0_GetBase_CLOCK_POWER(); unsigned long clkdiv; unsigned long camdiv; int hdiv = 1; if(gd->bd->bi_arch_number == MACH_TYPE_SMDK2410) return((clk_power->CLKDIVN & 0x1) ? get_HCLK()/2 : get_HCLK()); else { clkdiv = clk_power->CLKDIVN; clkdiv = clk_power->CAMDIVN; switch (clkdiv & S3C2440_CLKDIVN_HDIVN_MASK) { case S3C2440_CLKDIVN_HDIVN_1: hdiv = 1; break; case S3C2440_CLKDIVN_HDIVN_2: hdiv = 2; break; case S3C2440_CLKDIVN_HDIVN_4_8: hdiv = (camdiv & S3C2440_CAMDIVN_HCLK4_HALF)? 8 : 4; break; case S3C2440_CLKDIVN_HDIVN_3_6: hdiv = (camdiv & S3C2440_CAMDIVN_HCLK4_HALF)? 6 : 3; break; } return get_FCLK()/hdiv/((clkdiv & S3C2440_CLKDIVN_PDIVN)? 2 : 1); } }

里面这个代码改为 hdiv = (camdiv & S3C2440_CAMDIVN_HCLK3_HALF)? 6 : 3;

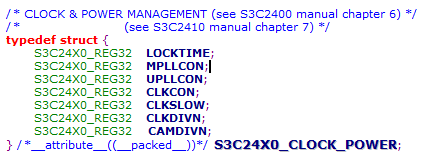

注意CAMDIVN里面在clk_power 里面没有定义 所以需要在include ( S3C24x0.h)中找到重新加上去

此时uboot 第一阶段结束

第一阶段完成的事情:

1. 在总Makefile里面 设置 make config

2. 在分Makefile里面更改 编译的文件

3. board.c 文件里面更改时钟

4. 在speed文件里面更改给USART的时钟

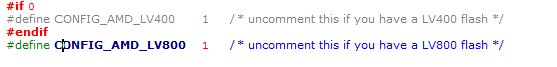

第二阶段:选择nor flash 我们使用的板子是支持AM29LV800 而默认是支持AM29LV800 所以说还要更改config 文件

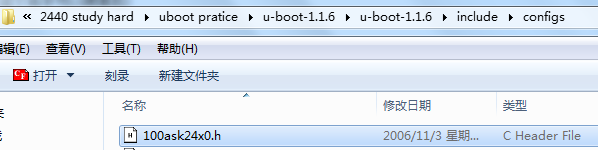

在\include\configs 里面

我去验证第二阶段是否正确,之后会更新后面的过程 到现在为止基本上u-boot移植完成 但是只是支持nor flash

后面将加入nand flash的内容