基于ZCU104的PS和PL数据交互例程(四):vivado中制作Block Design

1.设计架构

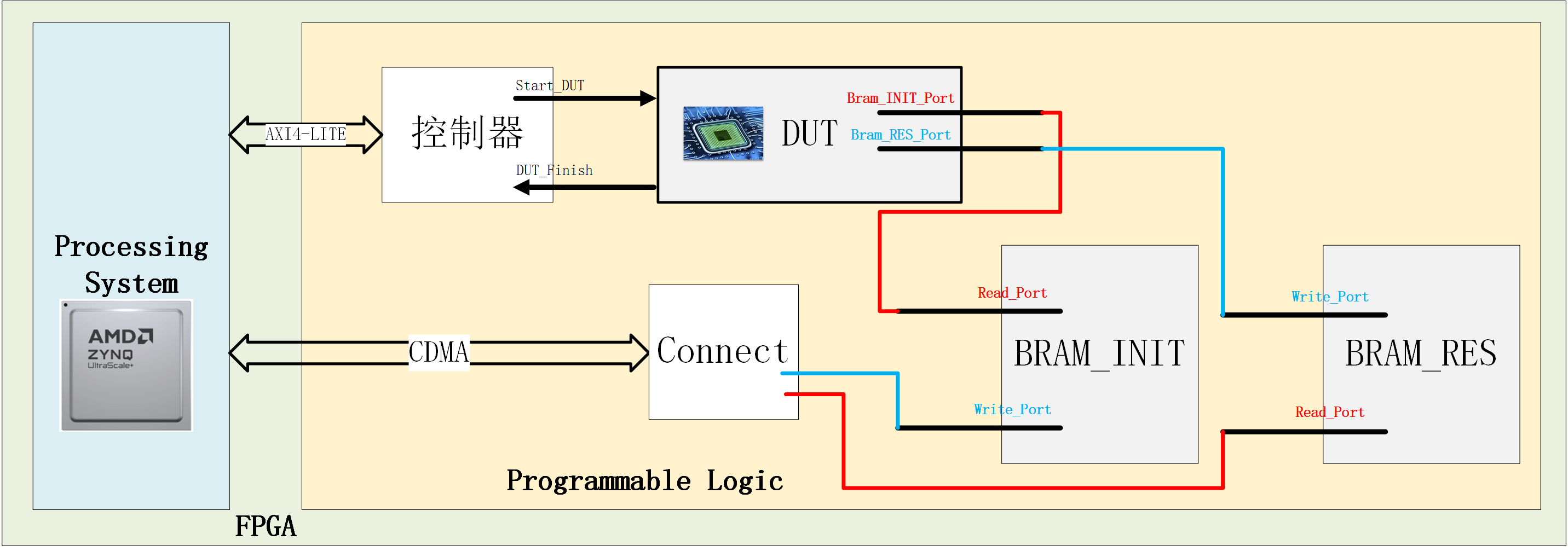

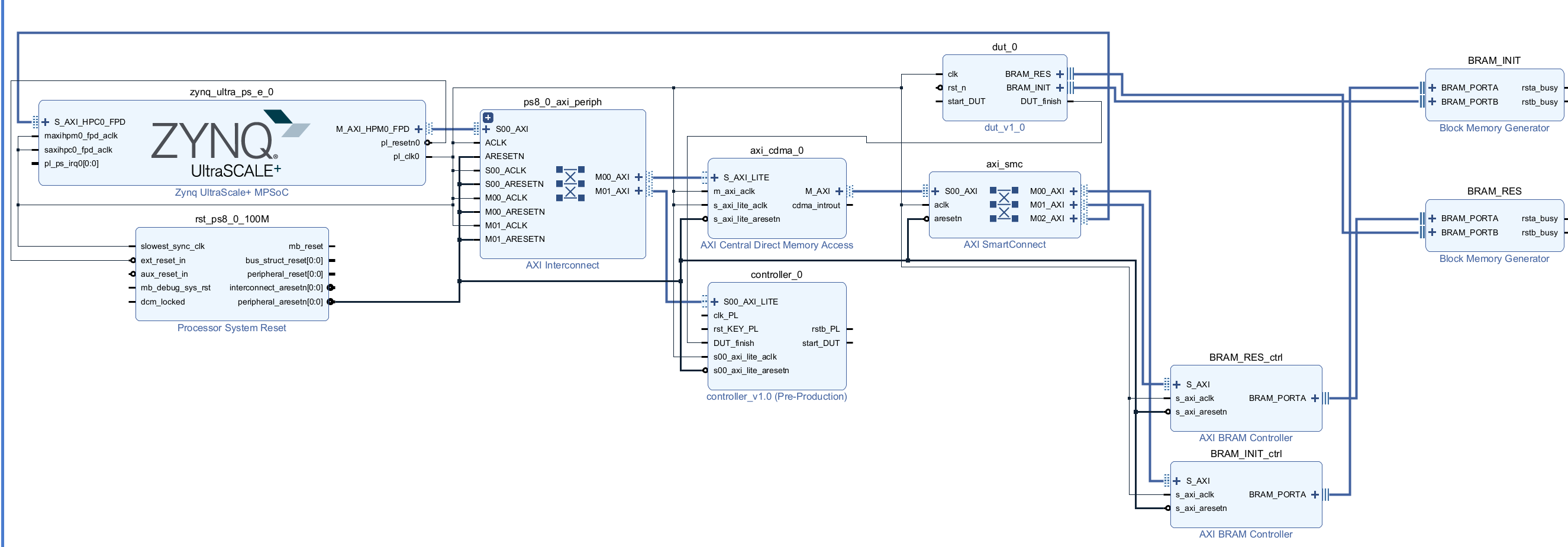

本次工程的架构设计思路如下

-

PS与PL交互数据总共分为两类,第一类是控制信号,第二类是数据信号。这里第一类控制信号走AXI4-LITE,第二类数据信息走CDMA

-

整体数据流程

-

PS端开始任务后,首先通过CDMA把初始数据送到BRAM_INIT

-

初始数据传输完成后,PS端通过AXI4-LITE给控制器发送初始数据加载完成信号

-

拿到PS给的初始数据完成信号后,控制器发送Start_DUT信号给DUT

-

DUT通过BRAM_INIT_Port读取BRAM_INIT中的数据(这里按照自己DUT的逻辑读取即可)

-

DUT读取完数据后,开始计算

-

DUT计算完成后,把结果数据通过BRAM_RES_Port写到BRAM-RES中

-

DUT发送DUT_Finish信号给控制器

-

控制器通过AXI4-LITE发送PL处理结束信号

-

PS端拿到PL处理结束信号后,通过CDMA把结果数据从BRAM_RES中读走

-

完成一次交互逻辑,后续重复操作

-

2.vivado中BD设计

参考block design的设计流程,这里给出完成的工程

封装IP的详细流程见另外两篇博客

基于ZCU104的PS和PL数据交互例程(二):vivado中封装现有工程成IP - 水流shuiliu - 博客园 (cnblogs.com)

基于ZCU104的PS和PL数据交互例程(三):vivado中创建IP - 水流shuiliu - 博客园 (cnblogs.com)

新建工程之后,选择zcu104板卡

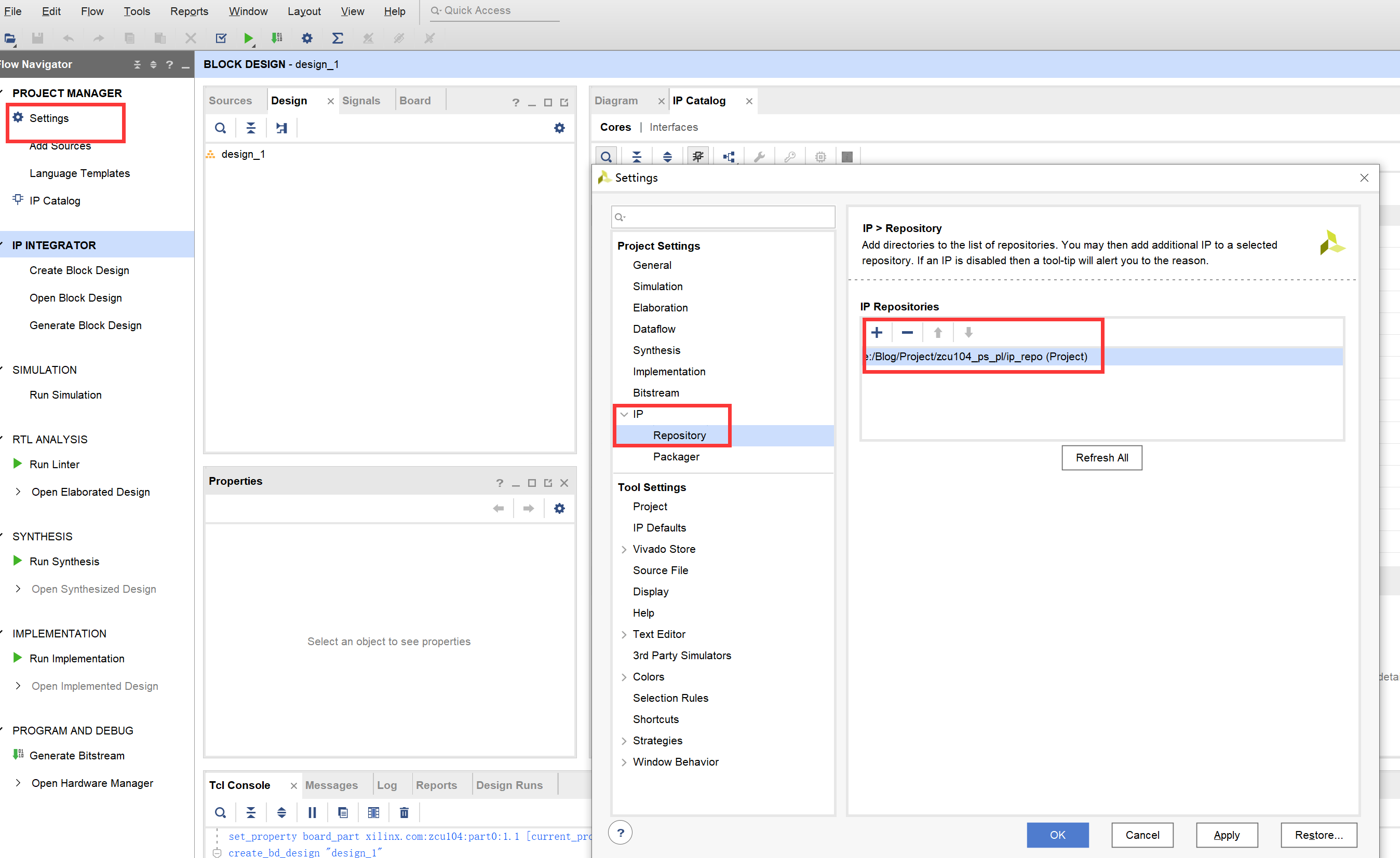

点击Settings把准备好的IP路径加入进来

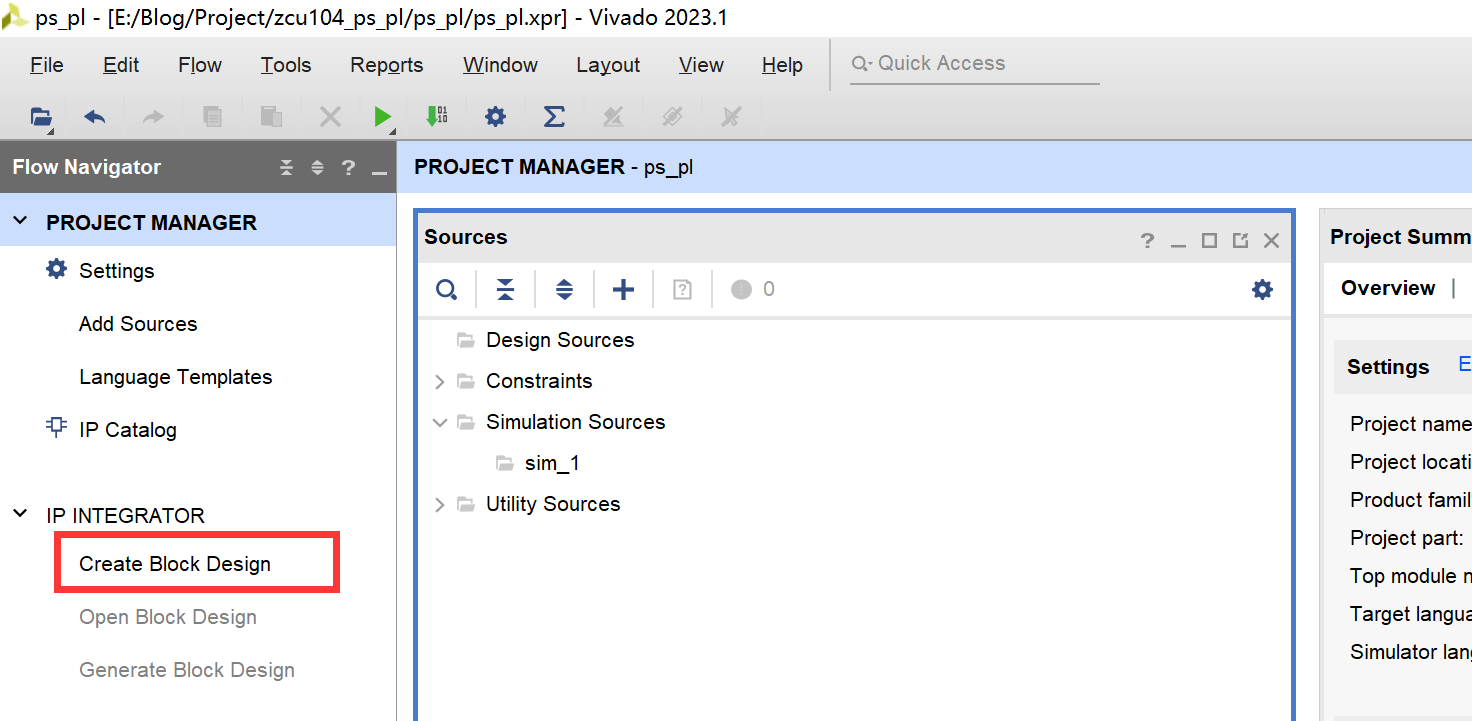

点击新建block design

配置PS的IP

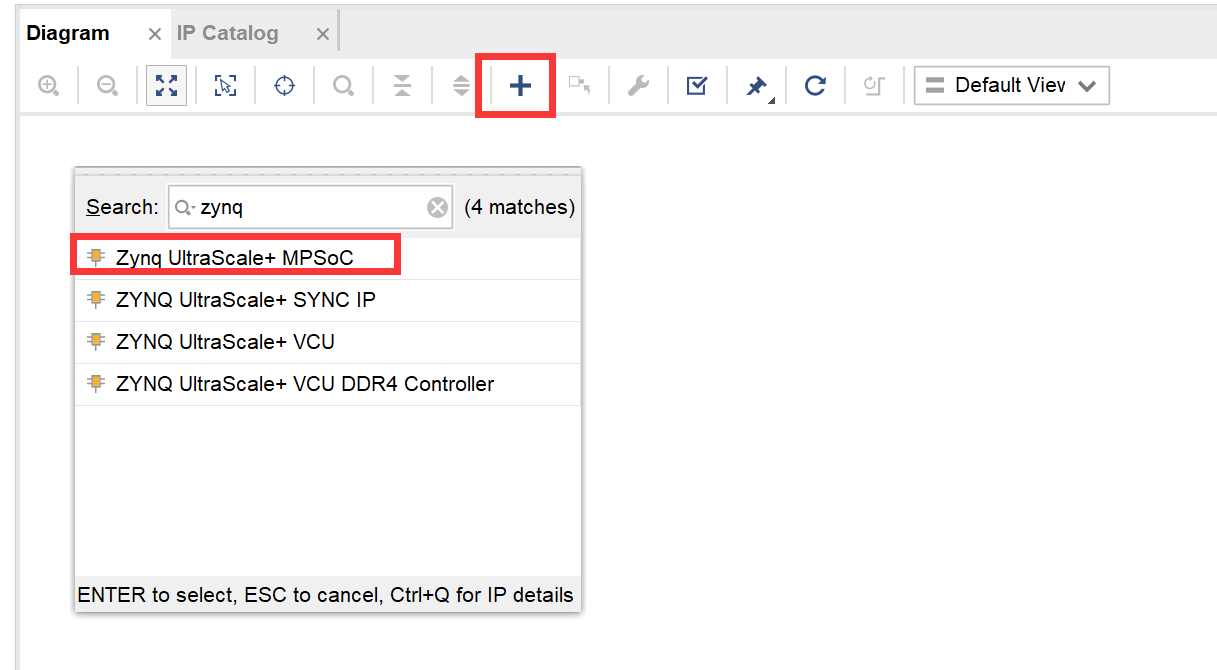

然后加入PS端的IP

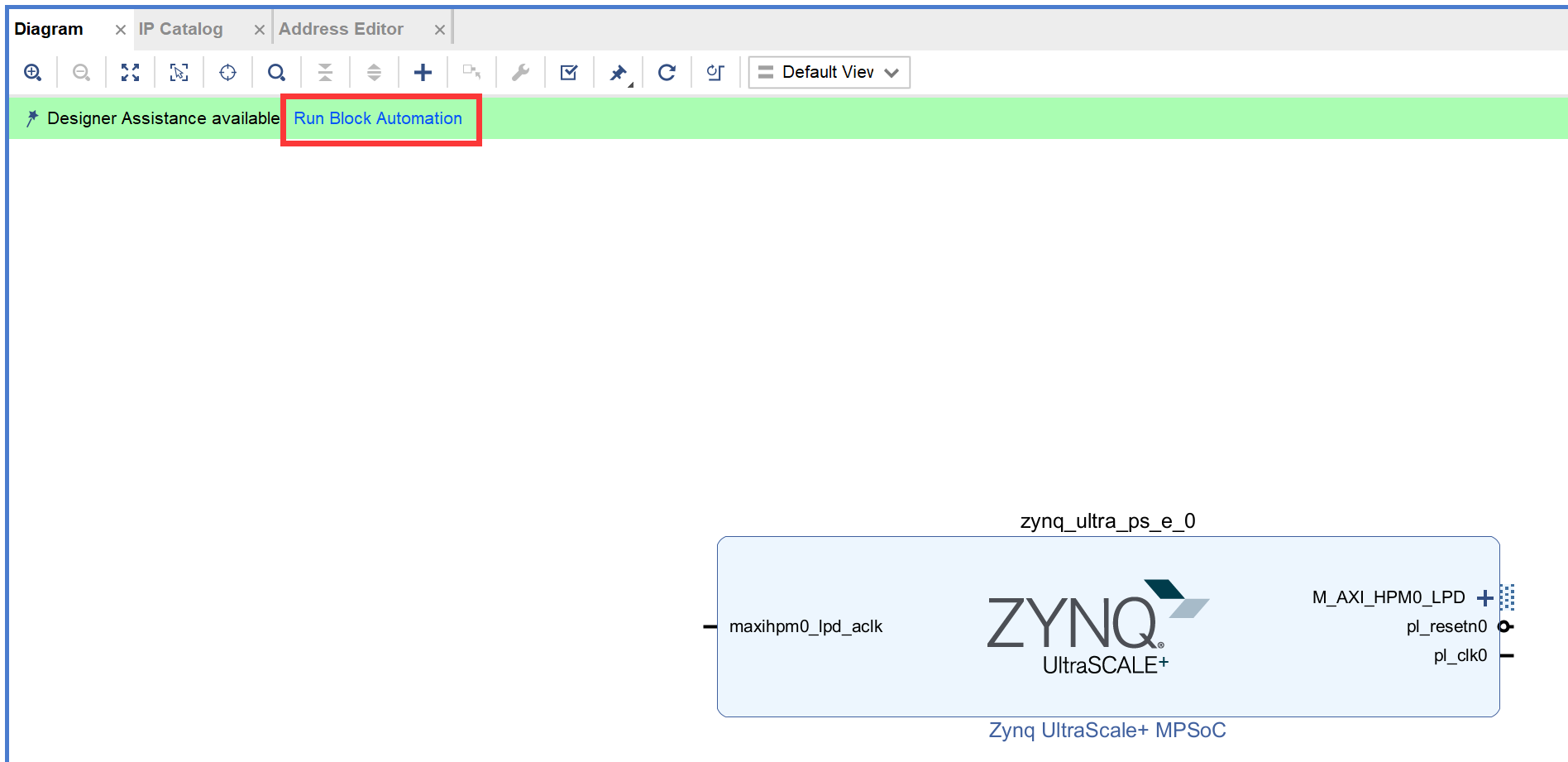

点击Run Block Automation,会自动配置PS端

然后双击PS端,进行特殊配置

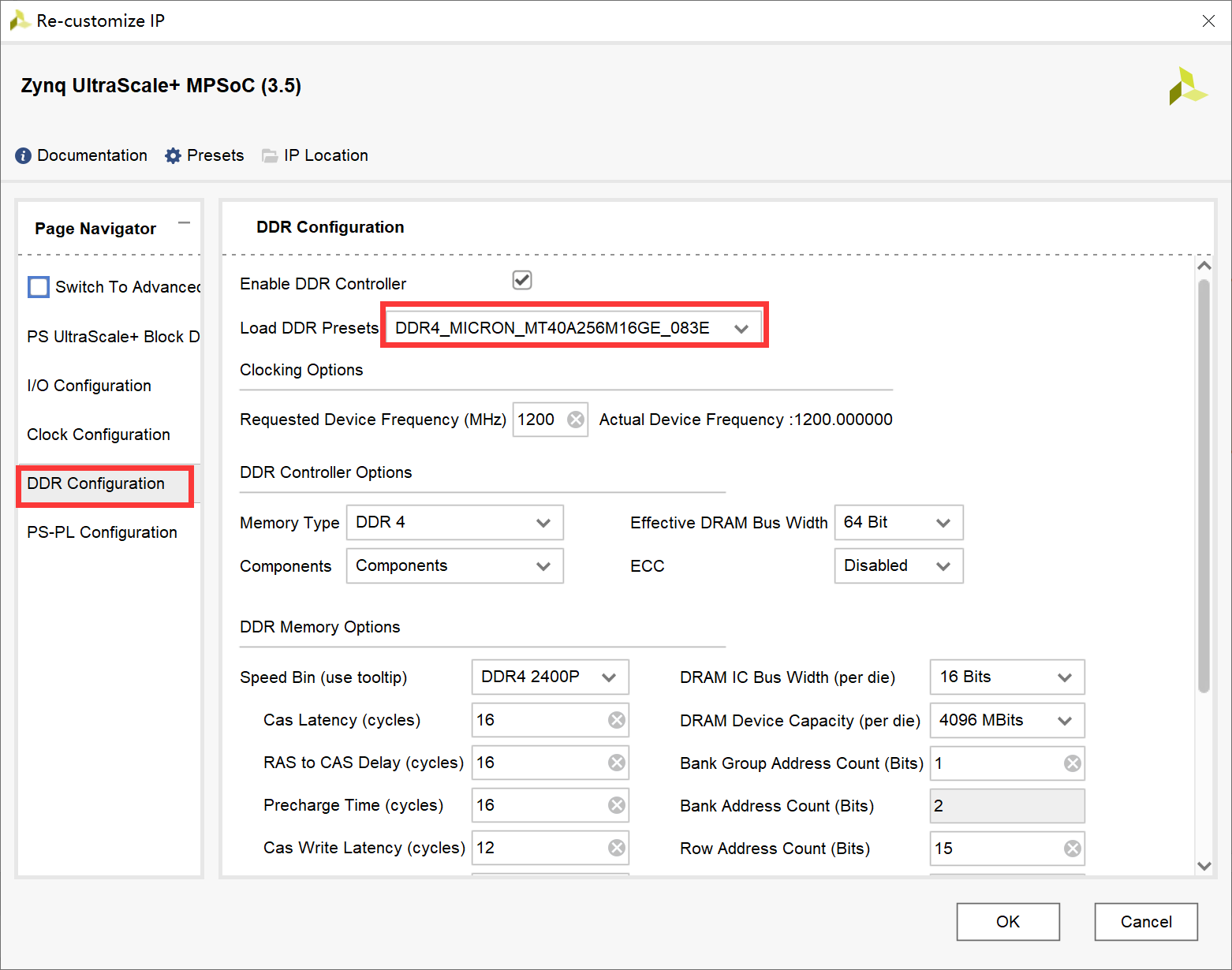

DDR配置,根据ZCU104的User Guide,这里选择后缀为083E的型号

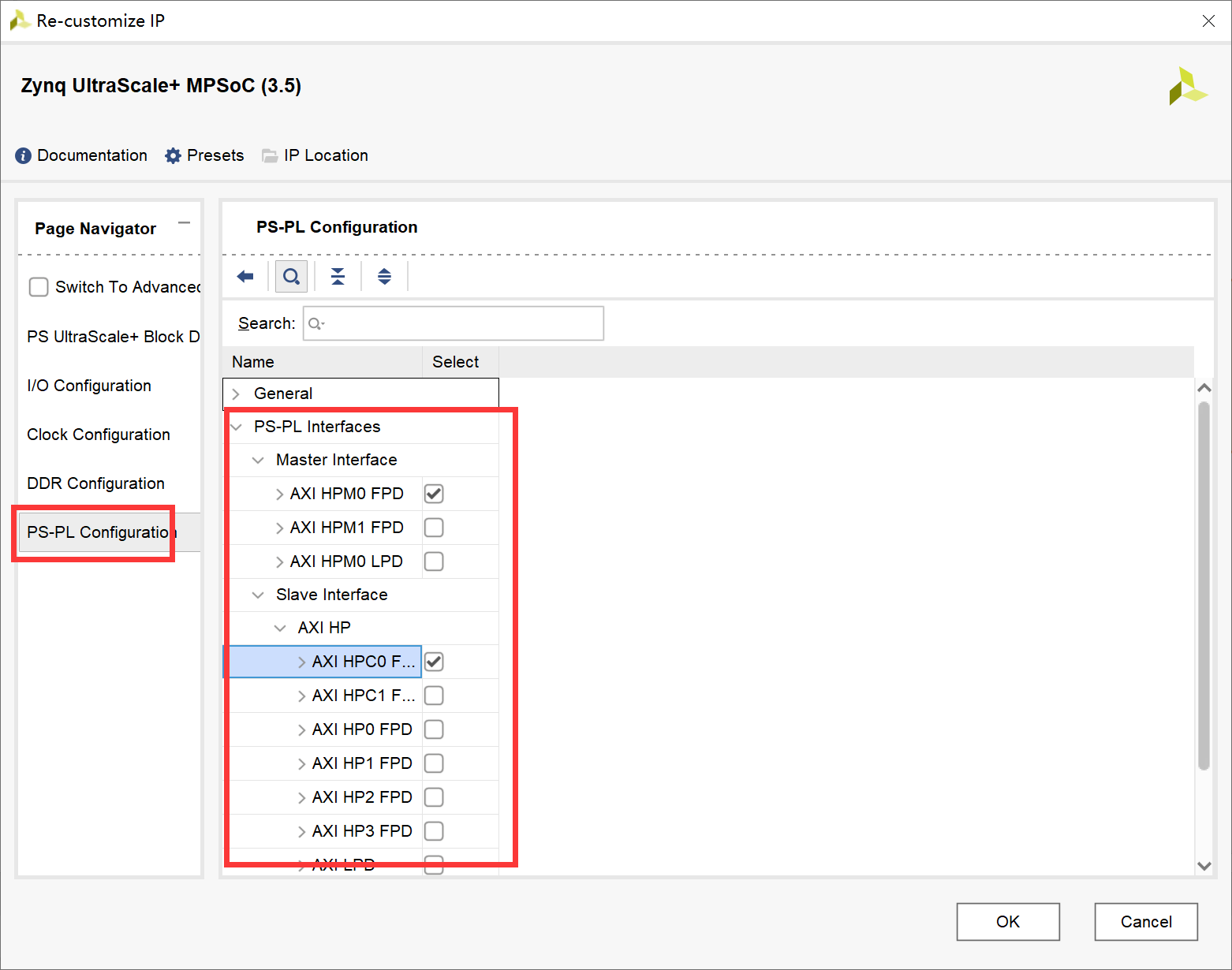

PS与PL端口配置,master接口1个,slave接口1个

默认PS给PL的时钟是100M,中断引脚打开,所以我们不再修改,完成配置

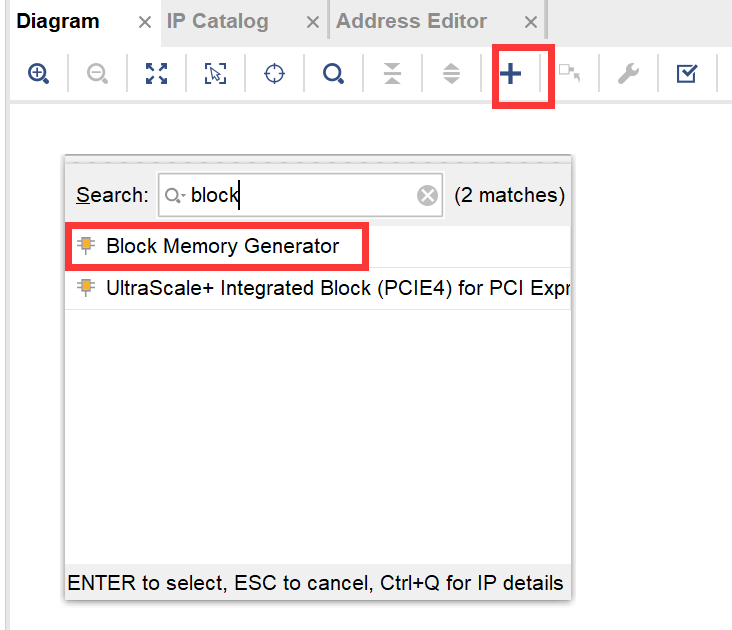

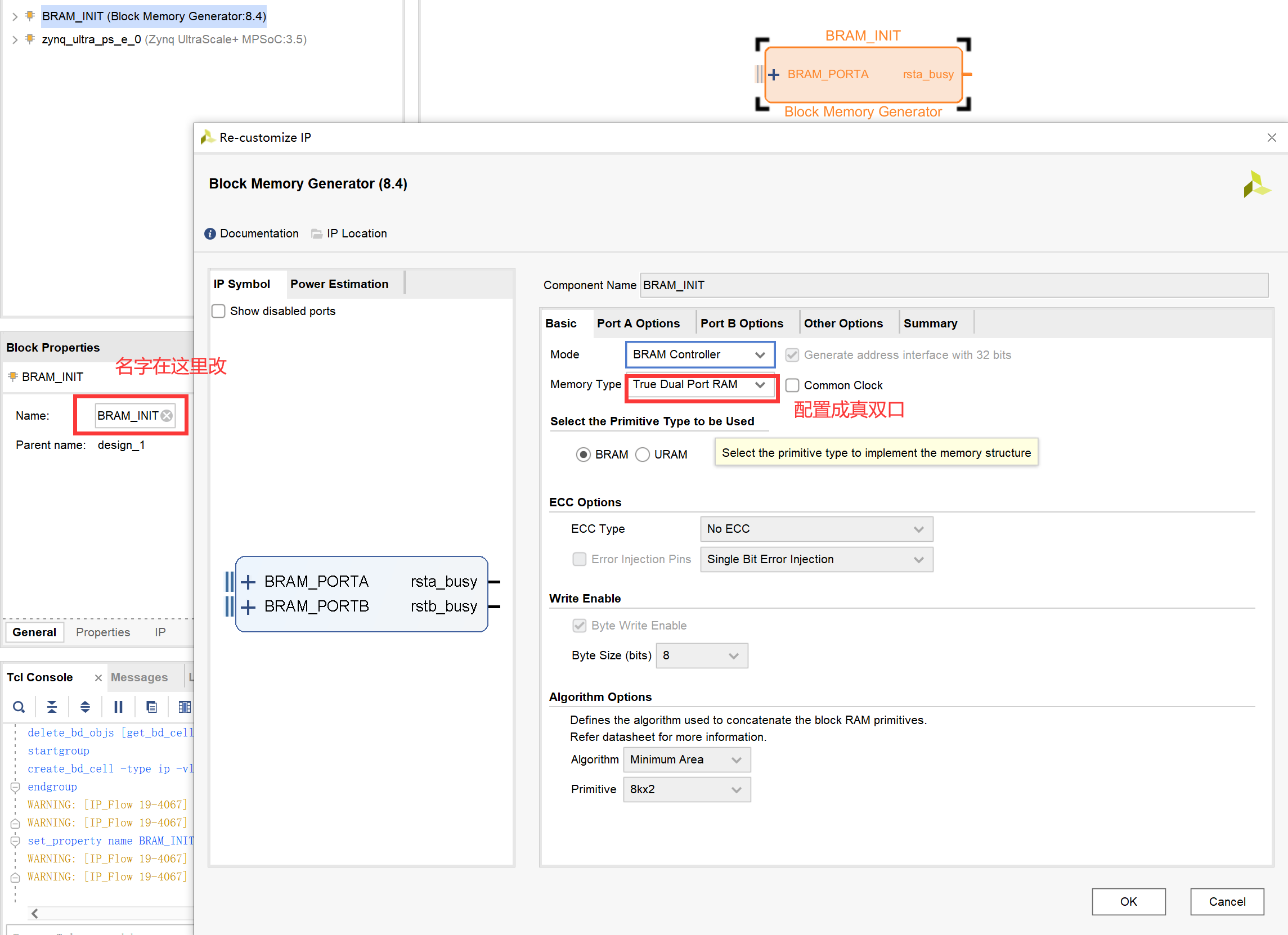

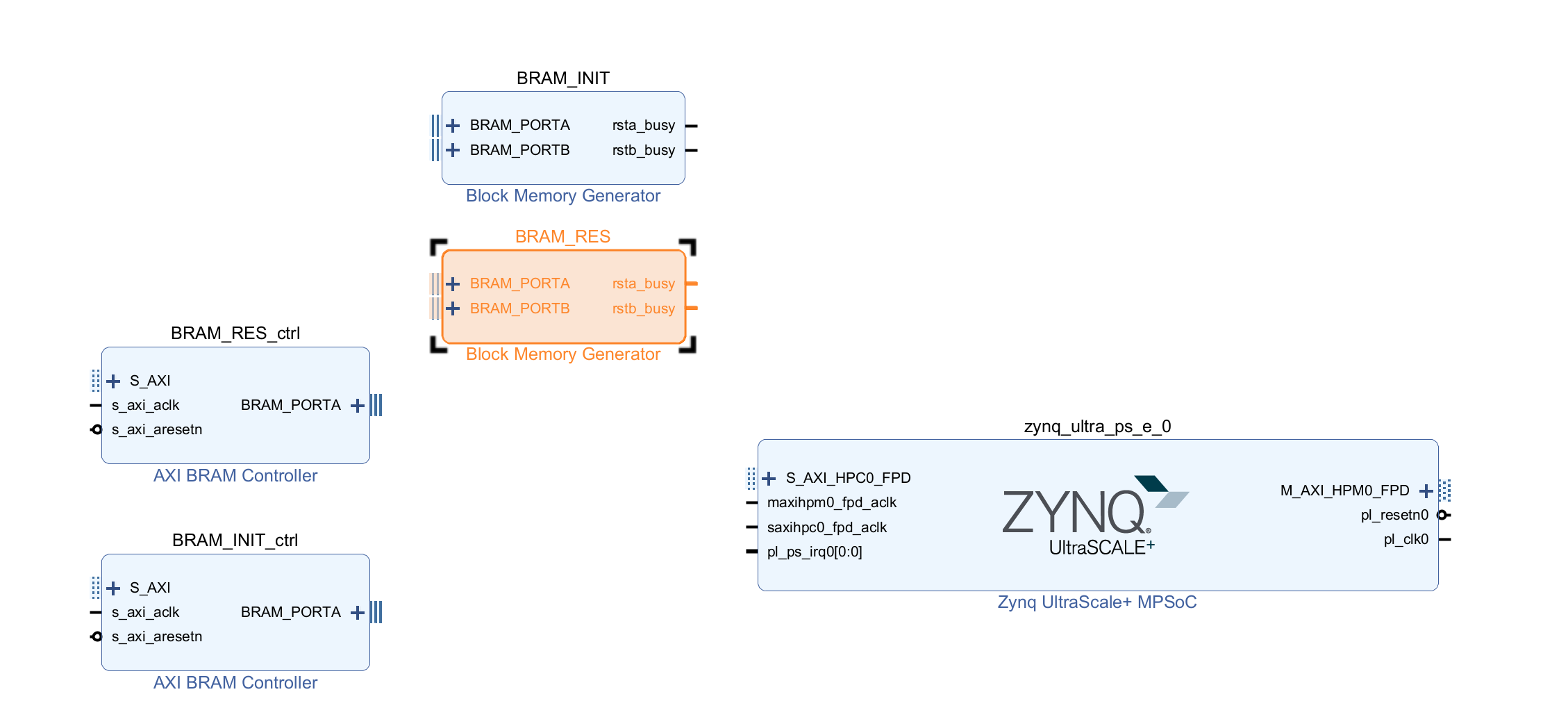

添加BRAM的IP

配置成真双口,这里要注意BRAM的数据位宽和地址,这里数据位宽是32bit,跟DUT里面一致,就不再修改。依次加入BRAM_INIT和BRAM_RES

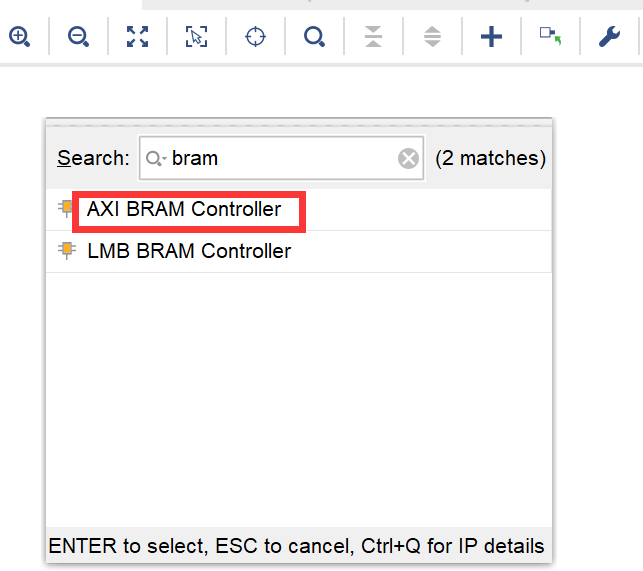

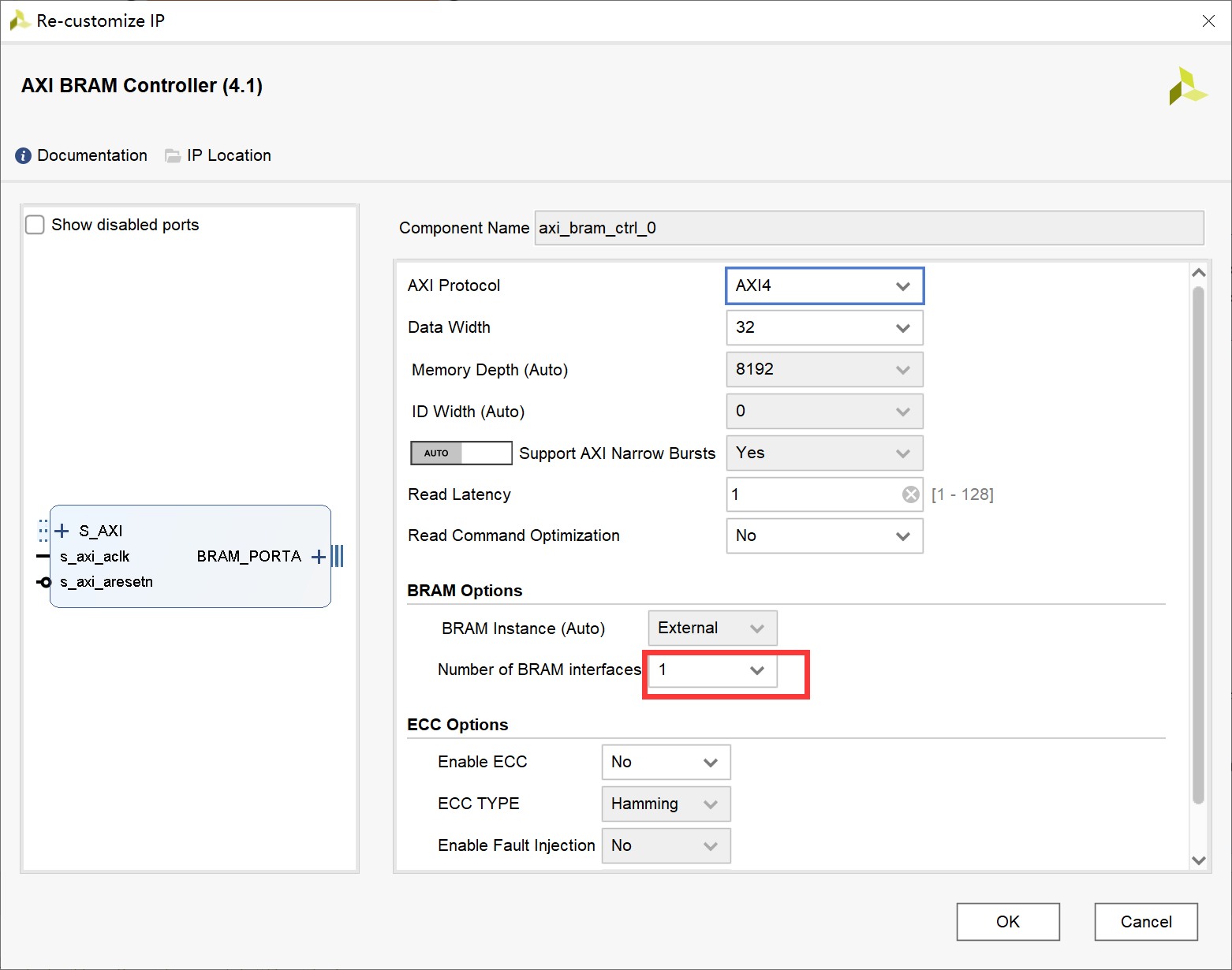

添加bram controller

这里给BRAM_RES和BRAM_INIT每个都配置一个bram controller,所以bram controller配置成一个接口就行

目前添加的IP情况如下

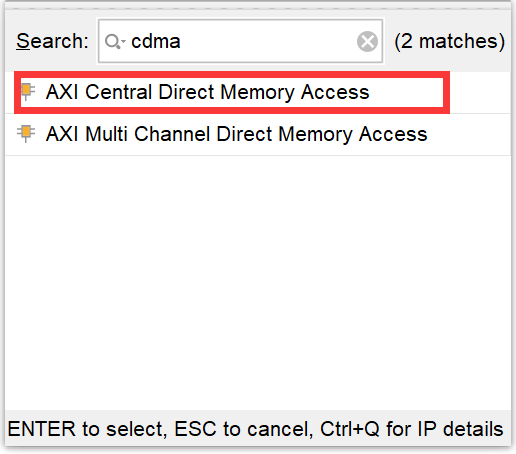

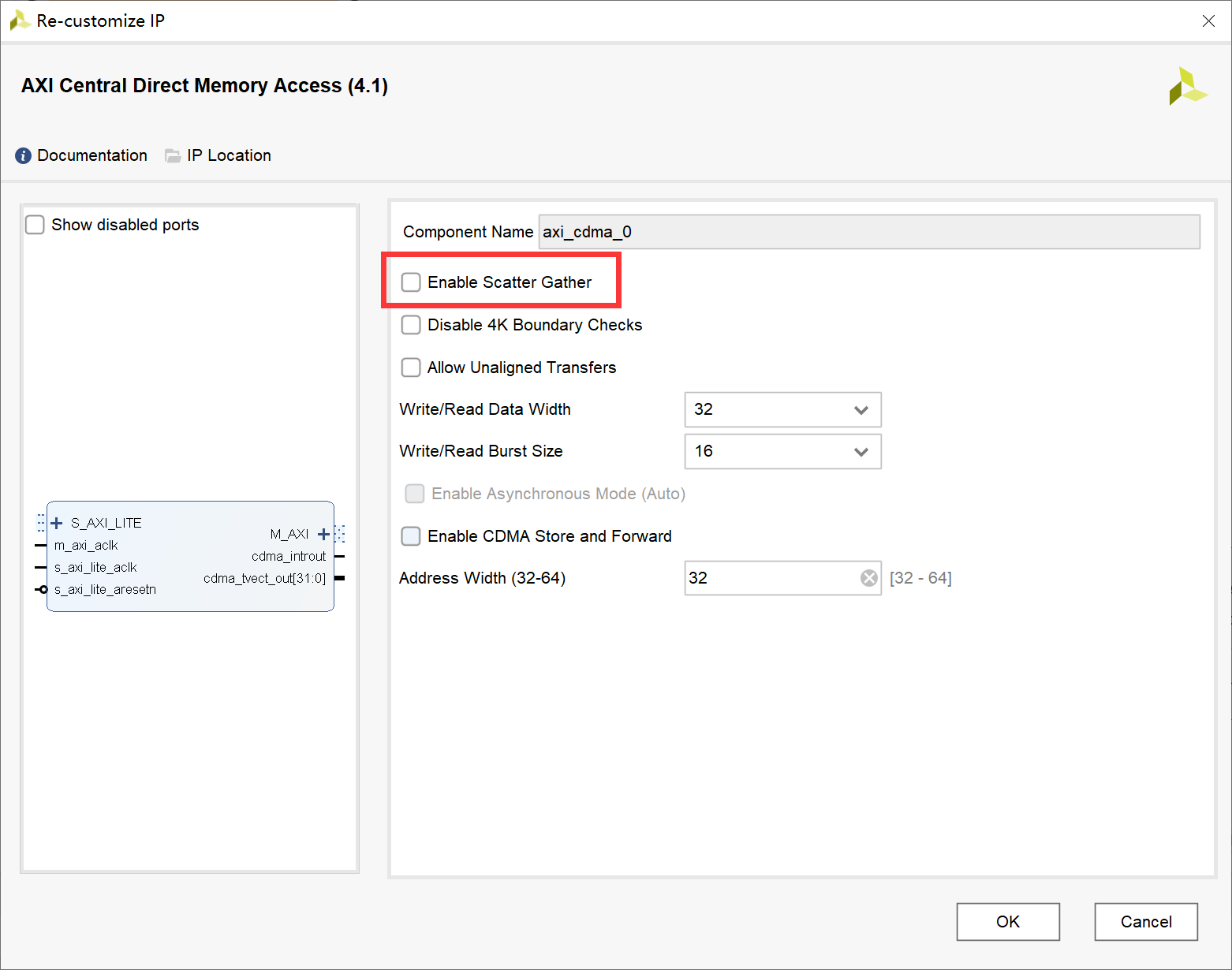

添加CDMA

配置如下

后面连接的时候,使用的AXI SmartConnect,这样数据传输更快。

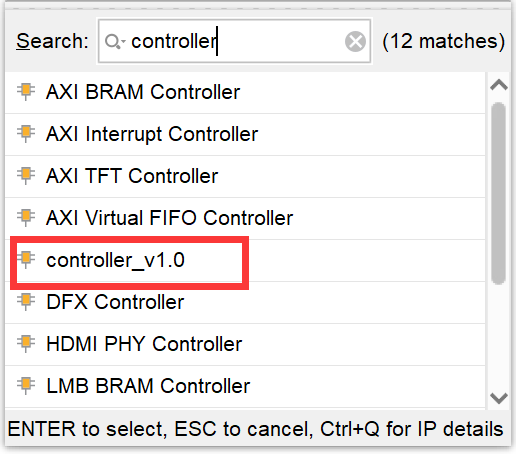

添加自己的IP

添加自己的IP,controller和dut,不需要配置

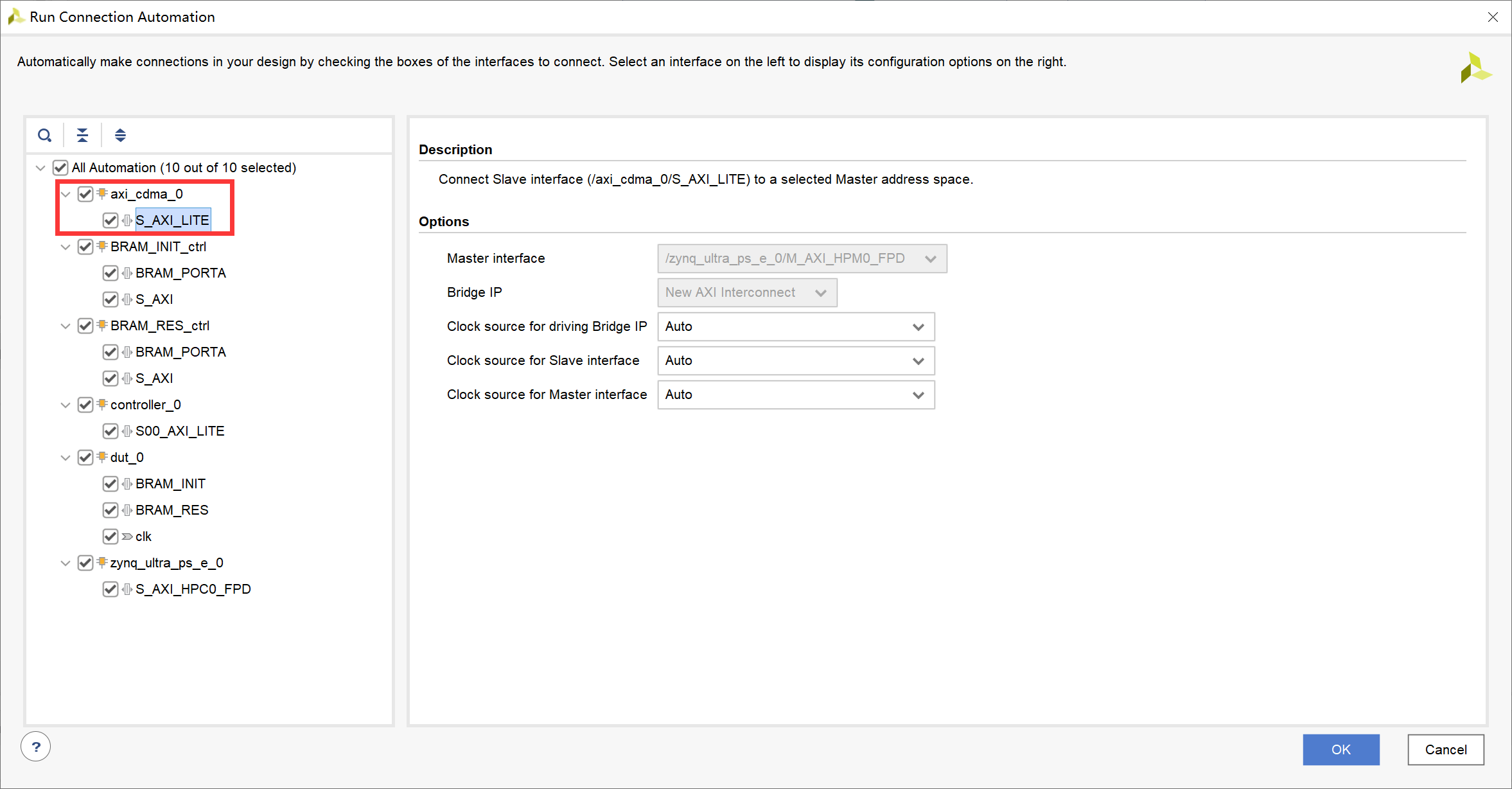

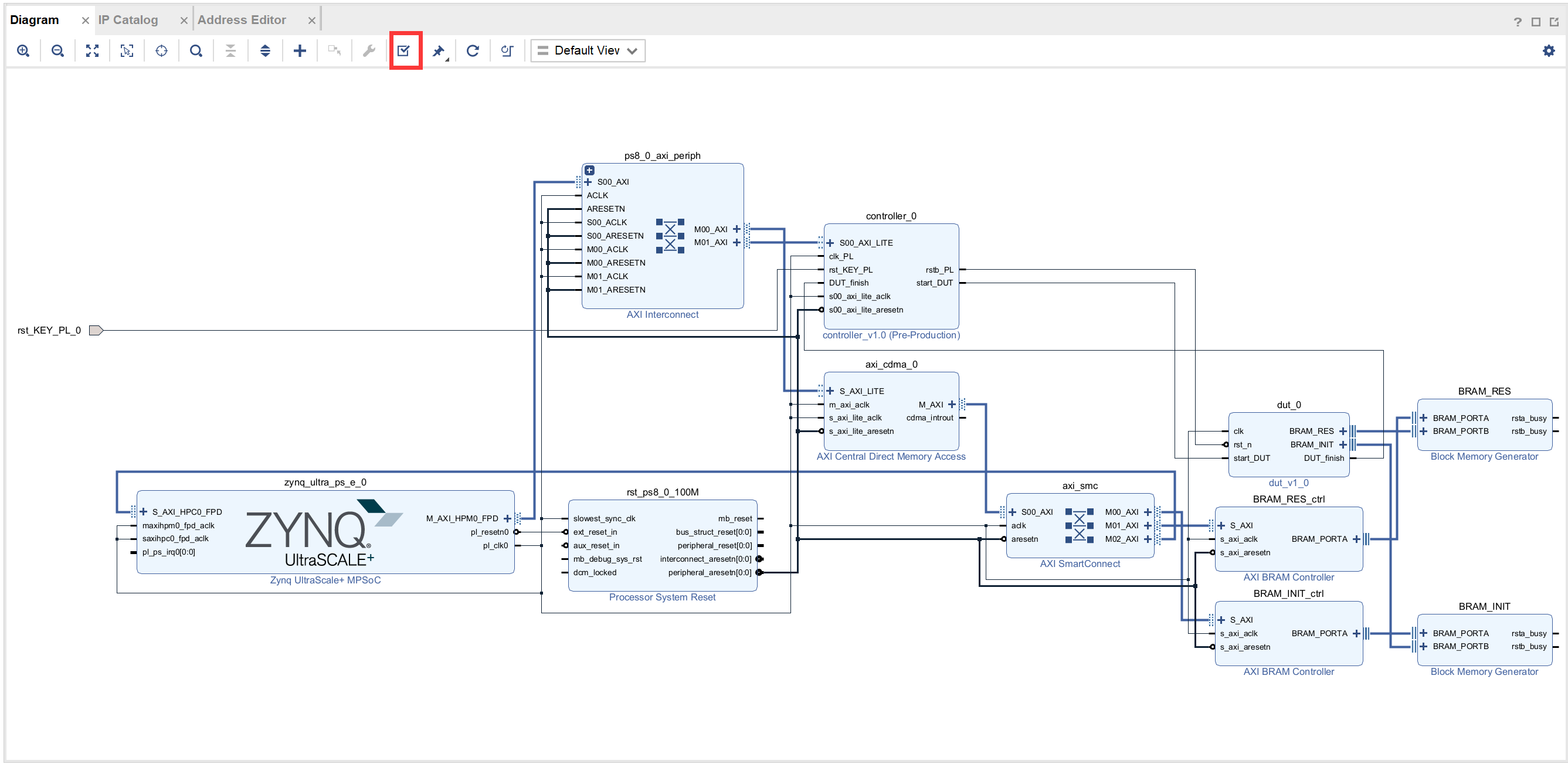

自动连接IP

点击block design的左上角的Run Connect Automation

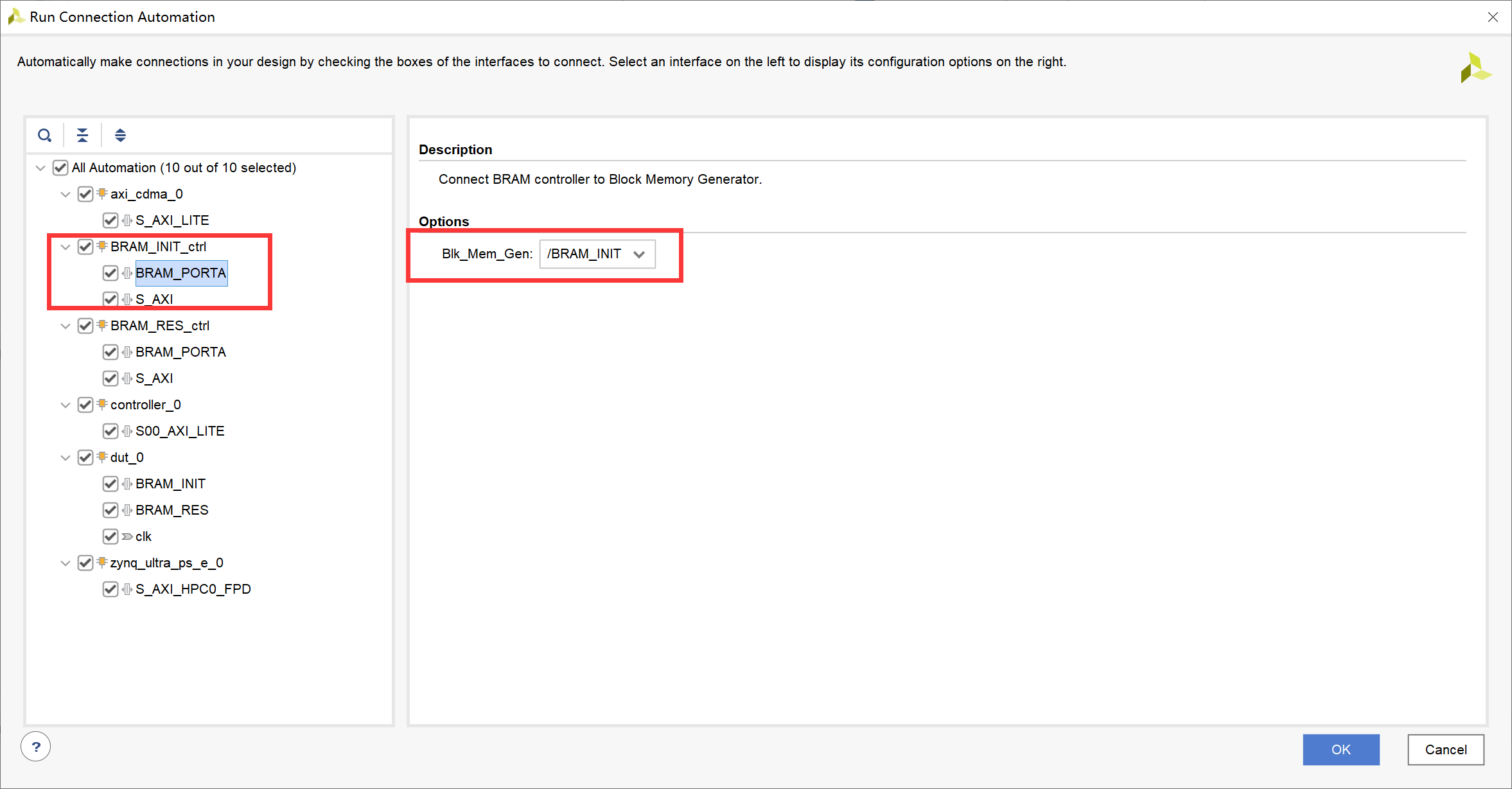

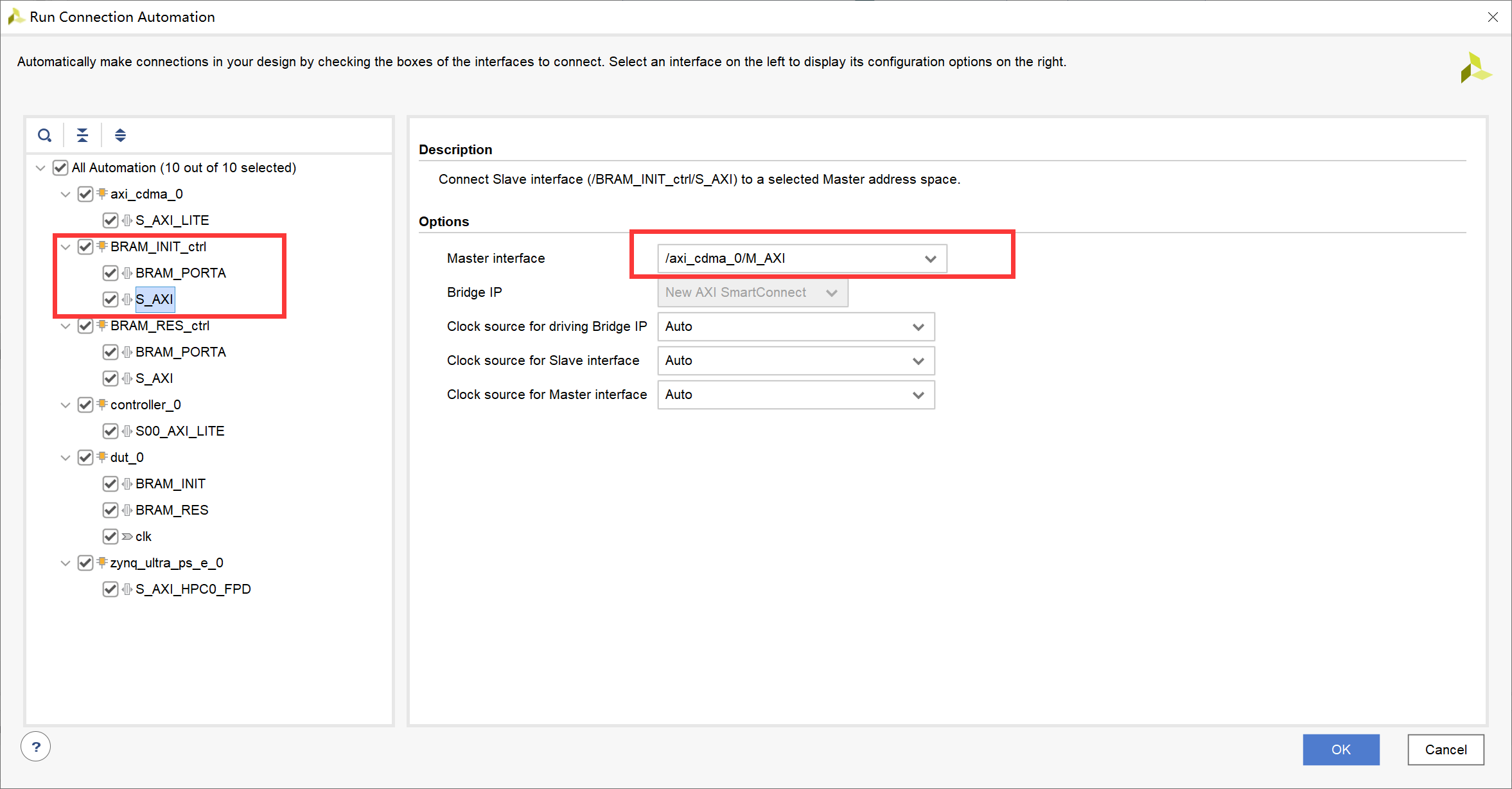

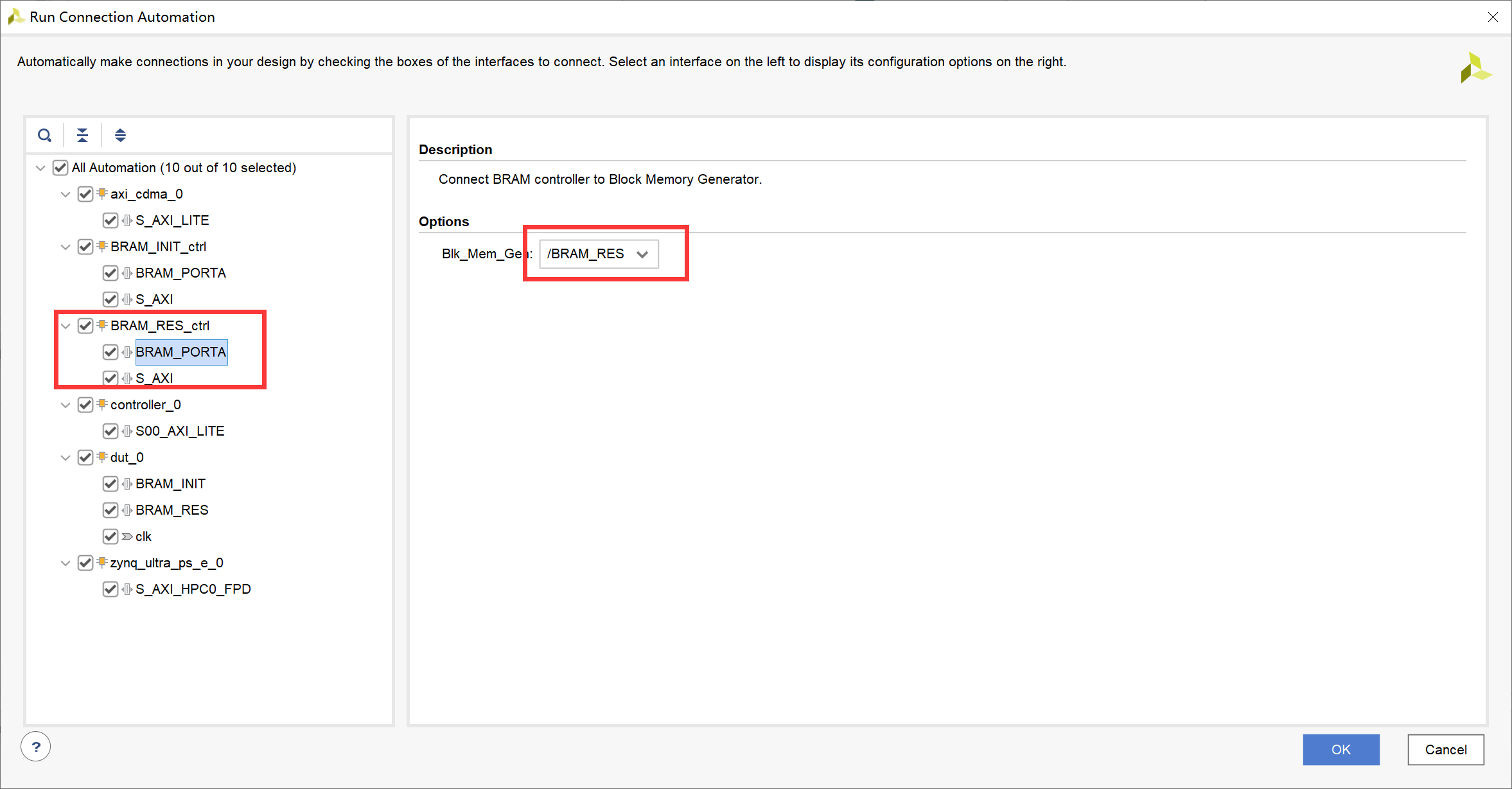

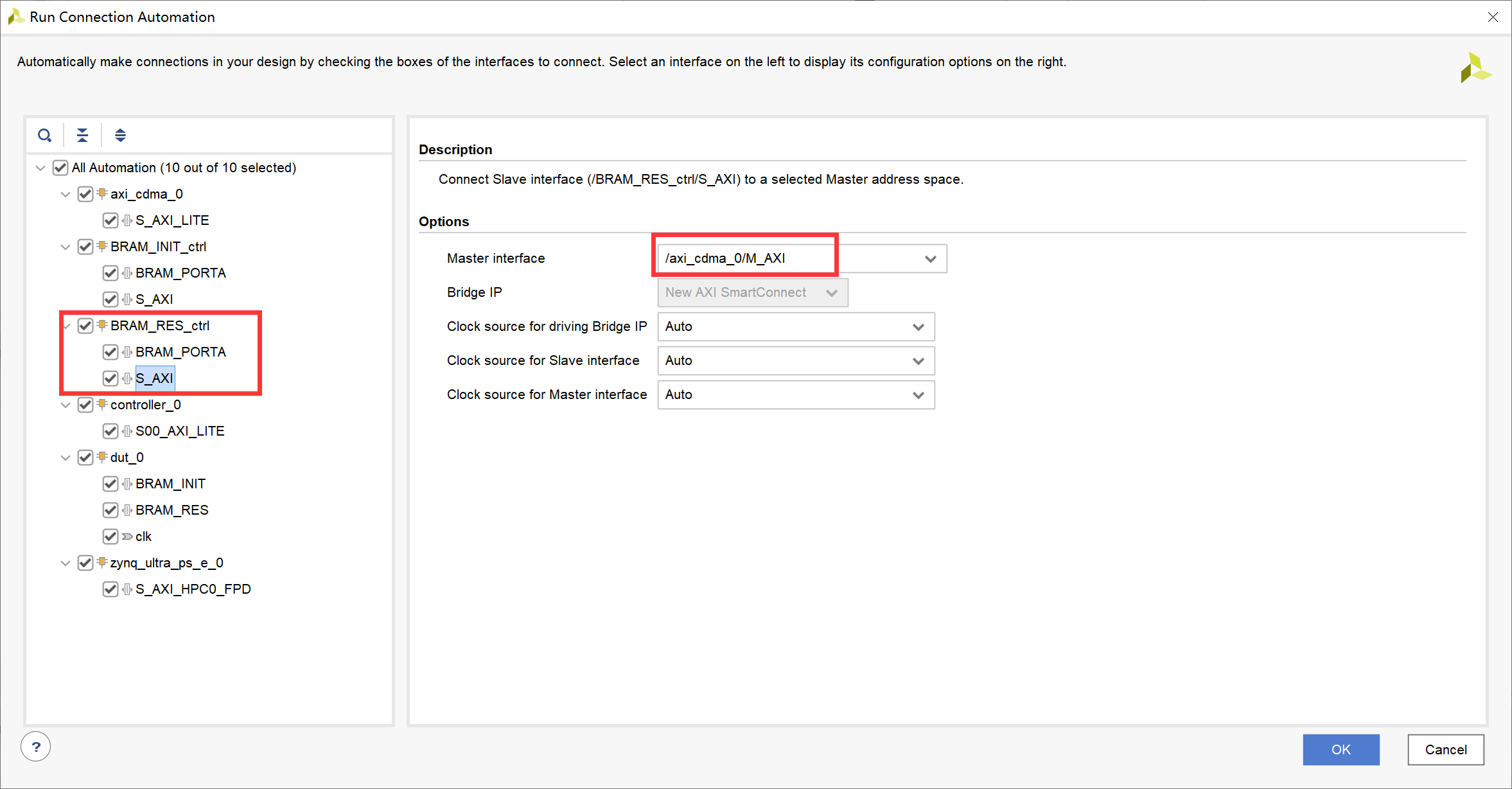

按照下图配置

配置BRAM_INT_ctrl

配置BRAM_RES_ctrl

controller和ps的保持默认就行

配置dut的BRAM端口,选择对应的就行

最后点击OK

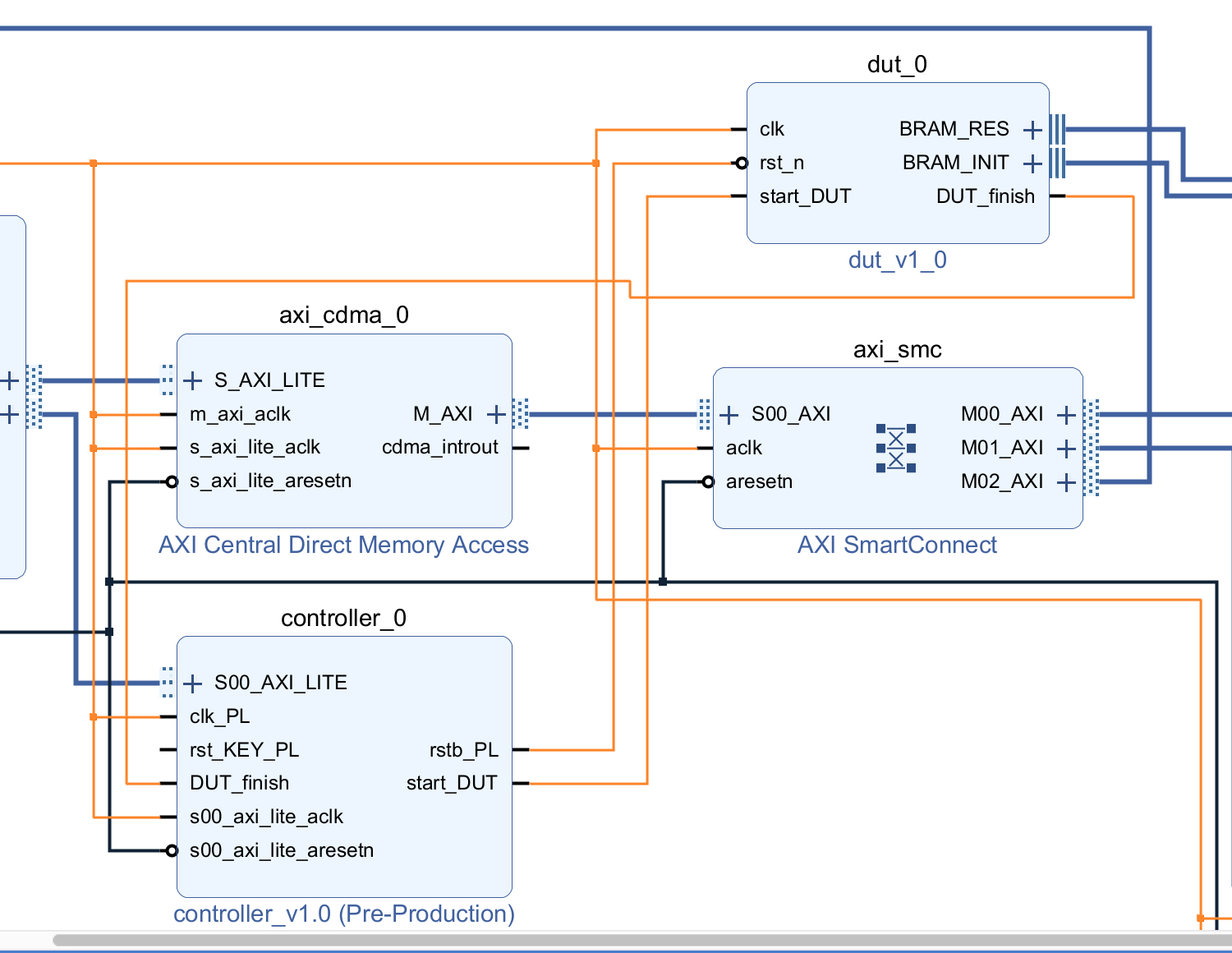

手动连接

连接clk_PL,start_DUT,DUT_finish,rst_n这些信号

(这里的cdma的中断引脚cdma_introut应该要跟ps的pl_ps_irq连接的,这里忘记连接了,但是后面生成镜像驱动也没有问题,可能是因为我后面使用轮询来操作的,如果想用中断操作,建议这里一定要连接上)

将rst_KEY_PL引出来,通过按键复位。右键rst_KEY_PL,选择Make External

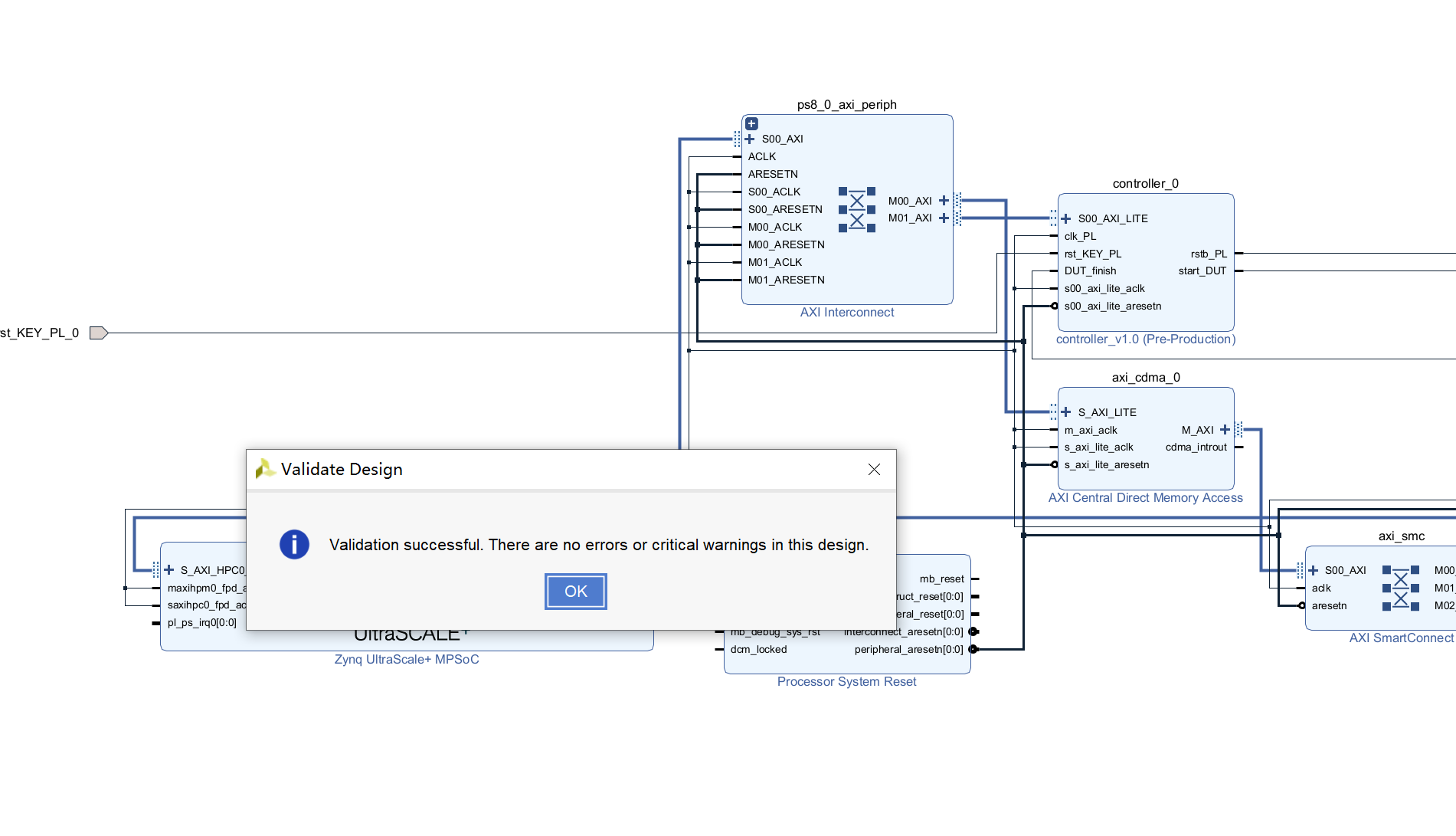

最后点击验证

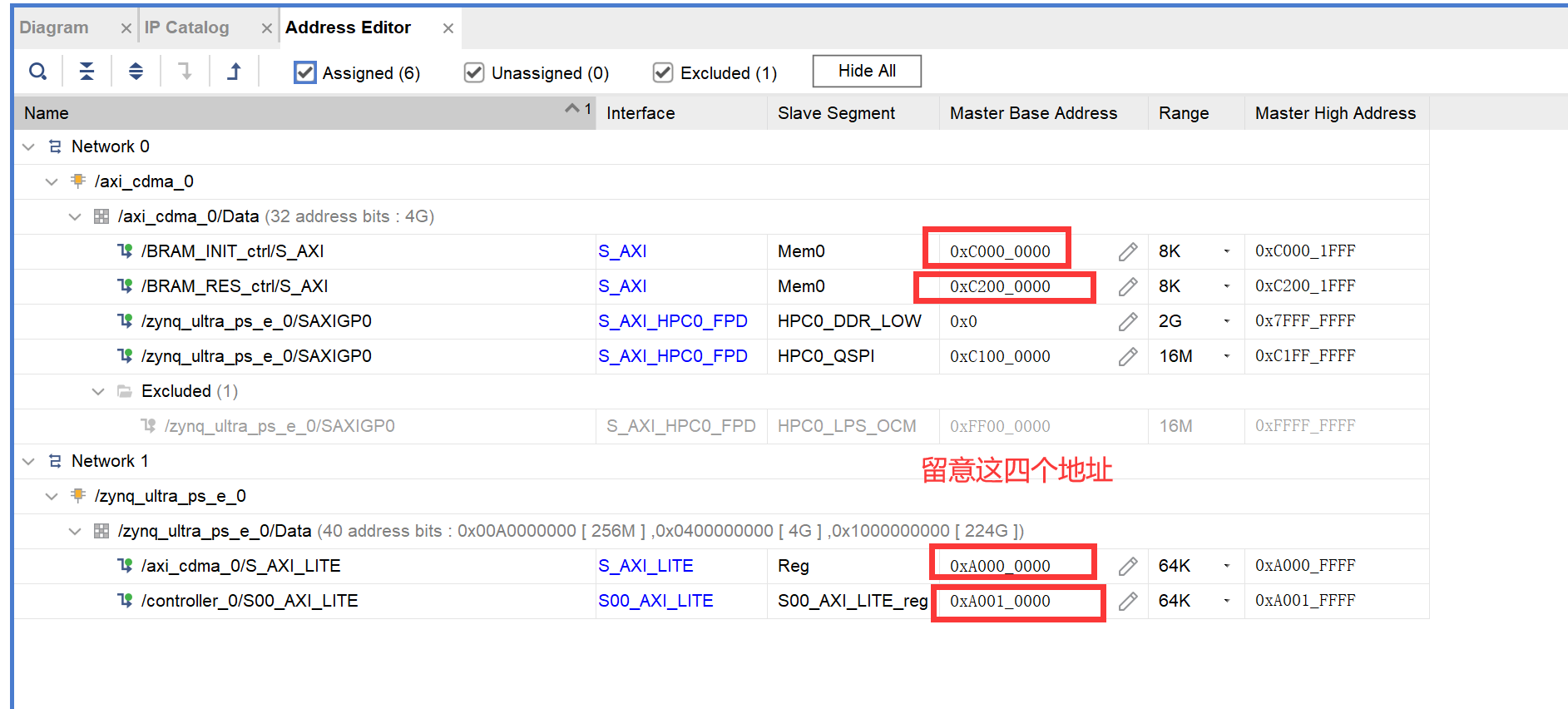

验证通过后查看地址分配情况,后面Linux下映射虚拟地址到物理地址有用

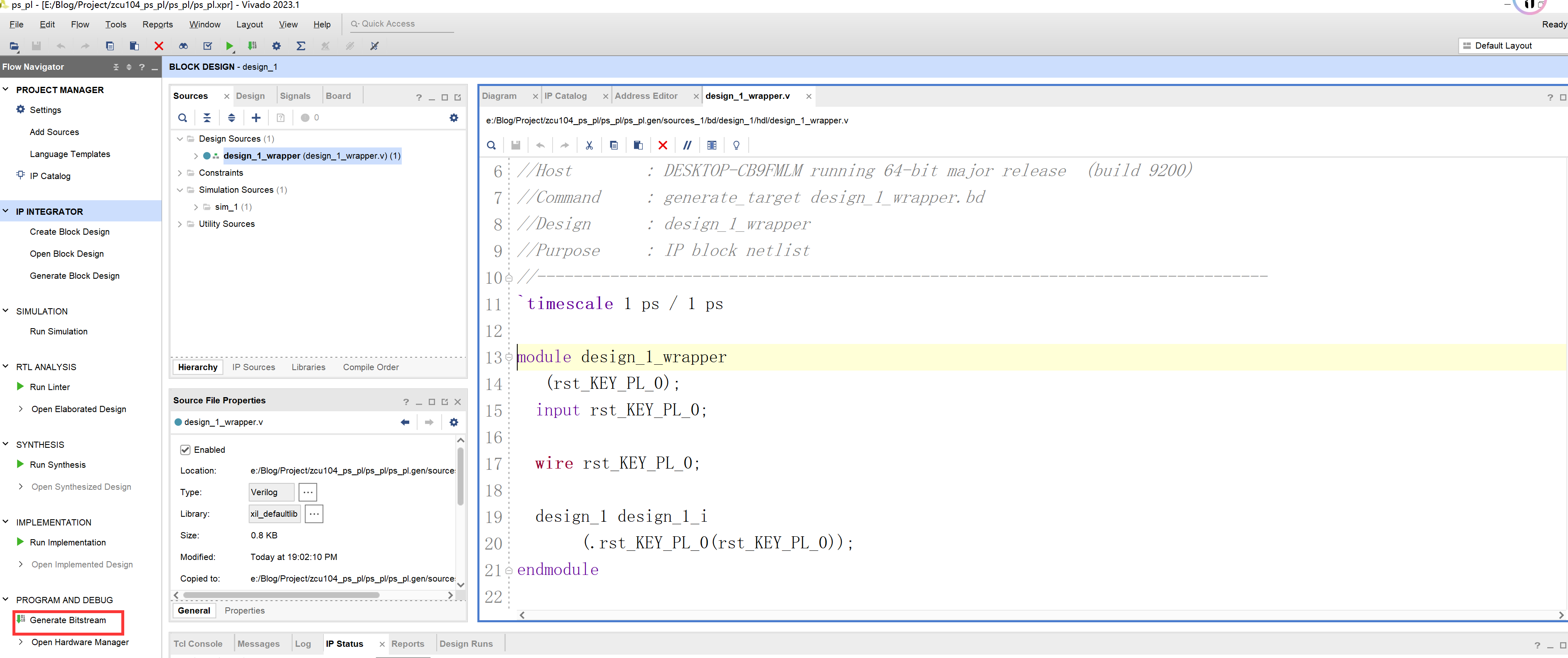

3.打包BD

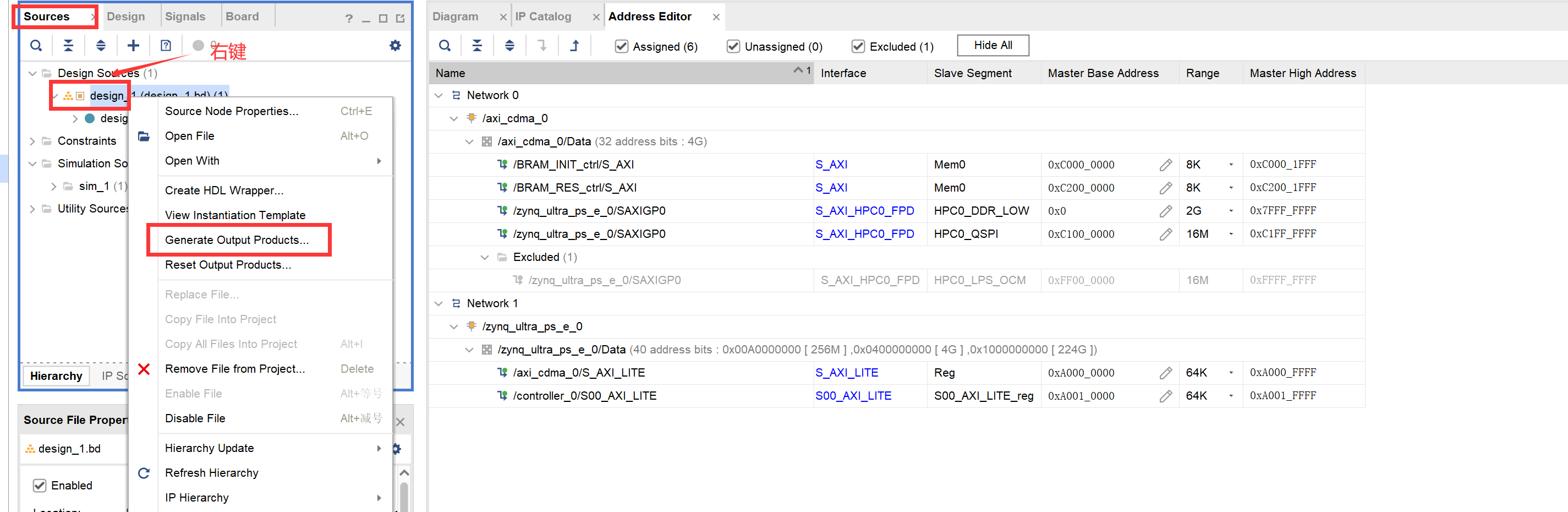

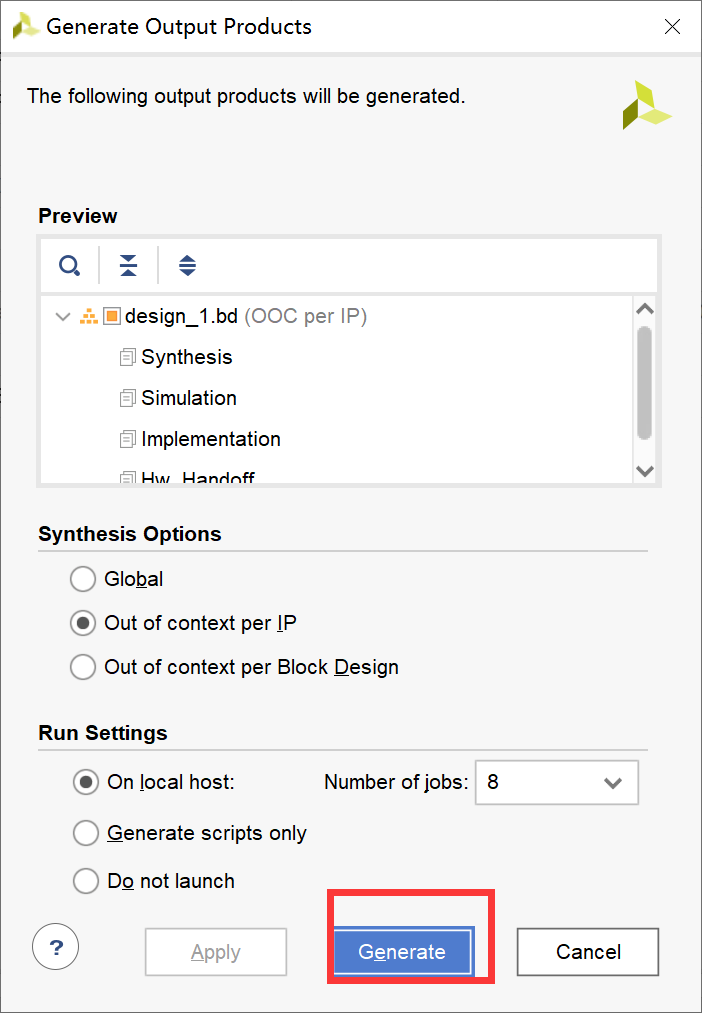

在sources页面,右键bd,选择Generate Output Products

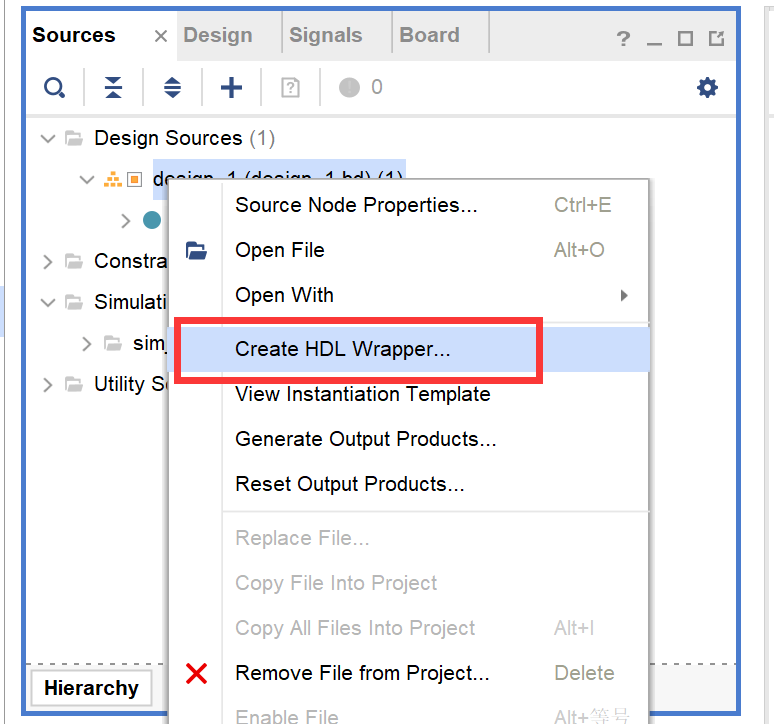

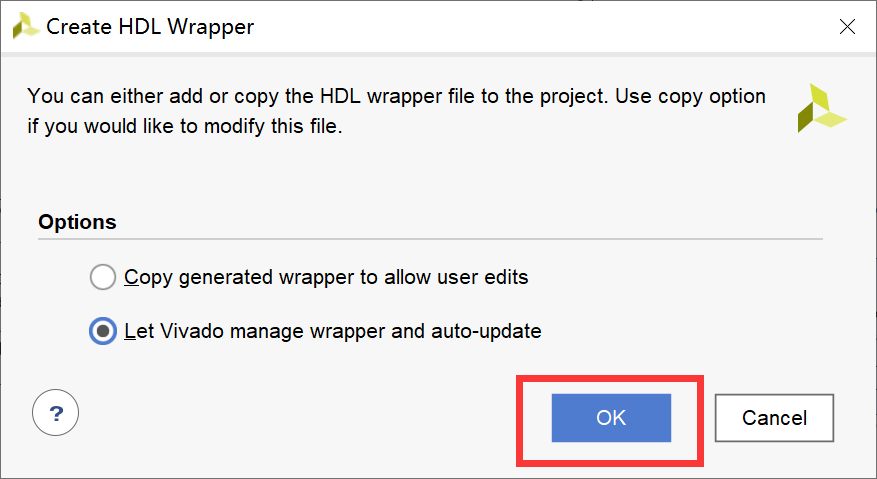

完成后,创建顶层文件,如下图选择

4.添加约束文件

set_property PACKAGE_PIN B3 [get_ports rst_KEY_PL_0]

set_property IOSTANDARD LVCMOS33 [get_ports rst_KEY_PL_0]

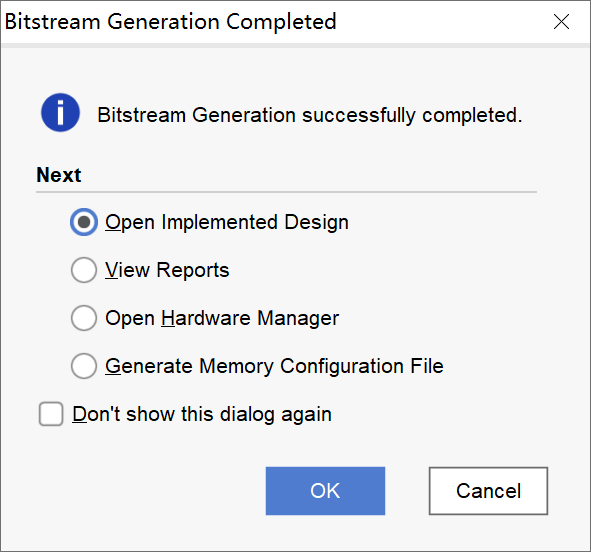

5.生成比特流

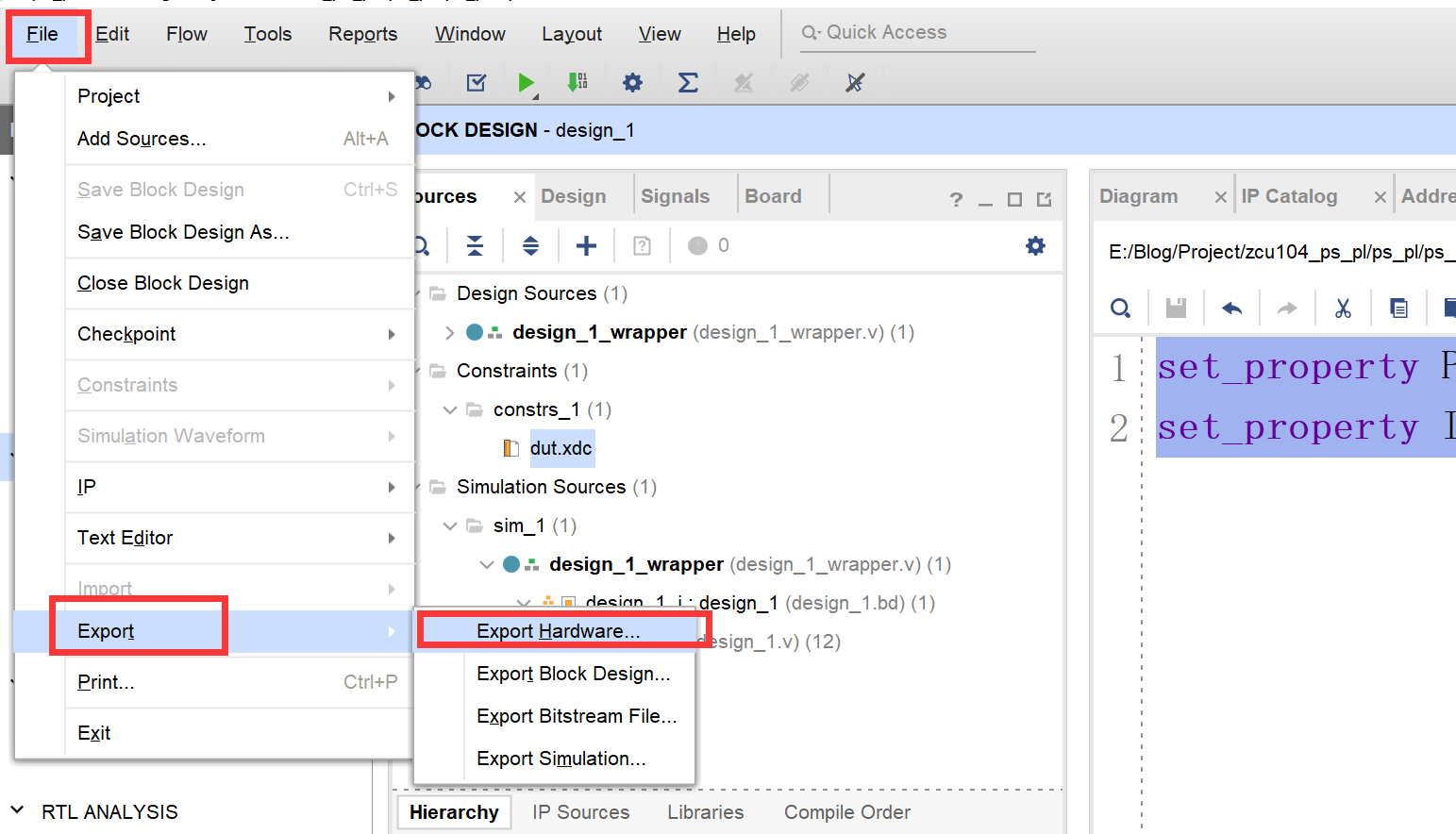

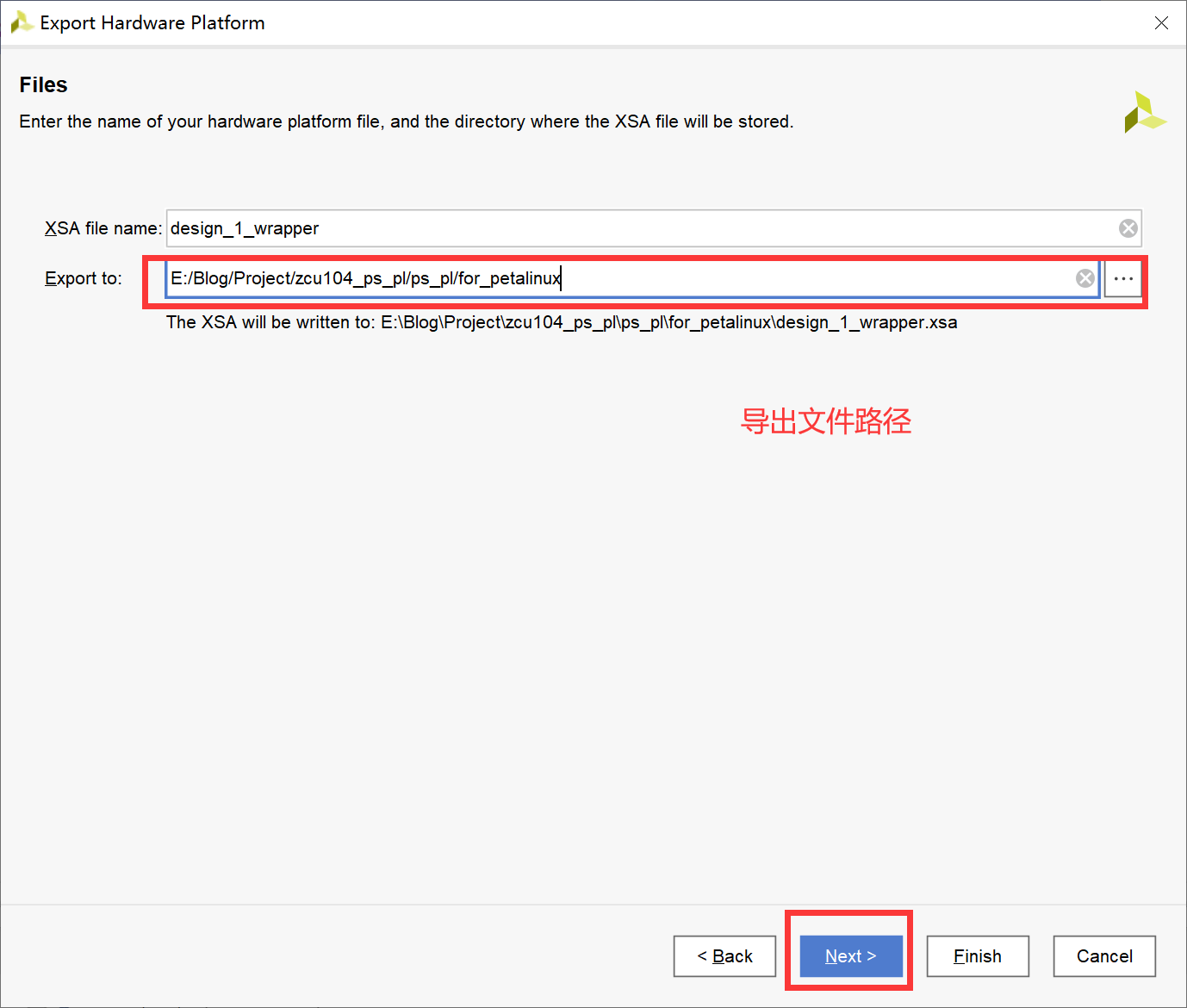

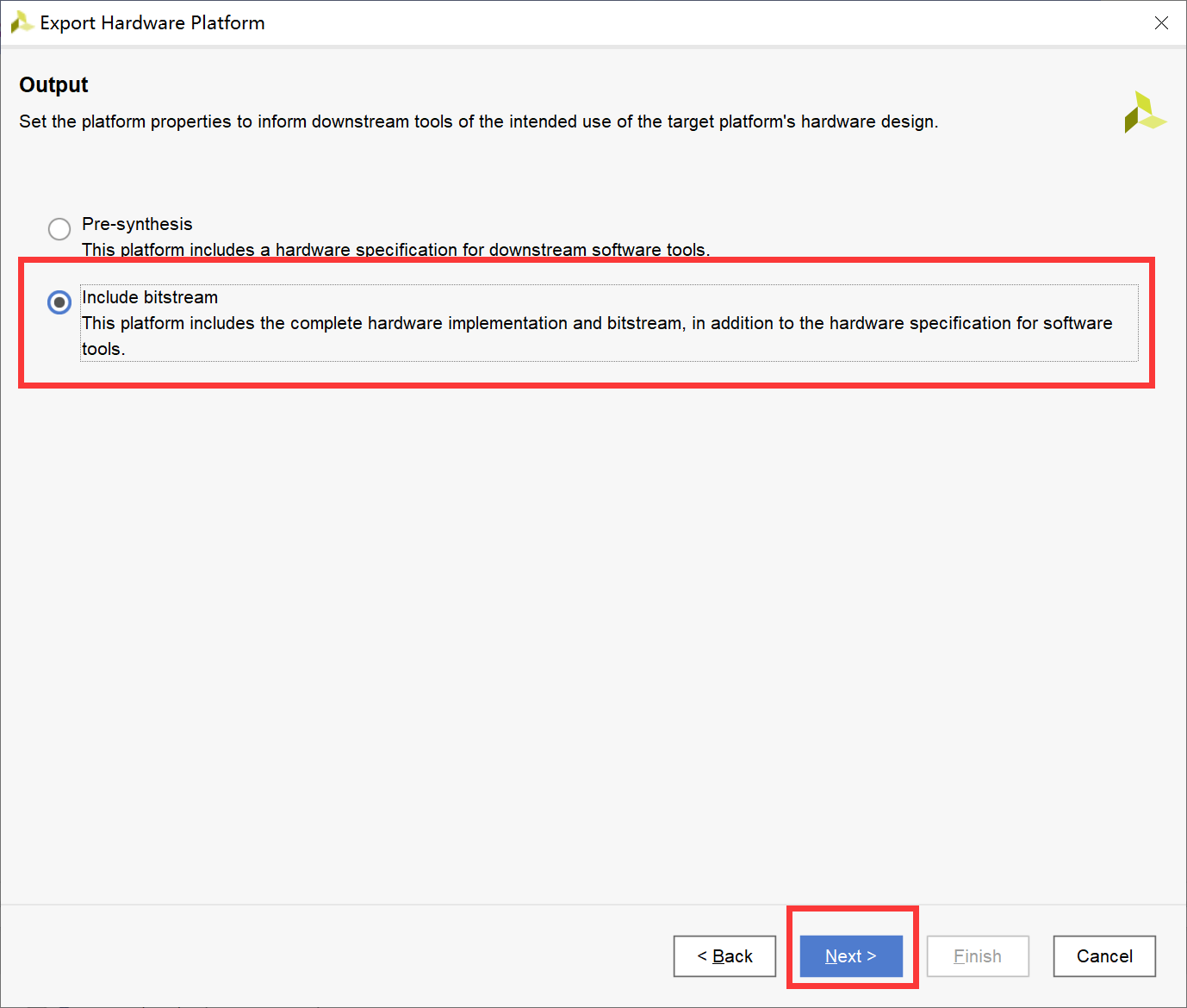

6.导出硬件文件(XSA)

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步