Makefile细碎知识点记录

由于有些规则用的少,记不住,但还是时不时能用到,开个记录帖记一下这些零散的规则。

参考文档:跟我一起学Makefile

1.忽略某些文件

-include <filename>

2.环境变量 MAKEFILES

如果当前环境中定义了该变量,make 会把该变量当作类似 include 的动作,但该变量引入的目标不会起作用,如果环境变量中定义的文件发现错误,make 会忽略。可能会导致一些未知问题。

3.关键字 wildcard、patsubst

4.静态模式

可以更容易定义多目标的规则。

objects = foo.o bar.o

all: $(objects)

$(objects): %.o: %.c

$(CC) -c $(CFLAGS) $< -o $@

目标从 objects 中获取,$<表示第一个文件,$@表示目标集。

5.echo显示命令

格式与 bash 有点区别,@echo 需要打印的命令。

make -n 可以只打印不执行命令。

6命令执行

如果第二条命令在第一条命令的基础上执行,需要在同一行用分号隔开。

7.变量

—用“ = ”操作符时,变量可以用后面的变量进行定义。

CFLAGS = $(include_dirs) -O include_dirs = -Ifoo -Ibar

CFLAGS 展开后是 -Ifoo -Ibar -O

—用“:”操作符时,变量不能用后面的变量进行定义。

—“?=”操作符表示,如果之前定义过,就不定义,否则定义。

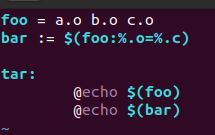

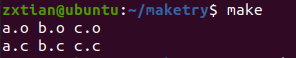

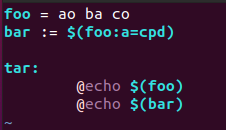

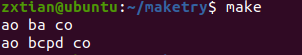

8.变量值的替换

$(var : a = b),将变量中所有以 a字符串 结尾的 a字符串替换成 b字符串

输出:

输出:

9.条件判断

—ifdef 和 ifndef,同 C 语言。

—ifeq 和 ifneq,语法格式:

ifeq (var1, var2)

else

endif

10.函数

如果有什么需要用的或者看不懂的函数可以先从这个链接里找找有没有介绍。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· 阿里巴巴 QwQ-32B真的超越了 DeepSeek R-1吗?

· 【译】Visual Studio 中新的强大生产力特性

· 10年+ .NET Coder 心语 ── 封装的思维:从隐藏、稳定开始理解其本质意义

· 【设计模式】告别冗长if-else语句:使用策略模式优化代码结构