Xilinx URAM使用说明 UG573

UltraRAM Resources

UltraRAM Summary

UltraRAM 是单时钟、双端口、同步存储器,可用于 UltraScale+™ 器件。由于 UltraRAM 与柱状(columnar)架构兼容,因此多个 UltraRAM 可以实例化并直接级联在一个 UltraRAM 列中,用于器件的整个高度。单个时钟区域中的列包含 16 个 UltraRAM 块。

具有 UltraRAM 的设备包括分布在设备中的多个 UltraRAM 列。 UltraScale+ 系列中的大多数器件都包含 UltraRAM 块。有关特定器件系列中 UltraRAM 的可用数量,请参阅 UltraScale 架构和产品概述 (DS890) [参考资料 1]

UltraRAM块是按设备中的一列或多列排列的288 KB(4096*72)单时钟同步内存块。每个时钟区域每列有16个UltraRAM块。

使用专用级联路由可以在一列内将多个UltraRAM块级联在一起,唯一的限制是器件的高度或堆叠硅互连(SSI)器件中的单个超级逻辑区(SLR)。此外,可以使用少量的逻辑资源将多个列级联在一起。如果采用适当的流水线方式,级联UltraRAM块不会出现计时损失。

UltraRAM是一种灵活的高密度内存构建块。每个UltraRAM块可以存储高达288Kbit的数据,并配置为4K x 72的内存块。UltraRAM的容量是BRAM的八倍。与BRAM类似,设备上分布有多个UltraRAM列。UltraRAM有两个端口,均可寻址所有4K x 72位。每个端口可以在每个端口的每个时钟周期独立执行一次读操作或一次写操作。然而,在内部,SRAM阵列使用单端口存储单元。

双端口操作是通过在单个周期内执行端口A操作,然后执行端口B操作来实现的。因此,两个端口共享一个时钟输入。每个端口在一个周期内只能执行一次写操作或读操作。执行写入操作时,读取输出保持不变并保持先前的值。

288 KB数据块可以级联,以促进更深层次的内存实现。与级联相关的大部分布线都包含在UltraRAM列中。因此,如果UltraRAM块被适当地流水线处理,则几乎不需要或不需要一般互连,并且不会由于布线而引起时序损失。

对于两个端口接口中的每一个,UltraRAM最多包含四个流水线阶段。在独立的非级联模式中,UltraRAM可以配置为一到四个时钟周期的延迟,但通常只需要一到三个周期的延迟,具体取决于目标频率。级联模式延迟是UltraRAM链大小、频率目标和其他约束的函数。同样,时钟到输出的性能取决于所选的输出寄存器。使用Vivado工具集来确定特定设计实施的性能和打卡时间。

UltraRAM Key Features

- 在单个块中存储288K比特

- 双端口、4K x 72、单时钟同步存储器

- 用于构建更大块的 UltraRAM 级联。 UltraRAM 具有用于适当输入和输出的专用布线资源,以从较低的 UltraRAM 级联到较高的 UltraRAM

- 两个端口上的纠错编码 (ECC),具有单比特错误检测和纠正以及双比特错误检测

- 休眠省电功能

- 通过在 UltraRAM 块链中自动调用/释放睡眠模式来自动节能

- 输入、输出和级联路径上的可选流水线触发器

- 输出的数据输出复位功能被复位为全 0

- x72 的单端口宽度

- UltraRAM 存储器在上电或设备复位期间被初始化为全 0。没有用户定义的 INIT 属性,因此无法将 SRAM 阵列的内容初始化为用户定义的值。

UltraRAM Cascade 级联

UltraRAM 级联的特点是:

- UltraRAM 具有用于大多数输入和输出的专用布线资源,以从较低的 UltraRAM 级联到较高的 UltraRAM。

- 内置11 位MSB 地址的地址译码逻辑用于级联UltraRAM 时自动为读写操作生成内部使能。

- 列中的级联支持从下到上的一个方向,并且可以在不使用通用互连资源的情况下实现。

- 列之间的级联需要在每列的入口点和出口点使用设备布线和潜在的逻辑资源。

UltraRAM Error Correction Coding纠错编码

每个 UltraRAM 块提供一个 64 位 ECC 块。还提供独立的编码和解码功能。 ECC 模式可以注入错误。 UltraRAM ECC 的特点是:

- 两个端口上的可选 ECC 编码和解码。

- 单位和双位错误检测。

- 单比特纠错。

- 单比特或双比特错误注入能力。

- 在ECC 解码逻辑之后的可选流水线寄存器以获得最佳性能。

Block RAM and UltraRAM Differences

Block RAM 和 UltraRAM 之间的主要区别是:

- UltraRAM 具有一个单一的时钟输入,是完全同步的,并且与 Block RAM 不同,它不直接支持独立的时钟接口。

- 不支持可配置端口宽度的单个4K x 72 UltraRAM 或多个时钟域。但是,UltraRAM 块的字节写使能功能可用于在存储器结构本身之外支持此功能。

- UltraRAM 仅支持每个端口每个周期的读取或写入。

- 简单双端口(SDP) 和真正的双端口(TDP) Block RAM 模式不直接适用于UltraRAM。 UltraRAM 端口行为可以看作是 SDP 的超集,而不是 TDP。

- 固定读取行为; UltraRAM 没有用户可定义的先读、先写、不变模式。

- 静态数据级联; UltraRAM 没有动态级联输入或输出多路复用器控制。

- UltraRAM 不可能发生地址冲突。

- UltraRAM 级联数据、地址和控制信号,而不仅仅是数据线。

- 在UltraRAM 省电模式(SLEEP) 期间,只要满足设置和保持时间,用户操作将被忽略并且内容不会损坏。内存内容在睡眠省电模式下保留。

- 自动节能可以通过使用自动睡眠功能来实现,该功能可以根据活动独立控制唤醒和睡眠模式。该模式通过预测一列或多列中许多级联 UltraRAM 块的活动,动态地为链中选定的 UltraRAM 块打开或关闭睡眠模式。对于单个 UltraRAM 块应用程序,使用此功能需要许多不活动周期才能发挥作用。

不得违反 UltraRAM 地址、启用和睡眠引脚的时钟最小脉冲宽度和建立/保持时间。违反时钟最小脉冲宽度或这些设置/保持时间(即使写使能为低)可能会破坏 UltraRAM 的数据内容。这最常发生在时钟不稳定或驱动 UltraRAM 控制引脚的触发器被异步复位时,例如系统范围内的复位。为避免此问题,请确保时钟稳定,并为断言和反断言设计同步复位。当时钟不稳定时,禁用时钟缓冲器或禁用驱动 UltraRAM 控制引脚的逻辑或置低 UltraRAM EN 输入。

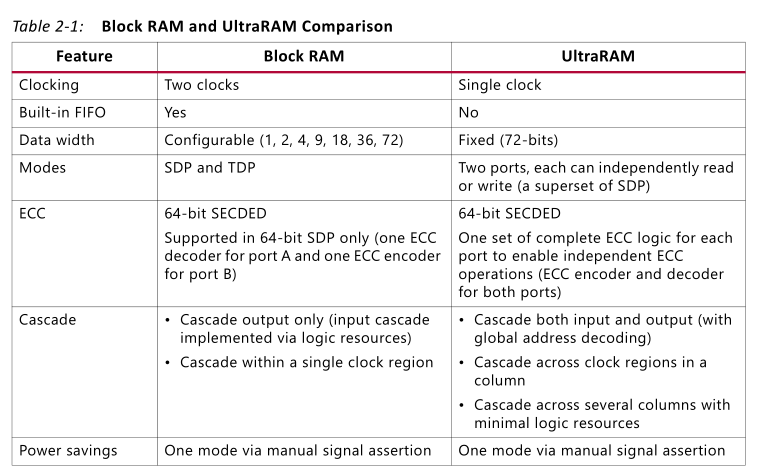

Block RAM 和 UltraRAM 比较

级联:

仅级联输出(输入级联通过逻辑资源实现) || 级联输入和输出(使用全局地址解码)

在单个时钟区域内级联 || 跨列中的时钟区域级联

|| 以最少的逻辑资源跨多个列级联

UltraRAM 原语

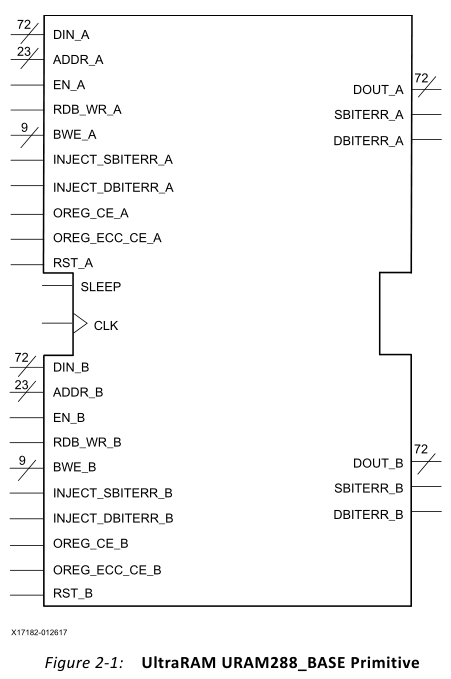

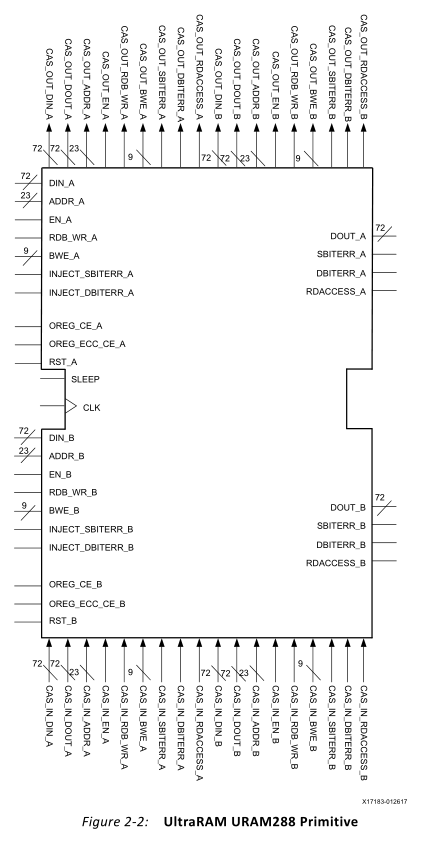

UltraRAM URAM288 和 URAM288_BASE 库原语是所有 UltraRAM 配置的基本构建块。 URAM288 原语支持所有可能的配置,包括级联和 ECC。 URAM288_BASE 原语是一个子集,支持没有级联功能的单个 UltraRAM 块实例。 URAM288_BASE 原语如图 2-1 所示,URAM288 原语如图 2-2 所示。

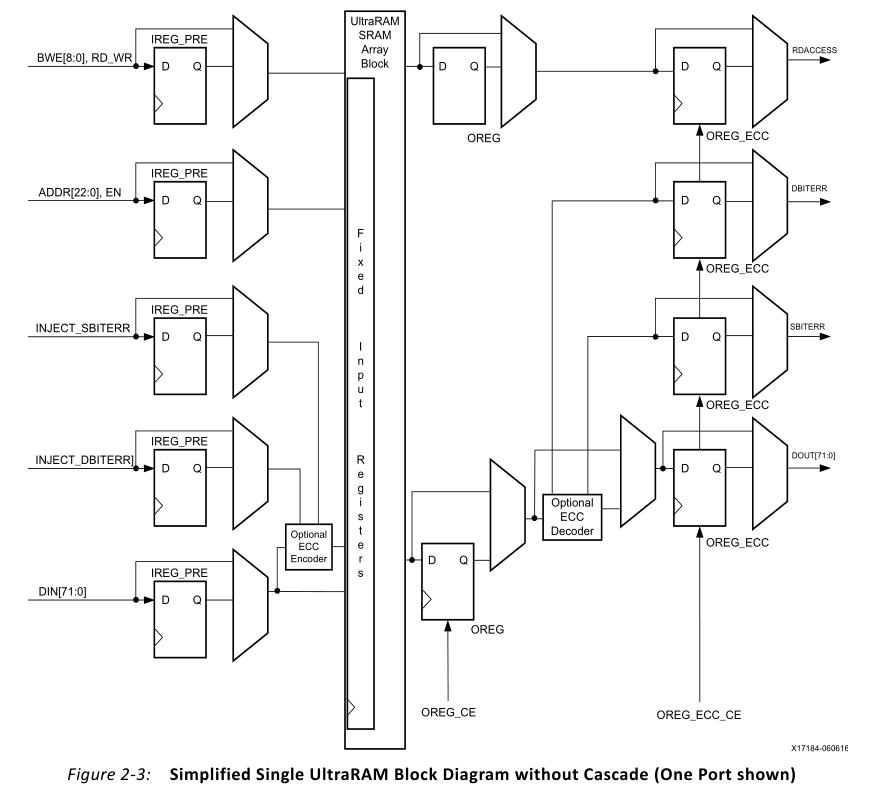

图 2-3 描述了简化的单个 UltraRAM 框图,没有级联,显示了一个端口。

UltraRAM 端口名称和说明

无级联端口

| PORT NAME | DESCRIPTION | 描述 |

| CLK | UltraRAM clock source. | |

| SLEEP | Dynamic power gating control. | 动态电源门控。 |

| Port A Inputs | ||

| ADDR_A[22:0] | Port A address. ADDR_A[22:12] are only used in cascade mode. | 端口 A 地址。 ADDR_A[22:12] 仅用于级联模式。 |

| EN_A | Port A enable. Enables or disables the read/write access to the block RAM memory core. |

端口 A 使能。启用或禁用对块 RAM 存储器内核的读/写访问。 |

| RDB_WR_A | Port A read or write mode input select. Read (BAR) is active Low (0 = read and 1 = write). |

端口 A 读或写模式输入选择。读取 (BAR) 低电平有效(0 = 读取,1 = 写入)。 |

| BWE_A[8:0] | Port A byte write enable. | 端口 A 字节写使能。 |

| DIN_A[71:0] | Port A write data in. | 端口 A 写入数据。 |

| INJECT_SBITERR_A | Port A single-bit error injection during write. | 端口 A 写入期间的单位错误注入。 |

| INJECT_DBITERR_A | Port A double-bit error injection during write. | 端口 A 写入期间的双位错误注入。 |

| OREG_CE_A | Port A SRAM array core block read output pipeline register CLK enable. | 端口 A SRAM 阵列核心块读取输出流水线寄存器CLK 使能。 |

| OREG_ECC_CE_A | Port A ECC decoder output pipeline register CLK enable. | 端口 A ECC解码器输出流水线寄存器CLK使能。 |

| RST_A | Asynchronous or synchronous reset for port A output registers. Reset has priority over CE. |

端口 A 输出寄存器的异步或同步复位。复位优先于 CE。 |

| Port A Outputs | ||

| DOUT_A[71:0] | Port A read data out. | |

|

RDACCESS_A |

Port A read status output | 端口 A 读取状态输出。 |

| SBITERR_A | Port A single-bit error output status. | 端口单位错误输出状态。 |

| DBITERR_A | Port A double-bit error output status. | 端口 A 双位错误输出状态。 |

| Port B Inputs | ||

| ADDR_B[22:0] | Port B address. ADDR_B[22:12] are only used in cascade mode. | |

| EN_B |

Port B enable. Enables or disables the read/write access to the block RAM |

|

| BWE_B[8:0] | Port B byte write enable. | |

| DIN_B[71:0] | Port B write data in. | |

| INJECT_SBITERR_B | Port B single-bit error injection during write. | |

| INJECT_DBITERR_B | Port B double-bit error injection during write. | |

| OREG_CE_B | Port B SRAM array core block read output pipeline register CLK enable. | |

| OREG_ECC_CE_B | Port B ECC decoder output pipeline register CLK enable. | |

| RST_B |

Asynchronous or synchronous reset for port B output registers. Reset has |

|

| Port B Outputs | ||

|

DOUT_B[71:0] |

Port B read data out. | |

| RDACCESS_B | Port B read status output. | |

| SBITERR_B | Port B single-bit error output status. | |

| DBITERR_B | Port B double-bit error output status. |

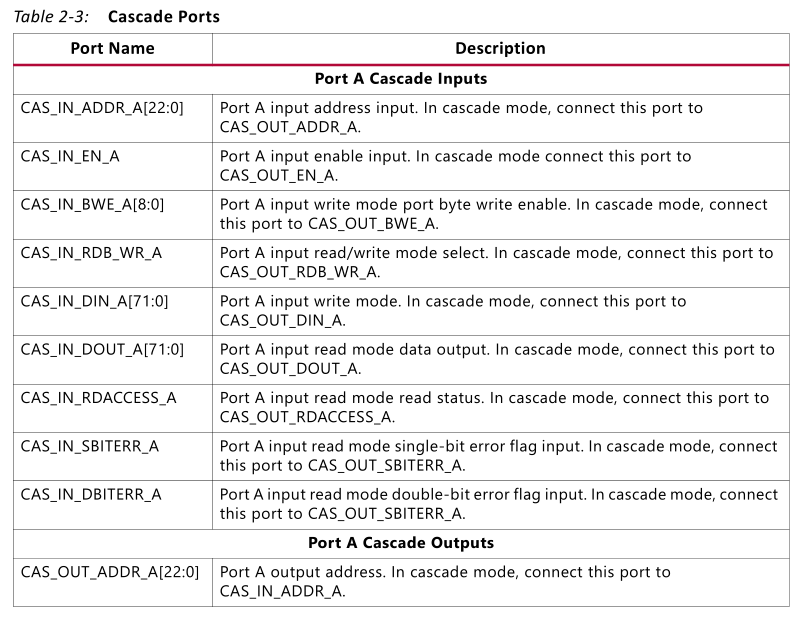

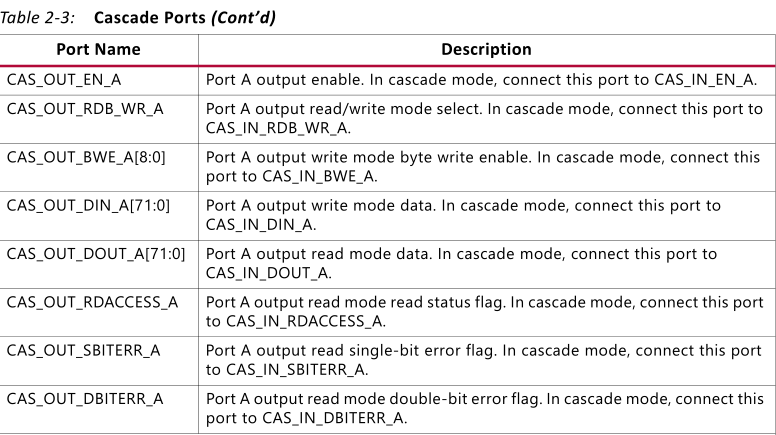

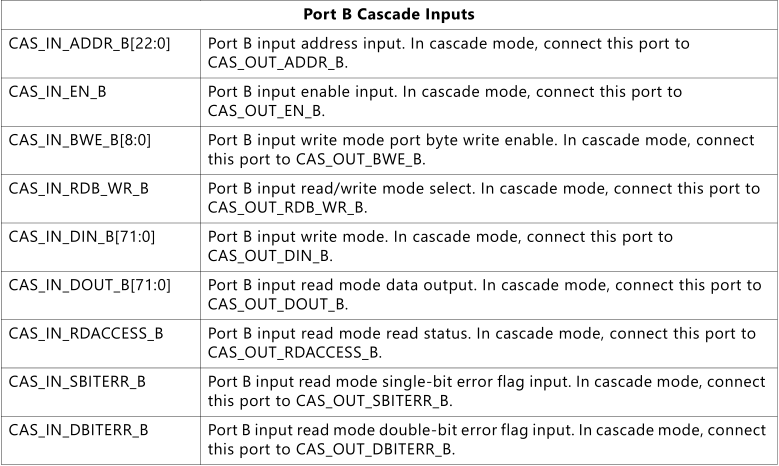

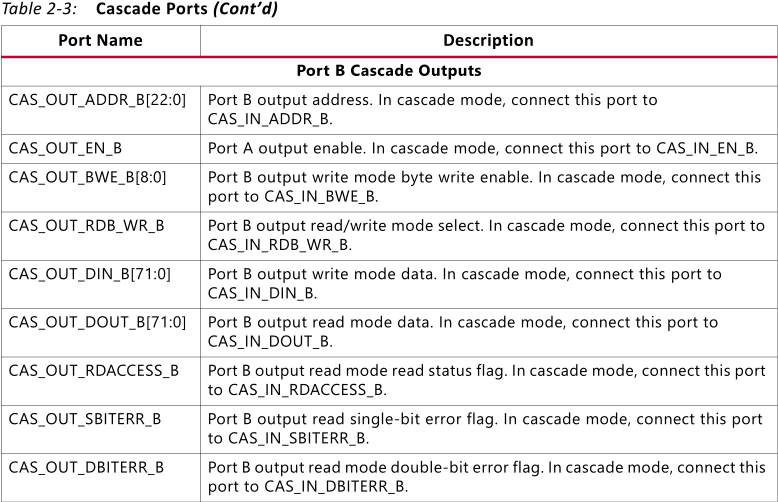

级联端口

UltraRAM Port Signals

时钟 – CLK

每个端口都与两个端口的单个时钟引脚完全同步。所有端口输入引脚的设置时间均参考该 CLK 引脚。输出数据总线有一个以 CLK 引脚为参考的时钟到输出时间。时钟极性是可配置的(默认为上升沿)。

电源门控使能输入——休眠

当内存长时间未被有效使用时,动态电源门控功能可用于节省静态功耗。

当睡眠模式有效,并且设置和保持时间满足时,存储器在下一个时钟周期开始进入睡眠模式。 SLEEP 输入禁用 UltraRAM 读写操作。因此,如果尝试读取或写入操作,它将被忽略,直到满足唤醒时间。但是,必须满足建立时间和保持时间。在睡眠模式下,SRAM 阵列的输出和 OREG 流水线寄存器在下一个时钟上升沿同步复位为“0”。其他可选的流水线寄存器不受睡眠模式的影响。因此,根据其他流水线寄存器的使用情况,UltraRAM 的最终数据输出值要么保持其先前的值,要么似乎重置为“0”。 OREG 寄存器的输出保持为“0”,直到第一个有效读取数据(在唤醒时间之后)流过流水线。

SLEEP 引脚控制 RAM 的电源门控。当 SLEEP = 1 时,SRAM 外设逻辑断电以节省能源。 SRAM 阵列中的数据会保留,但无法读取或写入。 SLEEP 允许两个时钟周期的唤醒时间,而不会影响 SEU 性能。该引脚的极性不可配置(高电平有效)。

唤醒时间定义了在 SLEEP 无效后 EN 引脚何时有效。

前面提到的时钟唤醒周期假设没有启用可选的流水线。

警告!如果使用 OREG (OREG=TRUE) 并且读取操作之后紧接着是 SLEEP 操作(SLEEP 变为活动状态),则读取操作数据不会退出 UltraRAM 块,因为 OREG 流水线级会立即断电。尽管在输出端未观察到数据,但 RDACCESS 信号仍然有效。

地址总线——ADDR_A、ADDR_B

23 位地址总线选择要读取或写入的存储单元。低 12 位用于选择每个 UltraRAM 中 4K 位置内的存储单元。高 11 位选择 UltraRAM,用于级联多个 UltraRAM 组成深存储器阵列。每个 UltraRAM 都有一个内置的比较器,它将高 11 位地址与唯一的 SELF_ADDR 属性进行比较,以识别 UltraRAM 是否已被选中。 SELF_MASK 属性定义 11 位地址中有多少应该用于比较。

使能——EN_A 和 EN_B

使能引脚影响端口的读写功能。具有无效使能引脚的端口将输出引脚保持在先前的状态,并且不会将数据写入存储单元。使能极性可反转(默认为高电平有效)。但是,在复位或省电模式(睡眠)期间,输出复位为“0”。

读/写选择——RDB_WR_A 和RDB_WR_B

当该引脚为“1”时,它选择写操作,当它为“0”时,它选择读操作。极性是可逆的。每个端口在一个周期内只能执行一次读或写操作。执行写入操作时,读取输出保持先前的值。

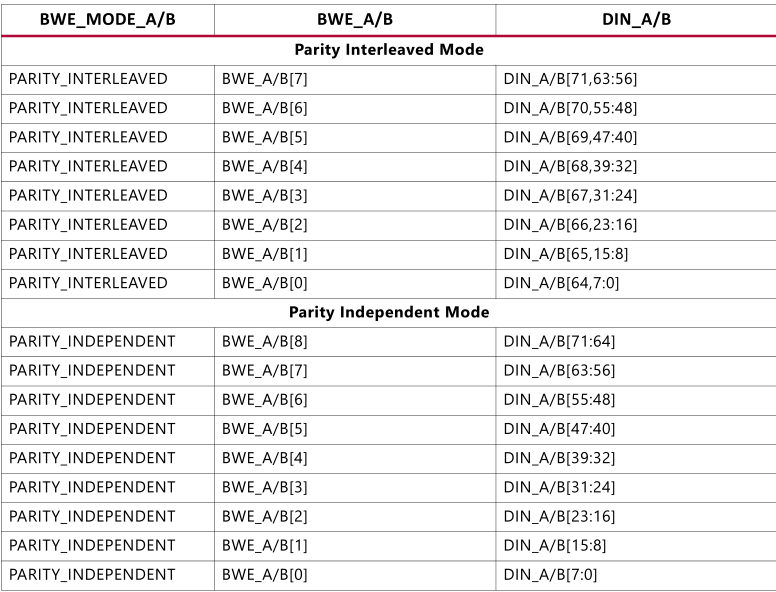

字节宽写使能——BWE_A、BWE_B

字节宽写使能 (BWE) 是一个 9 位总线。根据 BWE_MODE_A/B 属性设置,可能不会使用位 9 (BWE[8])。在 PARITY_INTERLEAVED 模式下,仅使用八个最低有效位。每个 DIN 字节 0-7 的单个奇偶校验位对应于并写入 DIN 总线 MSB 中的相关奇偶校验位。此模式支持自定义奇偶校验方案。在 PARITY_INDEPENDENT 模式下,九个 BWE 位对应于 DIN 总线的一个字节。表 2 - 4 详细说明了如何在写操作期间使用 BWE_A/B 位启用相应的 DIN 位。字节写使能输入在读操作期间被忽略。

Table 2‐4: Byte Write Enable (URAM288)

数据输入总线——DIN_A、DIN_B

数据输入总线提供要写入 UltraRAM 的新数据值。数据总线为 72 位宽,低 64 位用于数据,高 8 位用于奇偶校验或常规数据输入。

注入单位和双位错误输入——INJECT_SBITERR_A、INJECT_DBITERR_A、INJECT_SBITERR_B、INJECT_DBITERR_B

出于测试目的,注入错误输入可以在写入数据输入上引发单位或双位错误。

OREG 流水线阶段的寄存器使能 – OREG_CE_A、OREG_CE_B

该寄存器使能引脚控制第一个可选输出寄存器。当使用 OREG_A/B 属性启用此寄存器且相应的 CE 输入为高电平时,读取数据将在时钟上升沿存储在寄存器中。 CE 输入的极性不可配置(高电平有效)。

OREG_ECC 流水线阶段的寄存器启用 – OREG_ECC_CE_A、OREG_ECC_CE_B

该寄存器启用引脚控制 ECC 可选输出寄存器。当使用 OREG_ECC_A/B 属性启用此寄存器且相应的 CE 输入为高电平时,读取数据将在时钟上升沿存储在寄存器中。 CE 输入的极性不可配置(高电平有效)。

复位——RST_A、RST_B

复位操作有两种模式。同步和异步复位模式由 RST_MODE_A/B 属性控制。在默认的同步复位模式下,所有输出触发器和锁存器都同步复位为“0”。在异步复位模式下,所有输出触发器和锁存器都复位为“0”,无需等待 CLK 边沿。此操作不会影响 UltraRAM 存储单元,也不会干扰任一端口上的写操作。两个信号的极性都是可配置的(默认为高电平有效)。

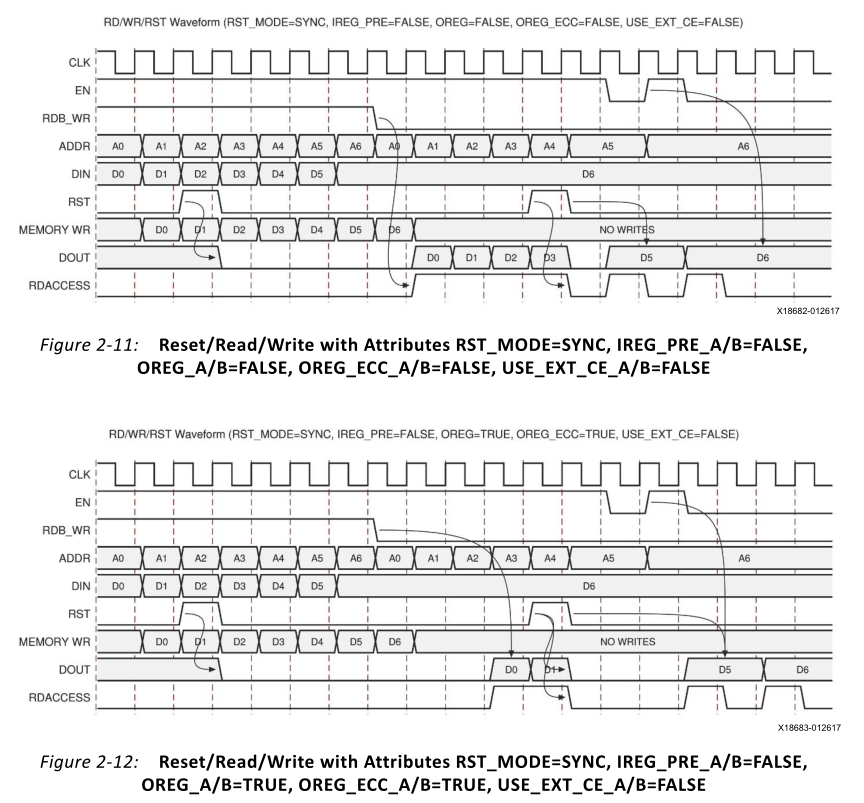

在 UltraRAM 矩阵中使用时,RST 输入预计会在矩阵中所有 UltraRAM 的输入端同时有效(和无效)(在 SYNC 和 ASYNC 复位模式下)。因此,在 RST 操作之后,新的读取数据在 N 个周期后可用(其中 N 是矩阵的读取延迟)。但是,如果读取操作与复位操作重叠,则 DOUT 可能会在 N 个周期之前从复位值变为新的读取值。发生这种情况是因为与复位期间或之前的读取相对应的读取输出可能会传播到输出(因为输入管道 IREG_PRE/IREG_CAS 不受复位影响)。因此,此行为还取决于矩阵中的 REG_CAS 位置。当 REG_CAS 位置改变时,复位后的 DOUT 行为可能不同。有关显示这种行为差异示例的时序图,请参见带复位的读/写波形 — 带和不带可选输出流水线寄存器中的图 2-11 和图 2-12。

重要提示:当处于异步复位模式时,UltraRAM 在此输入端没有任何内置同步器用于反断言边沿。级联 UltraRAM 用例需要一个通用同步器(通常在层次结构的上层实现)。结构中的输入在提供给 UltraRAM 之前必须正确同步。

数据输出总线——DOUT_A、DOUT_B

数据输出总线反映了在读取操作期间地址总线在最后一个有效时钟边沿引用的存储单元的内容。在写入操作或无操作期间,数据输出总线不会更改,并且会保留前一个周期的数据。这适用于单个 UltraRAM 和级联/矩阵配置。与级联 UltraRAM 类似,级联链末端(出口点)的读取输出也保存先前的数据。数据总线为 72 位宽,低 64 位用于数据,高 8 位用于奇偶校验或作为常规数据输出。

读取状态输出——RDACCESS_A、RDACCESS_B

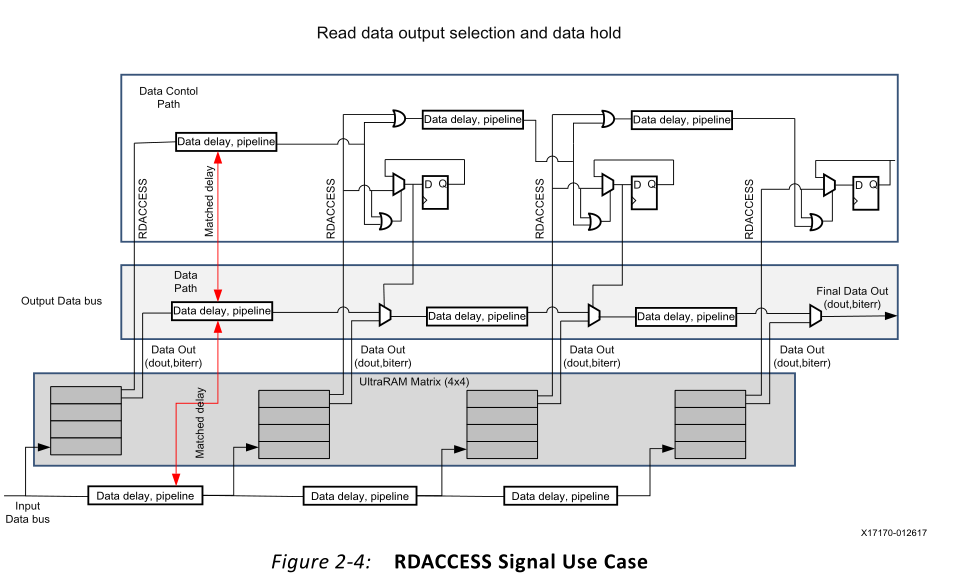

UltraRAM 生成读取访问状态输出 (RDACCESS_A/B) 以指示读取操作已完成执行,指示新数据何时可用于输出。此输出与相应的读取数据具有相同的延迟。当跨多列级联 UltraRAM 时,可以在顶层使用此输出来选择正确的读取数据。当此输出为高电平时,表示已在该 UltraRAM 或其下方属于级联链的 UltraRAM 中执行了读取操作。当跨越级联 UltraRAM 的列时,可能需要 CLB 寄存器来说明列级联中的流水线。

RDACCESS 信号的主要目的是支持以矩阵方式排列的 UltraRAM。它识别矩阵配置中的哪个 UltraRAM 块正在给定时钟周期内主动读取数据。然后,应用程序可以确定需要传播到最终输出以进行处理的适当读取数据。

图 2-4 说明了一个用例,其中 RDACCESS 信号用于选择正确的读取输出数据并控制矩阵的输出数据路径。该电路保存非活动输出的数据。将矩阵入口点之间的输入延迟(例如,出于性能原因的结构中的水平流水线)与输出端的相同延迟(图 2-4 中显示的延迟/流水线块)相匹配非常重要。

ECC 错误位输出——SBITERR_A、DBITERR_A、SBITERR_B、DBITERR_B

当 EN_ECC_RD_A/B 属性设置为 TRUE 时,ECC 错误位输出有效。当 ECC 解码器识别出单个位错误或双位错误时,这些输出被置位。

可反转控制信号引脚

五个控制引脚 CLK、EN_A/B、RST_A/B 各有一个单独的反转选项。 EN 和 RST 控制信号可以配置为高电平有效或低电平有效,并且时钟可以在上升沿或下降沿有效(默认为上升沿有效高电平),而无需其他逻辑资源。

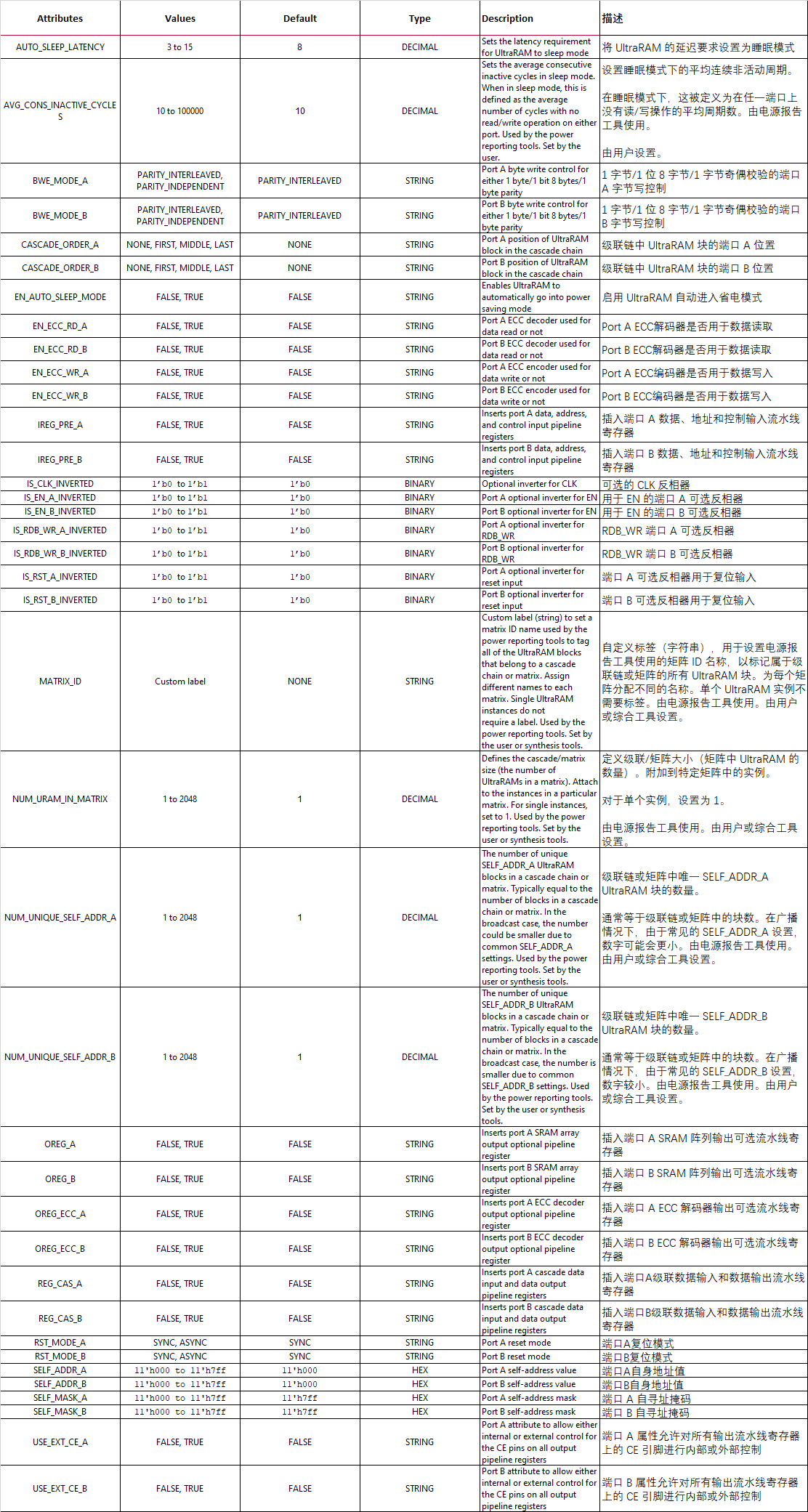

UltraRAM Attributes

注意:URAM288_BASE 原语没有任何级联属性。

自动睡眠延迟——AUTO_SLEEP_LATENCY

自动睡眠模式以自动方式自动利用sleep引脚提供的功能。为了确定何时进入睡眠状态以及何时醒来,UltraRAM会提前进行RAM访问。

当 EN_AUTO_SLEEP_MODE 属性设置为 TRUE 时,AUTO_SLEEP_LATENCY 属性定义使能和全局地址输入 EN_A、EN_B、ADDR_A[22:12] 和 ADDR_B[22:12] 必须先于其他输入到达的时钟周期数。该前瞻信息用于决定 UltraRAM 何时可以进入休眠状态。 EN_A/B 和 ADDR_A/B[22:12] 被内部延迟以实现此功能。启用和全局地址信号提前到达所需的时钟周期数通过 AUTO_SLEEP_LATENCY 属性设置,该属性可以取 3 – 15 之间的值。因此,要使 UltraRAM 进入睡眠模式,连续不活动时钟的最小数量周期是必需的,它由 AUTO_SLEEP_LATENCY 属性的值定义。

实现的睡眠周期数使用以下公式计算:

- 如果连续非活动周期数 < AUTO_SLEEP_LATENCY,则睡眠周期数 = 0。

- 如果连续非活动周期数 >= AUTO_SLEEP_LATENCY,则连续睡眠周期数 = 连续非活动周期数 – 3。

- 非活动周期定义为任一端口均无RD/WR 操作的周期。

例如,要获得任意五个或更多连续不活动周期的睡眠周期,请将 AUTO_SLEEP_LATENCY 设置为 5。

一旦进入自动休眠模式,OREG 的输出将仅在一个时钟周期内保留旧值。根据 UltraRAM 何时进入睡眠模式,数据可以在下一个周期或更晚的时间重置为“0”。如果在 OREG 之后没有启用其他流水线寄存器,则设计必须仅在最后一个有效时钟周期内使用寄存器输出读取数据。如果还有其他连续的流水线寄存器,那么这些流水线寄存器将保存最后读取的数据。

自动休眠模式对于大型链条或任何活动很少的链条最有效。虽然此属性有默认值,但应用程序会根据应用程序的活动、延迟和其他需求来确定此功能的有效节能效果。

如果 AUTO_SLEEP_LATENCY 太低,UltraRAM 会过于频繁地进入睡眠和唤醒,这会导致消耗更多功率。如果太高,则可能无法保存最大电量。

字节写入启用模式-BWE_MODE_[A|B]

此属性确定字节写入启用(BWE_[A/B])输入的数据和奇偶校验使用。要么选择1个数据字节\1个奇偶校验位模式(PERIFICATY_INSERVILED),要么选择8个数据字节/1个奇偶校验字节模式(PARCHAY_INTERNAL)。有关更多信息,请参见字节范围写入启用-BWE_A、BWE_B。

CASCADE CHAIN ORDER-CASCADE_ORDER_[A|B]

此属性指示UltraRAM是否为级联的一部分,以及UltraRAM在级联链中的位置。值为None(默认)、First、Medium和Last。应将每列中第一个的所有UltraRAM设置为第一个,将每列中最后一个的所有UltraRAM设置为最后。介于两者之间的所有UltraRam必须设置为中间。

有关详细信息,请参阅级联用户属性。

AVG_CONS_INACTIVE_CLOLES、MATRIX_ID、NUM_URAM_IN_MATRIX和NUM_UNIQUE_SELF_ADDR_A|B

属性这些属性对设计没有功能影响,用于功率估计和功率报告。当通过合成推断UltraRam时,Vivado工具会自动设置这些属性。

建议:手动实例化时,应设置属性以反映准确功率计算的实际使用情况。如果不设定,电力估计将是悲观的。

注意:在广播用例中,SELF_MASK设置会影响NUM_UNIQUE_SELF属性。

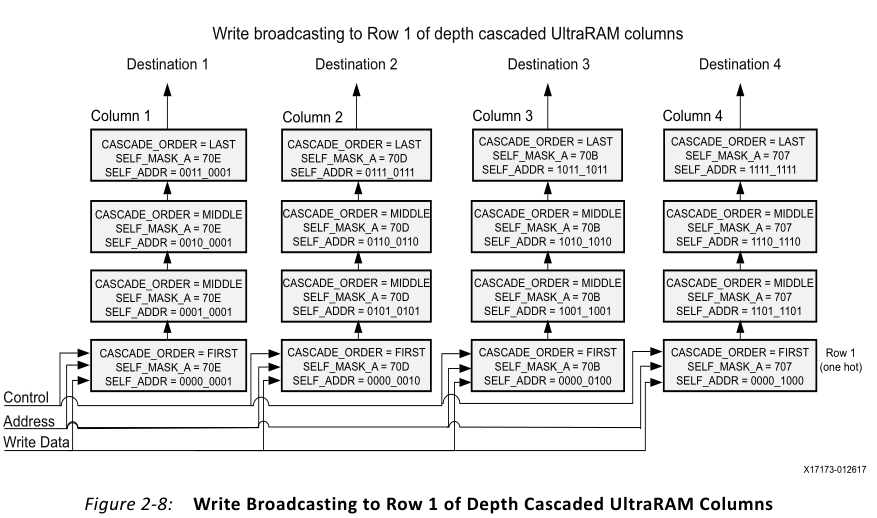

虽然矩阵中的UltraRAM实例上的ADDR_A/B[22:12]输入可能不同,但SELF_MASK设置可能会导致矩阵中的多个实例匹配。参见图2-8所示的示例。

设置启用自动休眠模式-EN_AUTO_SLEEP_MODE

此模式启用自动休眠模式以实现自动节能,并覆盖应用程序对休眠模式的控制。设置为TRUE时,禁用用户控制的休眠输入。相反,UltraRAM在内部将自身置于和退出休眠模式,以实现自动节能。UltraRAM进入和退出休眠模式的标准是由AUTO_SLEEP_THELLAY属性确定的非活动时钟周期的度量。

注意:在AUTO_SLEEP模式下不允许使用USE_EXT_CE_A/B。不允许这两个属性同时为真。

Enable ECC WRITE-EN_ECC_WR_[A/B]

此属性确定是否启用ECC编码器(WRITE)。

Enable ECC Read-en_ECC_RD_[A/B]

此属性确定是否启用ECC解码器(读取)。

可选输入寄存器阶段-IREG_PRE_[A|B]

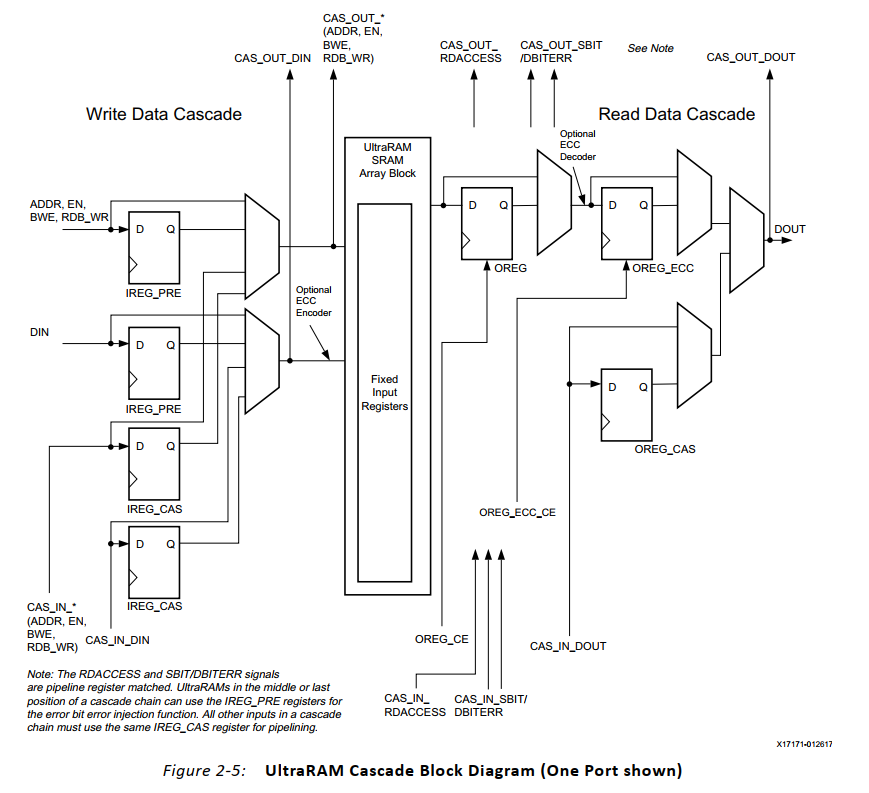

此属性确定EN/RDB_WR/BWE/ADDR/DIN/INJECT_SBITERR/INJECT_DBITERR UltraRAM输入是否启用了各自的输入流水线寄存器。除可选级联寄存器阶段-REG_CAS_[A|B]另有说明外,IREG_PRE和REG_CAS是互斥的。参见图2-5。

可选输出寄存器阶段-OREG_[A|B]

此属性确定SRAM阵列输出是否启用了流水线阶段。

可选ECC输出寄存器阶段-OREG_ECC_[A|B]

此属性确定ECC解码逻辑的ECC错误和数据输出是否启用了流水线寄存器。

可选级联寄存器阶段-REG_CAS_[A|B]

确定级联数据/控制/地址输入和输出是否启用其流水线寄存器(IREG_CAS和OREG_CAS)。这些流水线阶段在确定UltraRAM的最大频率方面起着关键作用。在级联模式下,这些寄存器应在每个模块或每隔几个模块中使用,具体取决于最大频率要求。IREG_PRE和REG_CAS是互斥的,除非CASCADE_ORDER属性设置为MEDER或LAST,否则IREG_PRE寄存器仍可用于错误注入输入INJECT_S/DBITERR的级联情况。对于所有其他输入,必须使用REG_CAS。参见图2-5。

重置模式-RST_MODE_[A|B]

确定RST_[A/B]是CLK的同步输入还是异步输入。

Self Address-SELF_ADDR_[A|B]

此属性确定UltraRAM的自身地址,并且对于级联链中的每个UltraRAM必须是唯一的值。这决定了级联链中每个UltraRAM的地址。它是一个11位的值,可以是11‘h000到11’h7ff之间的任何值。有关详细信息,请参阅级联用户属性。

自屏蔽值-SELF_MASK_[A|B]

此属性确定级联地址(SELF_ADDR)中的多少位用于与ADDR输入进行比较(地址解码),以确定输入地址是否与级联链中的UltraRAM匹配。地址位数由级联UltraRAM中的总地址空间决定。对应于未使用的地址位的MSB位应设置为\“1\”。有关详细信息,请参阅级联用户属性。

外部CE用法-USE_EXT_CE_[A|B]

此属性允许使用外部CE输入以非级联模式控制所有输出流水线阶段。默认情况下,设计使用内部生成的CE来控制所有流水线阶段。这不适用于OREG_CAS寄存器使能。在级联模式下,OREG_CAS寄存器使能由UltraRAM自动控制。启用外部CE模式时,不允许使用RDACCESS输出信号。

重要提示:在级联模式下,不能使用USE_EXT_CE,应将其设置为FALSE。因此,在级联模式下,不能使用外部CE输入(OREG_CE和OREG_ECC_CE)。仅当CASCADE_ORDER=NONE时才支持此属性。

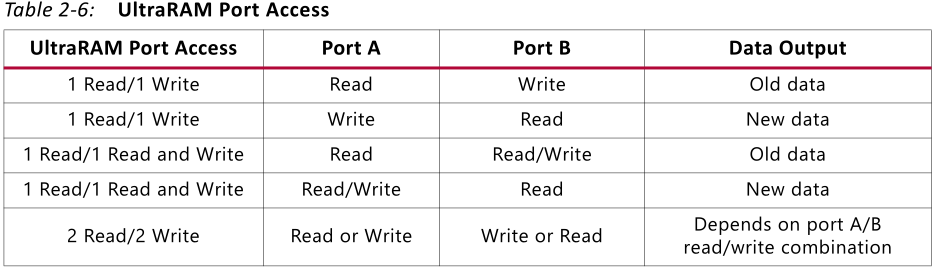

双端口SRAM阵列操作

双端口288 KB UltraRAM由一个288 KB存储区域和两个独立的访问端口A和B组成。这两个端口共享一个时钟输入。

在每个时钟周期中,每个端口可以独立于另一个端口执行读或写操作。这两个端口中的任何一个端口都允许任意读/写组合。读写操作始终与时钟同步。在同一时钟周期内,总是先执行端口A的操作,然后执行端口B的操作。

因此,当两个端口访问相同的地址位置时,不可能发生数据访问冲突。每个端口都有自己的地址、数据输入、数据输出、使能和写入使能。

- 如果两个端口对同一地址执行读写操作,则行为定义如下(请参见Table 2-6):

- 如果端口A正在写入,则端口B正在读取,则端口B读取新数据。

- 如果端口A在读取,端口B在写入,则端口A读取旧数据。

- 如果端口A和B正在写入,则端口B写入将覆盖端口A写入。在时钟周期结束时,存储器存储端口B写入数据。

读取操作

在默认模式下,在未启用可选流水线寄存器的情况下,读取操作使用一个时钟沿。读地址在读端口上注册,存储的数据在SRAM访问时间之后被加载到输出锁存器中。当使用额外的可选输入/输出寄存器时,读取操作需要额外的周期,具体取决于使用的流水线寄存器的数量。在下一次有效的读操作或重置操作更改输出之前,读数据一直保存在输出上。

写操作

除非使能可选输入寄存器,否则写操作是单时钟沿操作。写入地址注册在写入端口上,输入的数据存储在存储器中。除非重置输入被断言,否则读输出在写操作期间保持先前的值。

可选输入寄存器

可选数据、地址和控制输入寄存器(IREG_PRE寄存器)通过消除用于流水线操作的CLB触发器的布线延迟来提高设计性能。提供用于级联数据、地址和控制的可选输入寄存器(IREG_CAS寄存器)。数据输入或级联输入寄存器可在任何给定时间用于UltraRAM块,具体取决于其配置(输入级联或非级联)。

输入和输出级联寄存器均通过REG_CAS属性同时使能,不能单独开启或关闭。

可选输出寄存器

可选输出寄存器通过消除用于流水线操作的CLB触发器的布线延迟来提高设计性能。第一个可选输出寄存器(OREG级)紧接在SRAM阵列读取操作之后。ECC解码逻辑(OREG_ECC阶段)和级联逻辑(OREG_CAS寄存器)之后的附加可选输出寄存器可用。默认情况下,该设计使用内部生成的CE来控制所有流水线级以实现省电。但是,可以通过设置USE_EXT_CE_A/B属性来使用外部CE端口。当外部CE使能时,将为这些输出寄存器提供独立的时钟使能输入端口。如果输出数据寄存器通过其CE端口禁用,则它们保持其值不受输入寄存器操作的影响。

重置操作

UltraRAM RST操作同时重置读取数据/状态/ECC错误输出和所有相应的可选输出/级联流水线寄存器。根据RST_MODE属性设置,重置功能可以是同步的(默认)或异步的。

重置操作优先于任何读取操作和任何CE输入。在取消断言RST之后,重置值一直有效,直到新的读取数据值流经流水线。

当处于异步重置模式时,UltraRAM在此输入上没有任何内置同步器用于解除断言。因此,RST输入可能需要基于逻辑的同步器。

重要提示:如果设计使用级联,则应对链中的所有UltraRAM RST使用通用同步器。

字节写入启用功能

字节写入启用功能允许将单字节的输入数据写入SRAM阵列。每个端口A和端口B都有9位写使能输入。BWE_MODE_[A/B]属性可选择两种工作模式。在奇偶校验_交织模式下,每个写使能位启用8个数据位加上1个奇偶校验位。因此,每个字节都有对应的单个奇偶校验位。在独立奇偶模式下,每个写使能位(BWE[7:0]使能8个数据位(一个字节)。BWE位编号9(BWE[8])使能位控制八个奇偶校验位中的一个字节。在读取操作期间,字节写入输入被忽略。

重要提示:如果使用ECC功能,则必须将所有字节写入启用位设置为\“1\”,以使ECC编码器/解码器正常运行。

级联UltraRAM和矩阵配置

UltraRAM的高级内置功能之一是能够通过专用的直接互连在单列中直接级联UltraRAM块来构建更深的RAM。用于数据输入、数据输出、ECC错误、地址、启用、读/写选择和写屏蔽属性的端口有助于级联(参见图2-5)。

级联仅在一个方向上受支持,并且始终采用自下而上的方式。

UltraRAM块可以在SLR内的单个列中无限制地级联,并且具有内置连接。级联流水线寄存器(IREG_CAS和OREG_CAS级由REG_CAS属性启用)是每个UltraRAM中的可用选项。根据设计的最大频率和延迟要求,可以根据需要启用这些寄存器。从上面的一个时钟区域到下一个时钟区域的级联可能需要在级联链的输入和输出侧都有额外的流水线寄存器,以避免潜在的设置时间冲突。

跨不同列的级联UltraRAM可以使用逻辑和路由资源来实现。UltraRAM生成读访问状态输出RDACCESS_A/B以指示已执行读操作。此输出具有与相应读取数据相同的延迟,并且在使用多列进行级联时可用于确定正确的读取数据。

如果没有正在执行的读操作,级联链末端(在块出口点)的读输出将保存先前的数据。

级联用户属性

- CASCADE_ORDER_A/B确定UltraRAM块级联顺序。

- None(默认)-UltraRAM未处于级联模式。

- First-UltraRAM是链中每列的级联链中的第一个实例。

- Medium-UltraRAM是级联链中的中间实例。

- LAST-UltraRAM是链中每列的级联链中的最后一个实例。

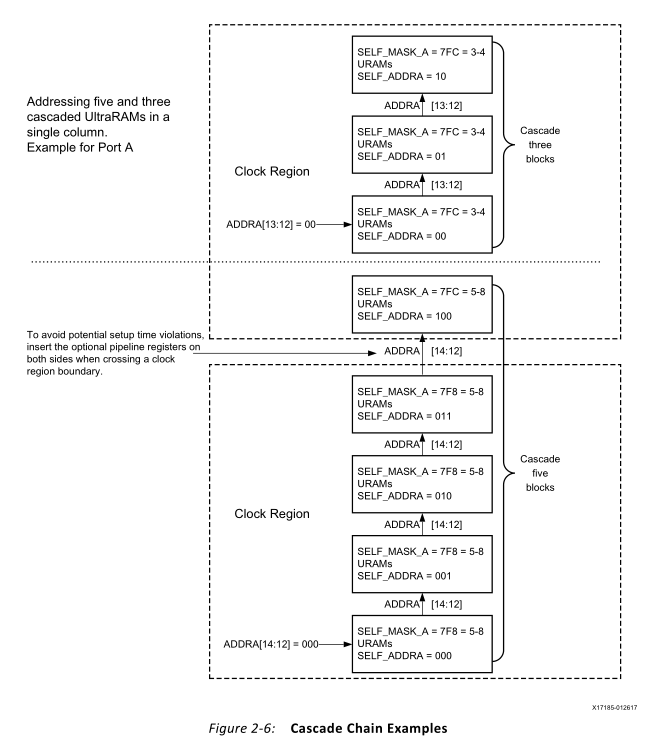

- SELF_MASK_A/B[22:12]确定级联链中的UltraRAM块数量,从而决定使用哪个ADDR_A/B[22:12]位。

- 11‘h7ff(默认)-未处于级联模式。ADDR_A/B[22:12]输入被屏蔽。

- 11‘h7fe-2 UltraRAM级联。ADDR_A/B[22:13]输入被屏蔽。

- 11‘h7fc-3-4 UltraRAM级联。ADDR_A/B[22:14]输入被屏蔽

- 11‘h7f8-5-8 UltraRAM级联。ADDR_A/B[22:15]输入被屏蔽。

- 11‘h7f0-9-16 UltraRAM级联。ADDR_A/B[22:16]输入被屏蔽。

- 11‘h7e0-17-32 UltraRAM级联。ADDR_A/B[22:17]输入被屏蔽。

- 11‘h7c0-31-64 UltraRAM级联。ADDR_A/B[22:18]输入被屏蔽。

- 11‘h780-65-128 UltraRAM级联。ADDR_A/B[22:19]输入被屏蔽。

- 11‘h700-129-256 UltraRAM级联。ADDR_A/B[22:20]输入被屏蔽。

- 11‘H600-257-512 UltraRAM级联。ADDR_A/B[22:21]输入被屏蔽。

- 11‘h400-513-1024 UltraRAM级联。Addr_A/B[22]输入被屏蔽。

- 11‘h000-1025-2048(1036)UltraRAM级联。所有地址输入都不会被屏蔽。

- SELF_ADDR_A/B[22:12]

- 该属性在级联模式下使用,必须根据UltraRAM级联链中的哪个地址位对其所连接的特定块进行设置。当使用具有SELF_MASK_A/B属性的地址位进行掩码并与使用的ADDR_A/B地址位匹配时,设置自地址位时,级联链中的特定UltraRAM块被访问。默认值为11‘H0。(图2-6)。

从级联UltraRAM构建矩阵

应用程序可以使用多个UltraRAM构建深层逻辑SRAM。这些UltraRAM实例形成一个矩阵,以便地址、控制信号和输入数据到达左下角的UltraRAM矩阵,输出数据显示在右上角。图2-7说明了UltraRAM矩阵背后的概念。在这个X×Y(行x列)矩阵中,每个矩阵元素都是垂直级联的单个UltraRAM块。读取/写入矩阵、地址、控制信号和输入数据(如果写入)进入行1中的UltraRAM矩阵。

写入操作将输入数据写入被寻址的UltraRAM块的行、列(R,C)位置和其中的字。类似地,对于读操作,输出数据通过选择UltraRAM R、C和其中的位置(始终)到达列顶部的输出总线。

图2-7显示了4x4 UltraRAM矩阵。

对于每个UltraRAM,使用单独的地址编码方案,每个块单独确定它是否应该有数据。SELF_ADDRESS和SELF_MASK允许矩阵中的非唯一地址,从而允许在同一周期内将数据同时广播到多个UltraRAM。SELF_ADDRESS可用作单热编码地址(甚至部分),而SELF_MASK确定哪些地址位重要,哪些地址位可以忽略(One-COLD)。因此,应用于矩阵中的所有UltraRAM的全局地址可以应用于一组预定的UltraRAM。图2-8说明了向第1行中的两个、更多或所有UltraRAM写入数据的多播写入。在此示例中,低四个块地址位通过必须同时接收数据的块的SELF_ADDR设置进行或运算,而SELF_MASK忽略块的不解码地址位。在此使用案例中,UltraRAM只能在1读/1写模式下使用。

地址位译码

- 行1多播

- ADDR15:12=0011多播到列1+2

- ADDR15:12=0101多播到列1+3

- ADDR15:12=0110多播到列2+3

- ADDR15:12=0111多播到列1+2+3

- ADDR15:12=1101多播到列1+2+4

- 等等。

- ADDR15:12=1111多播到第1+2+3+4列

- 行/列地址

- ADDR19:16=0001-0011第2,3,4行,第1列

- ADDR19:16=0101-0111第2,3,4行,第2列

- ADDR19:16=1001-1011第2,3,4行,第3列

- ADDR19:16=1101-1111第2,3,4行,第4列

Vivado Design Suite支持UltraScale+设备,该套件包括几个代码模板,以帮助确定可用的硅资源。使用UltraRAM存储器的RTL设计入口有三种方法:

- 从2016.1 Vivado工具版本开始使用Xilinx参数化宏(XPM)。

- 推断没有ECC的RTL内存,并使用设置为“Ultra”的ram_style属性。

- 实例化设备原语。

这些方法的示例在Vivado语言模板中,可以通过选择工具->语言模板从Vivado工具主菜单访问。

注:XPM是在高度定制化的情况下获得预期效果的最有效方法。《UltraScale架构库指南》(UG974)[参考文献3]中提供了详细信息。

内置错误检测和纠错

每个UltraRAM 4K x 72 RAM都为每个端口内置了可选的汉明码纠错功能。当ECC开启时,72位数据总线的高8位(MSB)用于奇偶校验。ECC操作对用户是透明的。在ECC模式下,所有字节写使能BWE_B[8:0]位必须设置为\“1\”(高),才能正常运行。端口A和端口B的ECC操作相同。

在每次写入操作期间生成8个保护位(ECCPARITY),并将其与64位数据一起存储到存储器中。这些ECCPARITY位在每次读取操作期间用于纠正任何单比特错误,或检测(但不纠正)任何双比特错误。

ECC数据位和状态/控制位与CLK同步。

在每次读取操作期间,从存储器读取72位数据(64位数据和8位奇偶校验),并将其提供给ECC解码器。ECC解码器生成两个状态输出(SBITERR_A/B和DBITERR_A/B),用于指示三种可能的读取结果:无错误、纠正单比特错误或检测到双比特错误。在标准ECC模式中,读操作不纠正存储器阵列中的错误。它只在DOUT上显示更正后的数据。为改进FMAX,提供了用于数据输出(DO)、SBITERR和DBITERR的可选寄存器。

如果RST_A/B被断言,则所有输出寄存器被重置为“0”。因此,SBITERR和DBITERR状态信号也被重置为“0”(低),表示数据输出没有单比特或双比特错误。

UltraRAM还可以在任一端口中插入错误。ECC模式可以在任意或所有字中注入单比特错误或双比特错误。当INJECT_SBITERR在写入周期期间被置位时,根据DIN[30]在存储器内部注入一位错误。

当INJECT_DBITERR在写入周期期间被置位时,双位错误被注入对应于DIN[30]和DIN[62]的存储器内部。如果在写入周期期间INJECT_SBITERR和INJECT_DBITERR均被置位,则在与INJECT_DBITERR相同的位置注入双位错误。

此功能在所有ECC模式中都可用。

ECC模式

在标准ECC模式(EN_ECC_RD=TRUE和EN_ECC_WR=TRUE)下,编码器和解码器均启用。在写入期间,64位数据和8位ECC生成的奇偶校验存储在阵列中。外部奇偶校验输入位被忽略。在读取过程中,读出72位解码数据和奇偶校验。

最常见的用例是在一个端口中同时启用ECC编码器和解码器。

但是,编码器和解码器可以单独启用。要仅启用编码器,必须通过DI端口发送数据,ECCPARITY位写入RAM,并且禁用解码器。如果只使用解码器,则会禁用编码器,将数据写入RAM,并从UltraRAM中读出校正后的数据和状态位。

ECC操作模式

有三种类型的ECC操作:

- 完全ECC模式

- ECC仅解码模式

- ECC仅编码模式

标准ECC模式同时使用编码器和解码器。

标准ECC

设置属性

EN_ECC_RD=TRUE

EN_ECC_WR=TRUE

标准ECC写入

ECC编码器使用DIN[63:0]生成相应的8位ECC奇偶校验,将其附加到64个数据位,然后写入存储器。由于ECC奇偶校验是在内部产生的,因此不使用DIN[71:64]引脚。

对于所有输入引脚,在ECC编码逻辑之前提供了IREG_PRE可选流水线阶段。可以根据需要启用此阶段,以满足最高频率要求。

标准ECC读取

在读取操作期间,从地址位置读出由64位数据和8位奇偶校验组成的72位存储器内容,并在内部进行解码。如果没有错误,原始数据和奇偶校验在DOUT[71:0]输出。如果数据或奇偶校验中存在一位错误,则纠正该错误,并且SBITERR为高电平。如果数据和奇偶校验中存在双比特错误,则不会纠正该错误。输出原始数据和奇偶校验,且DBITERR为高。

OREG可选流水线阶段正好在ECC解码逻辑之前可用,而OREG_ECC可选流水线阶段正好在ECC解码逻辑之后可用于所有DOUT和错误位输出。根据设计的最大频率和延迟要求,可以启用这两个阶段中的一个或两个。

仅ECC编码

设置属性

EN_ECC_RD=FALSE

EN_ECC_WR=TRUE

仅ECC编码写入

ECC编码器使用DIN[63:0]生成相应的8位ECC奇偶校验,将其附加到64个数据位,然后写入存储器。由于ECC奇偶校验是在内部产生的,因此不使用DIN[71:64]引脚。

对于所有输入引脚,在ECC编码逻辑之前提供了IREG_PRE可选流水线阶段。可以根据需要启用此阶段,以满足FMAX要求。

ECC编码只读

在ECC编码模式下,读取与正常块RAM读取相同。64位数据出现在DOUT[63:0],8位奇偶校验出现在DOUT[71:64]。不会进行单位纠错,并且永远不会断言错误标志SBITERR和DBITERR。

仅ECC解码

设置属性

EN_ECC_RD=TRUE

EN_ECC_WR=FALSE

在仅ECC解码模式中,仅启用ECC解码器。ECC编码器被禁用。

仅解码模式用于注入单比特或双比特错误,以测试ECC解码器的功能。ECC奇偶校验位必须使用DIN[71:64]引脚从外部提供。

仅使用ECC解码注入单位错误

DIN[71:0]并注入单比特错误写入存储器阵列。

- 当读出存储位置时,数据会根据需要进行修正。

- SBITERR与相应的DOUT数据对齐。

ECC解码器还纠正奇偶校验位中的单比特错误。

使用仅ECC译码注入双比特错误

- DIN[71:0]并注入双比特错误被写入存储器阵列。

- 访问存储位置时,会读出损坏的数据并检测到双位错误。

- DBITERR与相应的DOUT数据对齐。

ECC解码器还检测何时发生奇偶校验位中的双比特错误,以及何时发生数据比特中的单比特错误和相应奇偶校验位中的单比特错误。

UltraRAM时序图

本节描述和说明与UltraRAM块相关的时序。时序图显示了矩阵和单块配置中读/写/重置操作的行为,以及不同流水线选项和时钟使能功能的影响。休眠和自动休眠模式的详细时序图显示了各种流水线和延迟配置。

带和不带可选流水线寄存器的读/写波形

图2-9和图2-10显示了带和不带可选流水线寄存器的读/写波形。

带可选输出流水线寄存器和带可选输出流水线寄存器的读/写波形

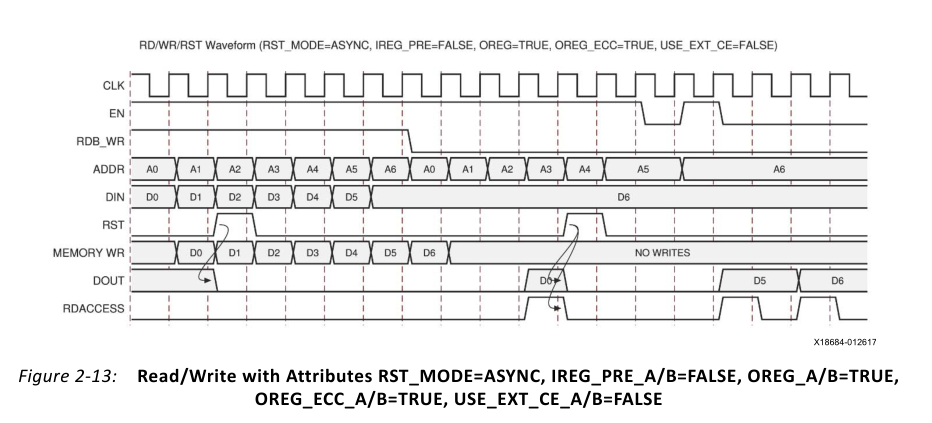

图2-11、图2-12和图2-13显示了带复位以及带和不带可选流水线寄存器的读/写波形。

注意:复位优先于读操作,复位对任何写操作没有影响。

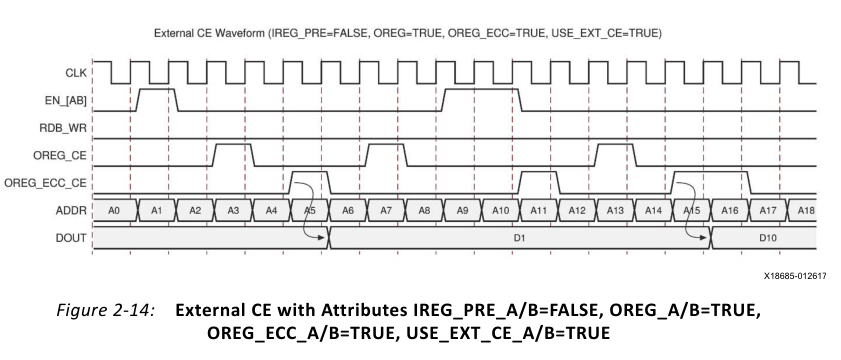

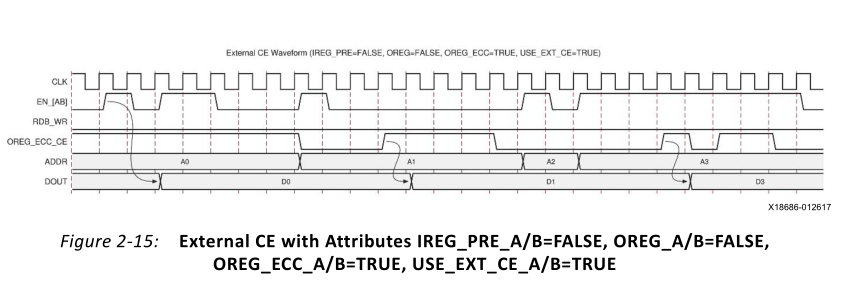

使用外部CE的读/写波形

图2-14和图2-15显示了使用外部CE的读/写波形。仅允许对单个UltraRAM模块使用外部CE,级联ultra ram不支持使用外部CE。

当USE_EXT_CE=TRUE时,不支持RDACCESS。

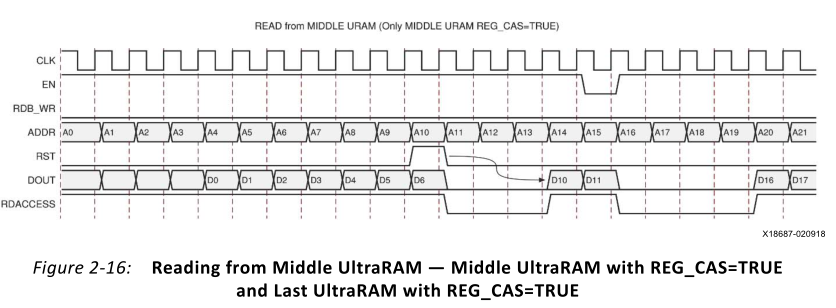

通过复位从矩阵波形中读取

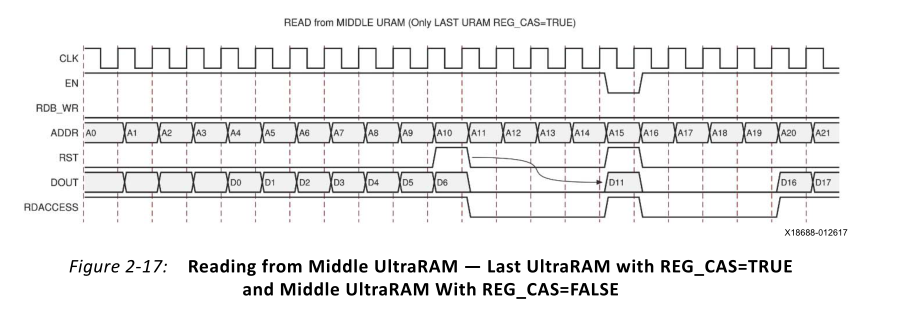

图2-16和图2-17中的波形适用于三个UltraRAM级联情况,并假设级联链中所有三个UltraRAM的OREG和OREG_ECC设置为TRUE:·

- RST输入在所有三个UltraRAM的输入端同时有效或无效。

- 所有其他输入在First UltraRAM的输入端驱动。所有输出都从最后一个UltraRAM退出。

注:重置后的DOUT输出行为可能因REG_CAS的位置不同而不同,如图2-16和图2-17所示。

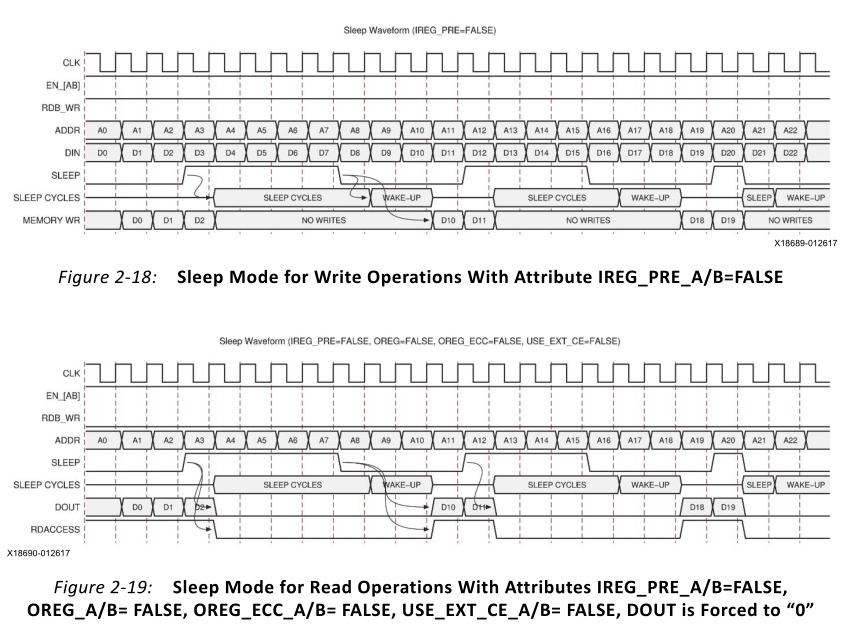

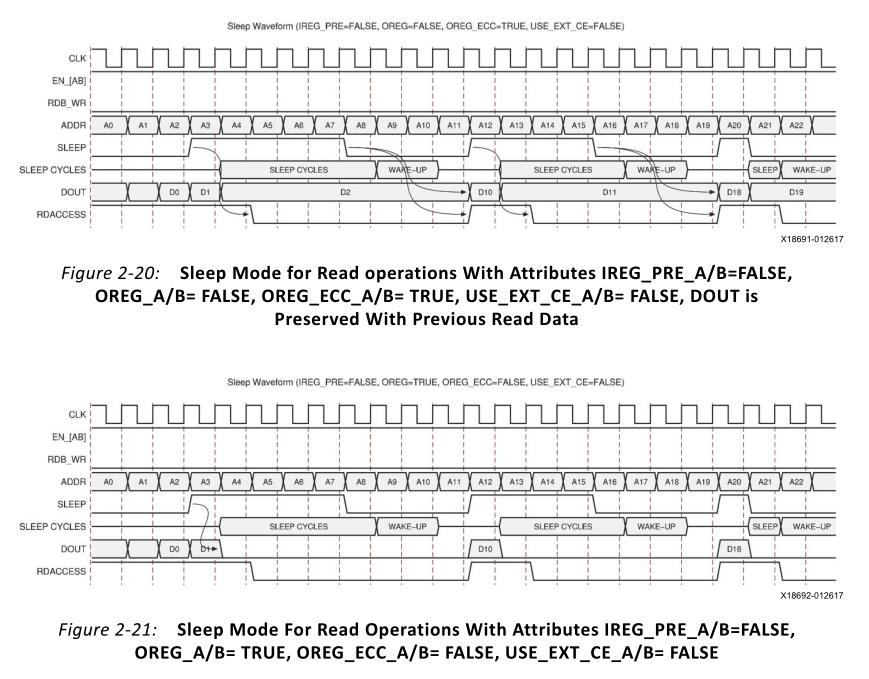

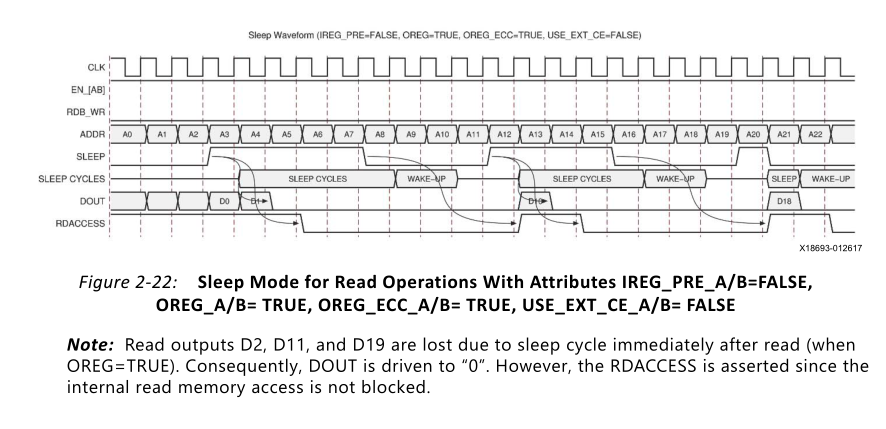

睡眠波形

睡眠优先于EN。任何尝试的内存写入都将被忽略,并保留以前的内存内容。任何尝试的内存读取也会被忽略。参见图2-18至图2-22。

注:读取输出D2、D11和D19在读取后立即由于休眠周期丢失(当OREG=TRUE时)。因此,DOUT被驱动到“0”。但是,由于内部读取存储器访问未被阻止,因此RDACCESS被断言。

当OREG=TRUE时,内部对应于地址A2的读取不会被阻止(因为在此周期中休眠仍然较低)。然而,由于休眠在下一个周期变为高电平,OREG丢失了数据,并且OREG的输出变为“0”。在这种情况下,即使OREG_ECC=TRUE,由于读取本身未被阻止,OREG_ECC将变为“0”,因为需要新的读取数据。如果在OREG=TRUE(无论OREG_ECC为TRUE或FALSE)的情况下立即执行读取操作并进入睡眠状态,则会发生这种情况。

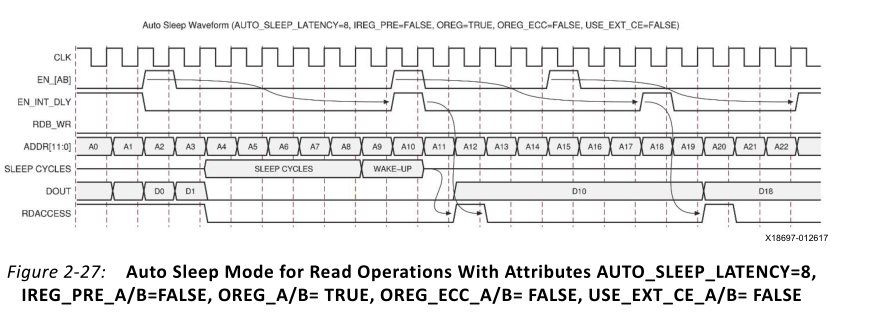

自动休眠波形

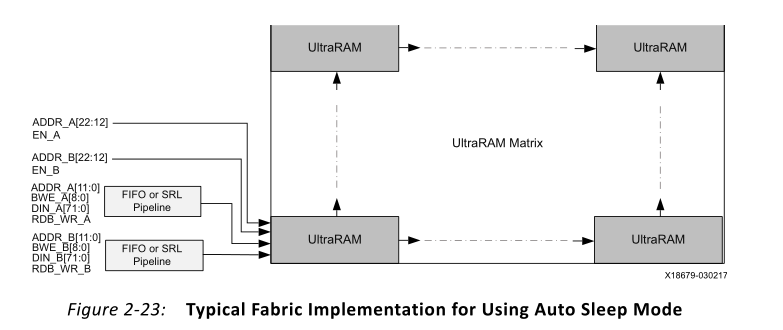

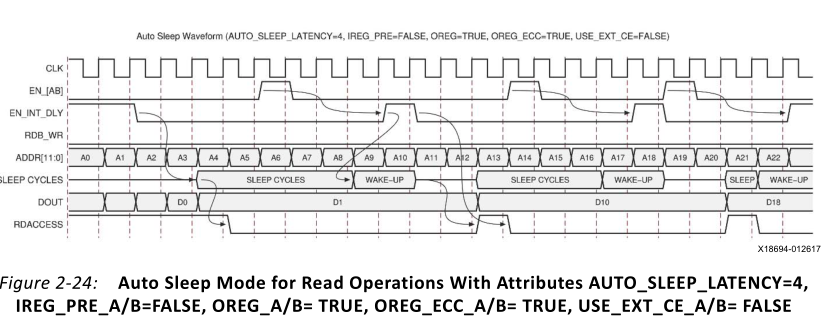

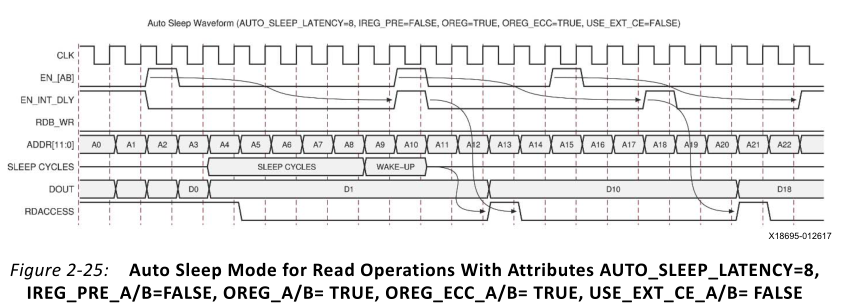

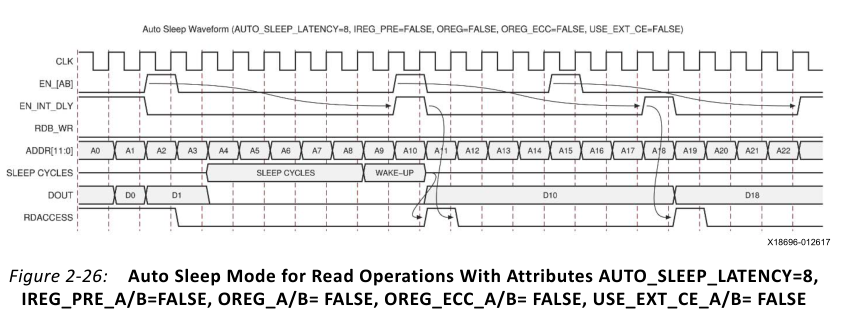

要确定UltraRAM何时可以在自动休眠模式下激活休眠和唤醒,需要前瞻性信息。字节写使能、读/写、数据和低位地址输入必须相对于使能和高位地址输入延迟。这些输入由与AUTO_SLEEP_THELLY设置相等的流水线阶段延迟,该设置可以介于3和15之间。FIFO或线性移位寄存器可以在FPGA结构中实现这一点。其他信号,如注入和CE输入,如果使用,也必须是流水线对齐的。有关更多信息,请参阅自动睡眠延迟-AUTO_SLEEP_LATHER。

EN_INT_DLY从输入EN延迟AUTO_SLEEP_DLATURE,以显示与其他输入的流水线对齐。当OREG_ECC=TRUE时,DOUT在休眠周期期间保存先前读取的数据。

EN_INT_DLY解除断言后,由于OREG阶段,在休眠周期之前插入额外的空闲周期。如果OREG管道设置为TRUE,则需要额外的周期以确保在UltraRAM进入休眠之前读取数据已传播到输出。

因此,EN_INT_DLY解除置位后需要等待两个周期,然后才能开始休眠周期。此外,睡眠周期也是AUTO_SLEEP_DLATION的函数,它规定了进入睡眠所需的空闲周期数(从EN到EN_INT_DLY的延迟)。

自动睡眠唤醒始终在EN_INT_DLY变为高电平之前一个周期发生,以保证在下一个读或写周期之前有足够的唤醒时间。唤醒仅是EN_INT_DLY_A/B(扩展为EN)上升的函数,没有其他输入。

EN_INT_DLY从输入EN延迟AUTO_SLEEP_DLATURE,以显示与其他输入的流水线对齐。当OREG_ECC=TRUE时,DOUT在休眠周期期间保存先前读取的数据。

AUTO_SLEEP_THELLAY指示UltraRAM进入睡眠所需的空闲周期数。在图2-25中,它被设置为8,这意味着在EN_INT_DLY解除断言和EN_INT_DLY的下一次断言之间至少需要8个周期才能看到任何休眠周期。在后面的周期中(在休眠/唤醒之后),没有足够的空闲时间,UltraRAM不会再次进入休眠状态。

有关预期睡眠周期数的信息,请参阅自动睡眠延迟-AUTO_SLEEP_THELLAY中的属性说明。

EN_INT_DLY从输入EN延迟AUTO_SLEEP_DLATURE,以显示与其他输入的流水线对齐。当没有休眠周期时,DOUT保存先前读取的数据,但当OREG_ECC=FALSE时,DOUT在休眠周期期间被驱动到“0”。

EN_INT_DLY从输入EN延迟AUTO_SLEEP_DLATURE,以显示与其他输入的流水线对齐。当没有休眠周期时,DOUT保存先前读取的数据,但当OREG_ECC=FALSE时,DOUT在休眠周期期间被驱动到“0”。