计算机组成原理 —— 总线和 I/O

2024年1月22日 晴天

不知道说啥,最近特别蠢,把自己吹感冒连续半个月,将近一个月。

第六章 总线

综合题 - 1

某总线的时钟频率为 66MHz,在一个 64 位总线中,总线数据传输的周期是 7 个时钟周期传输 6 个字的数据块。

(1)总线的数据传输率是多少?

(2)若不改变数据块的大小,而将时钟频率减半,这时总线的数据传输率是多少?

解析:

(1)velocity = quantity * frequency = 64/8 * 6/7 * 66 * 10^6 hz = 452.6 MB/s

(2)v = q * f = 64/8 * 6 / 7 * (66/2) MHz = 226.3 MB/s

综合题 - 2

某总线支持二级 Cache 块传输方式,若每块 6 个字,每个字长 4 字节,时钟频率 100 MHz。

(1)读操作时,第一个时钟周期接收地址,第二、三个为时延周期,另用 4 个周期传送一个块。读操作的总线传输率是多少?

(2)写操作时,第一个时钟周期接收地址,第二个为延时周期,另用 4 个周期传送一个块,写操作的总线传输速率是多少?

(3)设在全部的传输中,70%用于读,30%用于写,该总线在本次传输中的平均传输速率是多少?

解析:

(1)每个主存块 = 6*4 = 24 B

每个时钟周期读操作数据 24B / 7 = 24/7 B —— 前摇的动作也要算入!

bit rate = quanity * frequency = 24/7 B * 100 MHz = 342.9 MB/s

(2)每个时钟周期写操作数据 24B / 6 = 4B

bit rate = quantity * frequency = 4B * 100 MHz = 400 MB/s

(3)平均读写速度 = 0.7 * 342.9 MB/s + 0.3 * 400 MB/s = 240 MB/s + 120 MB/s = 360 MB/s

Page 258

综合题 - 1

在异步串行传输方式下,起始位为 1 位,数据位为 7 位,偶校验位为 1 位,停止位为 1 位,若波特率为 1200 b/s ,问这时的有效数据传输速率为多少?

解析:

1.ASCII 一共 10 比特

2.这里的波特率是 b/s,有效数据传输率 = 速率 * 有效比特的比例 = 1200 b/s * 7/10 = 840 b/s

Page 270

综合题 - 1

硬磁盘共有 4 个记录面,存储区域内半径为 10 cm,外半径为 15.5 cm,道密度为 60 道/cm,外层位密度为 600 bit/cm,转速为 6000 转/分。

(1)硬磁盘的磁道总数是多少?

(2)硬磁盘的容量是多少?

(3)将长度超过一个磁道容量的文件记录在同一个柱面上是否合理?

(4)采用定长数据块记录格式,直接寻址的最小单位是什么?寻址命令中磁盘地址如何表示?

(5)假定每个扇区的容量为 512B,每个磁道有 12 个扇区,寻道的平均等待时间为 10.5 ms,试计算磁盘平均存取时间。

解析:

(1)半径差 = 15.5 - 10 = 5.5CM, 磁道 = 60 道/CM * 5.5 CM = 330 道, 磁道总数 = 4 * 330 = 1320 道

(2)外层磁道长度 = 2*Pi*R = 2 * 3,14 * 15.5 = 97.34 CM

每条磁道比特数量 = 97.34 CM * 600bit/CM = 7300.5 字节

磁盘总比特数 = 7300.5 字节 * 1320道 = 9636000字节

(3)文件长度超过一个磁道,可以记录在同一个柱面,这样可以避免重新寻道。

(4)定长数据块,直接寻址的最小单位是【扇区】

磁盘地址结构: 硬盘号(2位) + 柱面号(9位) + 扇区号(4位)

最多可以有,4个磁盘,8个记录面,每个面最多 128 个磁道,每道最多 16 个扇区。

(5)读取扇区的时间 = 磁头内外径的时间 + 盘片自转时间 + 扫过扇区时间

= 平均寻道时间 + 盘片旋转一圈的时间/2 + 扫过扇区时间

A 平均寻道时间 10.5 ms

B 盘片转一圈时间 / 2 = 60s / 6000转 * 0,5 = 5ms

C 盘片转一圈时间 10 ms ,扫过 12 个扇区。因此,扫过一个扇区的时间 = 10ms / 12 = 0.83 ms

因此,读取扇区时间 = 10.5 ms + 5 ms + 0.83 ms = 16.33 ms

【注意】 注意这里扫过扇区的时间。一圈是 12 个扇区,因为这类题比较少。此前,同类题目,计算的是扫过扇区时间(也就是读取扇区的时间),和传输对应数据的时间。

Page 289

综合题 -1

在 DMA 方式下,主存和 I/O 设备之间有一条物理通路 相连吗?

答:不是。DMA 方式下,I/O设备与主存连接的通路,必须通过 CPU。

综合题 - 2

问题:

(1)一个完整的指令周期,包括哪些 CPU 工作周期?

(2)中断周期前和中断周期后各是 CPU 的什么工作周期?

(3)DMA 周期前和 DMA 周期后各是 CPU 什么工作周期?

解析:

(1)完整的指令周期:取址、间址、执行、中断

(2)中断之前是执行;中断之后是下一个指令的取址

(3)DMA 周期前后都是机器周期。

综合题 - 3

假定某 I/O 设备向 CPU 传送信息的最高频率为 4 万次/秒,而相应中断处理程序的执行时间为 40 微秒,则该 I/O设备是否可采用中断方式工作?为什么?

解析:

I/O和CPU之间传送一次为 1/40000 = 25 微秒

处理中断 40 微秒

这意味着,中断还没处理完,CPU 又会发送传输请求。这会使得数据丢失,因此不能采用中断方式。

综合题 - 4

在程序查询方式的输入/输出系统中,假设不考虑处理时间,每个查询操作需要 100 个时钟周期,CPU 时钟频率为 50 MHz。现有鼠标和硬盘两个设备,而且 CPU 必须每秒对鼠标进行 30 次查询,硬盘以 32 位字长为单位传输数据,即每 32 位被 CPU 查询一次,传输率为 2 * 2^20 B/s。求 CPU 对这两个设备查询所花费的时间比率,由此可得出什么结论?

解析:

1.用 CLK 计算

2.鼠标。每秒查询 30 次 * 100 CLK = 每秒占用 3000CLK

每秒 3000 / 50M = 60 * 10^(-6) = 0.006%

3.硬盘。4字节查一次。时间 = Quantity / Velocity = 4字节 / 2*2^20 字节/秒 =2^(-19) 秒

每秒查询 2^19 次

硬盘占用比例 = 2^19 / 50M= 512K/50M = 102.4%

CPU全部时间都不足以查询硬盘,因此不用这个方式与硬盘交互。

综合题 - 5

【2009】某计算机的 CPU 主频 500 MHz,CPI 为5(即执行每条指令平均需 5 个时钟周期)。假定某外设的数据传输率为 0.5 MB/s ,采用中断方式与主机进行数据传送,以 32 位为传输单位,对应的中断服务程序包含18 条指令,中断服务的其他开销相当于 2 条指令的执行时间,回答问题,并给出计算过程。

(1)在中断方式下,CPU 用于该外设的 I/O 时间占整个 CPU 时间的百分比是多少?

(2)当该外设的数据传输率达到 5 MB/s 时,改用 DMA 方式传送数据。假定每次 DMA 传送块大小为 5000B,且 DMA 预处理和后处理的总开销为 500 个时钟周期,则 CPU 用于该外设 I/O 的时间占整个 CPU 时间的百分比是多少(假设 DMA 与 CPU 之间没有访存冲突)?

解析:

(1)分为中断需要的 CLK,以及传数据需要的 CLK

中断需要的 CLK = (18+2) * 5 = 100 CLK

一次传数据需要的时间 = 4字节 / 0.5 MB/s = 8 / (10^6) s = 8 微秒

每秒传数据次数 = 1/ 8 微秒 = 125000 次

处理 I/O 的百分比 = (100 + 125000) / 500M = 0.25 * 10^(-3) = 0.025% —— 这是错的

处理 I/O 百分比 = (100 * 125000 ) / 500M = 2.5% —— 这是对的。每秒传送 125000 次,每次需要 100 CLK。

(2)

DMA 每秒传 1000 次,每次 500 CLK,每秒 500 000 CLK

I/O 百分比 = 500 000 / 500M =0.1%

【注意】 DMA 每次处理,只有预处理和后处理。

综合题 - 6

【2012】假定某计算机的 CPU 主频为 80 MHz,CPI 为 4,平均每条指令访存 1.5 次,主存与 Cache 之间交换的块大小为 16B,Cache 的命中率为 99%, 存储器总线带宽为 32 位,回答:

(1)该计算机的 MIPS 是多少? 平均每秒 Cache 缺失的次数是多少?在不考虑 DMA 传送的情况下,主存带宽至少达到多少才能满足 CPU 的访存要求?

(2)假定在 Cache 缺失的情况下访问主存时,存在 0.0005% 的缺页率,则 CPU 平均每秒产生多少次缺页异常?若页面大小为 4KB ,每次缺页都需要访问磁盘,访问磁盘时 DMA 传送采用周期挪用方式,磁盘 I/O 接口的数据缓冲寄存器为 32 位,则磁盘 I/O 接口平均每秒发出的 DMA 请求次数至少是多少?

(3)CPU 和 DMA 控制器同时要求使用存储器总线时,哪个优先级更高?为什么?

(4)为了提高性能,主存采用 4 体低位交叉存储模式,工作时每 1/4 个存储周期启动一个体,若每个体的存储周期为 50ns,则该主存能 提供的最大带宽是多少?

解析:

(1)每个 CLK 指令数 = 1/4 , 每秒 80M 个 CLK,于是 每秒指令数 = 1/4 * 80M = 20M Instructions 。故 MIPS 为 20。 —— 这是对的

Cache 缺失率 = 1%, 每条指令平均访存 1.5次。

平均每秒 Cache 缺失次数 = 每条指令访存次数 * 每秒指令数量 * (1-99%) = 1.5 * 20M * 1% = 300K

(2)每秒产生的缺页异常 = 300K* 0.0005% = 1.5 次

每秒平均访问页面大小 = 4KB * 1.5 = 6KB , 请求次数 = 6KB / 4B =1.5 * 1024 = 1536次

(3)DMA 请求优先级更高,因为是周期挪用的方式

(4)最大带宽(速度) = 4* 4B / 50ns = 320 MB/s

ns = 10^(-9) s

【注意】 这里一个体的大小,和端口寄存器一致。

综合题 - 7

【2016】假定 CPU 主频为 50MHz ,CPI 为 4,设备 D 采用异步串行通信方式向主机传送 7 位 ASCII 码字符,通信规程中有 1 位奇校验位和 1 位停止位,从 D 接收启动命令到字符送入 I/O 端口需要 0.5ms。回答:

(1)每传送一个字符,在异步串行通信线上共需传输多少位?在设备 D 持续工作过程中,每秒最多可向 I/O 端口送入多少个字符?

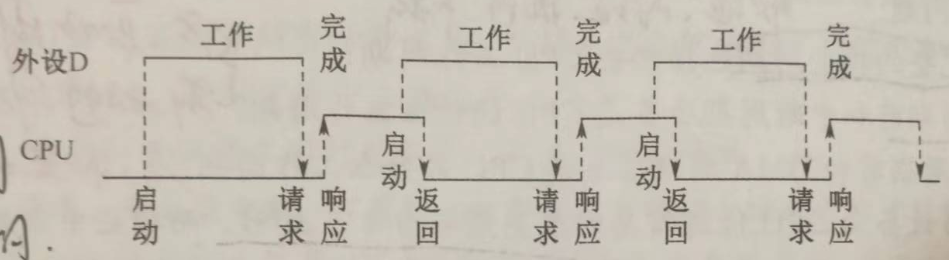

(2)设备 D 采用中断方式进行输入/输出。示意图如下:

I/O 端口每收到一个字符申请一次中断,中断响应需 10 个时钟周期,中断服务程序共有 20 条指令,其中第 15 条指令启动 D 工作。若 CPU 需从 D 读取 1000个字符,则完成这一任务所需时间大约是多少个时钟周期?CPU 用于完成这一任务的时间大约是多少个时钟周期? 在中断响应阶段 CPU 进行了哪些操作?

解析:

(1)传送一个 ASCII 码,需要 10 位。 —— 这个一定要记住!

每秒向 I/O 端口送的次数 = 1 / 0.5 ms = 2000次

每次输送 10 比特,于是每秒向 I/O 端口送 2000 * 10 bit = 2000个字符。

(2)中断响应 10 CLK

中断服务 20 Inc. * 4 = 80 CLK

中断一次耗去 90CLK

读取 1000 字符 = 1000 * 90 CLK = 90000 CLK

针对第二小题"完成这一任务的时间"

第一,处理中断服务程序,前 15 条指令可以用 CPI来计算。后面 5 条指令,传输 D 的内容。

第二,因为题目给出【D设备启动,到将数据送到端口寄存器】,这是后面 5 条指令的效果。既然给出时间,直接用题目给出的【时间】变量。

D设备启动 -> 数据送到端口寄存器,需要 0.5 ms,CPU 标准时间 1/50M s/CLK。因此,D设备启动直至数据送到端口寄存器,这段时间需要 0.5 ms / (1/50M) = 25000 CLK

第三,中断完成数据传送至端口寄存器,总时钟周期 = 中断响应 10 CLK + 前 15 条指令 15 * 4 CLK + 后 5 条指令 25000 CLK = 25070 CLK

1000 个字符需要的 CLK = 1000 * 25070 = 2.507 * 10^7 CLK

中断响应:关中断、保护断点、程序状态、识别中断源。

综合题 - 8

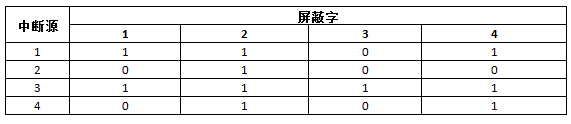

设某计算机有 4 个中断源 1、2、3、4,其硬件排队优先次序按 1 - 2 - 3 - 4 降序排列,各中断源的服务程序中所对应的屏蔽字如下所示

(1)给出上述 4 个中断源的中断处理次序。

(2)若 4 个中断源同时有中断请求,画出 CPU 执行程序的轨迹。

解析:

(1)看列。因此,中断次序,3-1-4-2

(2)如果原来的中断源顺序是 1-2-3-4

执行顺序, 1-2(中断1)-3(执行完 2,再执行1,再执行3) - 4(可中断1,不可中断2,可中断3,如全部执行完,则直接执行4)

综合题 - 9

假设磁盘采用 DMA 方式与主机交换信息,其传输速率为 2 MB/s ,而且 DMA 的预处理需要 1000 个时钟周期,DMA 完成传输后处理中断需要 500 个时钟周期。若平均传输的数据长度为 4KB,试问在硬盘工作时,50 MHz 的处理器需用多大的时间比率进行 DMA 辅助操作(预处理和后处理)?

解析:

1.CPU 每秒钟 50M CLK

2.DMA 预处理+后处理一共多少个 CLK?一共 1000 + 500 = 1500 CLK

DMA 每秒处理的次数 = 2 MB/s / 4KB = 0.5 * 1024 次/秒 = 512 次/秒

DMA 每秒占用 CLK 个数 = 1500 CLK/次 * 512 次/秒 = 768000 CLK/秒

综上,DMA占用CPU比例 = 768000 CLK / 50M = 1.536%

综合题 - 10

一个 DMA 接口可采用周期窃取方式把字符传送到存储器,它支持的最大批量为 400B。若存取周期为 0.2微秒,每处理一次中断需 5 微秒,现有的字符设备的传输率为 9600 b/s。假设字符之间的传输时无间隙的,试问 DMA 方式每秒因数据传输占用处理器多少时间?若完全采用中断方式,又需占处理器多少时间(忽略预处理所需时间)?

解析:

(1)数据传输

字符设备速度 = 1200 B/s —— 自己没做对!因为概念不清晰!

每秒传 1200B,因此需要 1200 个存取周期。 —— 这里是这样理解的。存取周期,针对读写主存或寄存器,读写一次的数据量,是一个字,或一个字节。【周期窃取】=【周期挪用】

每次能传 400 B,因此,每秒需要传 1200B / 400B = 3次

需要的时间 = 3*5微秒 + 0.2微秒*1200 = 255 微秒

(2)中断

中断的话,1200 次中断

时间 = 5微秒 * 1200 = 6000 微秒 = 6 毫秒

注意:对于【存取周期】理解不深刻。存取周期,一次传的数据,即一个字,或者一个字节。

综合题 - 11

假设磁盘传输数据以 32 位的字为单位,传输速率 1MB/s,CPU 的时钟频率为 50 MHz。回答:

(1)采取程序查询方式,假设查询操作需要 100 个时钟周期,求 CPU 为 I/O 查询所花费时间比率(假设进行足够的查询以避免数据丢失)?

(2)采用中断方式进行控制,每次传输的开销(包括中断处理)为 80 个时钟周期。求 CPU 为传输硬盘所花费的时间比率。

(3)采用 DMA 方式,假定 DMA 的启动需要 1000 个时钟周期,DMA 完成时后处理需要 500 个时钟周期,若平均传输的数据长度为 4KB,试问硬盘工作时处理器将用多少时间比率进行输入/输出操作?忽略 DMA 申请总线的影响。

解析:

(1)每秒查询次数 = 传输速度 / 数据量 = 1MB/s / 4B = 256 * 1024 次/秒 = 262144 次/秒

每秒需要的时钟周期 = 262144次 * 100 CLK = 26214400 CLK

占用 CPU 比率 = 26214400 / 50M = 52.4%

(2)每秒传输的次数 = 传输速率 / 一次传输数据量 = 1MB/s / 4B = 262144 次/秒

每秒需要的 CLK = 262144 次 * 80 = 21M

占用CPU 比率 = 21M / 50M = 41.9%

(3)DMA方式,跑一次需要 1500 CLK

每秒CPU传的次数 = 1 MB/s / 4KB = 256 次/秒

1500 * 256 = 384K

CPU比例 = 384K / 50M = 0.768%

综合题 - 12

【2018】假定计算机的主频为 500MHz,CPI 为 4,现有设备 A 和 B,其数据传输率分别为 2 MB/s 和 40 MB/s,对应 I/O接口中各有一个 32 位数据缓冲寄存器。回答问题:

(1)若设备 A 采用定时查询 I/O 方式,每次输入/输出都至少执行 10 条指令。设备 A 最多间隔多长时间查询一次才能不丢失数据?CPU 用于设备 A 输入/输出的时间占 CPU 总时间的百分比至少是多少?

(2)在中断 I/O 方式下,若每次中断响应和中断处理的总时钟周期至少为 400,则设备 B 能否采用中断 I/O 的方式?为什么?

(3)若设备 B 采用 DMA 方式,每次 DMA 传送的数据块大小为 1000B,CPU 用于 DMA 预处理和后处理的总时钟周期数为 500,则 CPU 用于设备 B 输入/输出的时间占 CPU 总时间的百分比最多是多少?

解析:

(1)每次 I/O 的CLK 数量 = 10条指令 * CPI = 40 CLK

每秒 I/O 次数 = 速度 / 每次传的数据量 = 2 MB/s / 4B = 512 K次

每秒 CLK = 40 * 512K = 20M

CPU比率 = 20M / 50M = 40%

(2)B设备每秒 I/O 次数 = 40 MB/s / 4B = 10M

每秒中断响应和中断处理的 CLK = 10M * 400 = 4000M > 500M

说明 CPU 处理不了,因此不能用中断方式。

(3) 每秒 I/O 次数 = 速度 / 每次传输的数据量 = 40 MB/s / 1000B = 40K次

每秒需要的 CLK = 40K * 500 = 20 M

CPU比率 = 20M / 500M = 4%

总结:2024年1月24日,距离考试考完已经一个月了。本人表示,学习要是做了几道题还没感觉,结论只有一个,就是共性的部分,还未获取到!

ShoelessCai.com 您值得关注!

浙公网安备 33010602011771号

浙公网安备 33010602011771号