计算机组成原理 —— 指令系统

离考试还有7天,还有 2.5 门专业课。

这次复习还是没抓住主要的内容,还剩数据结构,操作系统,和一半计组,内容不难,知识点零碎。

今天早上 4点半起来,效率很低,但还是 尝试新方法,我先把王道辅导书所有真题有关的习题和答案上传,尽量全部讲解一遍。

兼职认识或者接触到的伙伴赶紧跟上吧,但愿您们跟上步伐的时候,不会因为脸面,而干一些让全球华人都哭笑不得的事情 —— 脸比五星红旗还大,是什么意思?

开始讲课啦!

14 这道题,只要 takeaway ,三地址多出的部分,可以分割二地址。

2024年 1 月 17 日

15.特权指令,是不开放给用户使用的。

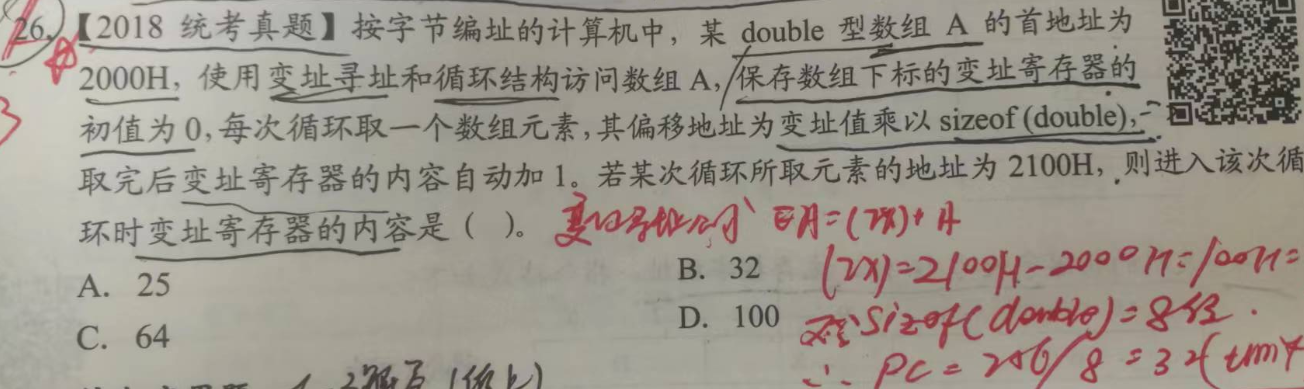

16.【2018】按字节编址的计算机中,某 double 型数组 A 首地址为 2000H,使用变址寻址和循环结构访问数组A,保存数组下标的变址寄存器的初值为 0 ,每次循环取一个数组元素,其偏移地址为变址值乘以 sizeof(double)

,取完后变址寄存器的内容自动加 1。若某次循环所取元素的地址为 2100H,则进入该次循环时变址寄存器的内容是()

A 25 B 32 C 64 D 100

答案:B

解析:

1.这道题,要把题目读懂;

2.放置下标的变址寄存器,偏移地址 = 变址数值 * sizeof(double) 每个数组元素是 double

3.因此,按照题目的含义,如果某次循环的地址为 2100H。实质想问的是,每个元素 double 的话,要经过几个 unit ?

4.这样的话,就来解题吧!

计算偏移量 = 2100H - 2000H = 100H = 1* 16^2 = 256 bit

元素个数 = 256 / 8 = 32 个 这个含义,本次循环,已经经过 32 个数组元素。

那么,寄存器放置的相对位移,是几呢?答曰 32,因为下标为 0 的时候,寄存器的值为 0。这一步的理解,就当作某种映射吧。

综合题-1

寄存器寻址的时候,速度最快,指令最短。

综合题-2

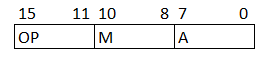

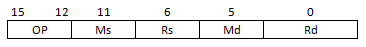

机器字长 16 位,存储器按字编址,访问内存指令格式:

其中,OP 为操作码,M 为寻址特征,A 为形式地址。设 PC 和 Rx 分别为程序计数器和变址寄存器,字长为 16 位,问:

(1)该指令能定义多少种指令?

答曰:指令的种类数量,有操作码的位数决定。故有 2^5 = 32 种 指令;

(2)确定各类寻址的【寻址范围】,完成填表。Jingyi 评注,为了更加好地学习,写上理由;

(3)写出 EA 计算公式。

变址寻址的范围为什么是 64K 还没理解。

2024.1.17 下午 5:51

黄色部分的含义,是寄存器8位,和偏移 8 位,总共范围 2^16 = 64KB

综合题-3

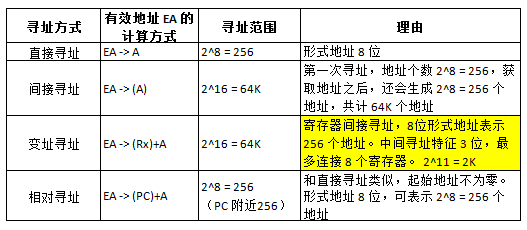

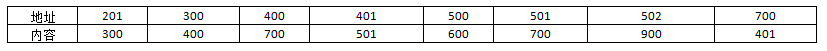

一条双字长的 LOAD 指令存储在地址为 200 和 201 的存储位置,该指令将指定的内容装入累加器(ACC)中。指令的第一个字指定操作码和寻址方式,第二个字是地址部分,主存内容示意图如下如所示。PC值为 200,R1 值为 400,XR 值为 100。

指令的寻址方式字段可指定任何一种寻址方式。回答问题:

直接寻址:EA的地址码 500,装入 ACC 的是 800; —— 注意,和立即数差异。

立即寻址:500 装入 ACC

间接寻址:300装入 ACC。500间址一次,800间址第二次。

相对寻址:325 装入 ACC 。EA = (PC)+A,202+500 = 702,间址之后 325。+2 因为双字指令长,unit = 指令长 / 机器字长 = 2

变址寻址:900 装入 ACC。EA = (XR)+A = 100 + 500 = 600 ;(600) = 900

寄存器 R1 寻址:400 装入 ACC。(R1)=400

寄存器 R1 间接寻址:700 装入 ACC。(R1)=400,(400)=700

评注:这道题目,可以背一背。

综合题-4

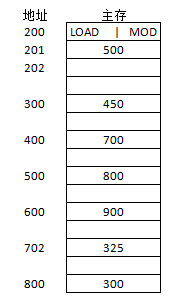

某机器字长 16 位,主存按字编址,指令格式如下:

其中,D 为位移量,X 为寻址特征位。

X = 00: 直接寻址

X = 01: 用变址寄存器 X1 进行变址

X = 10: 用变址寄存器 X2 进行变址

X = 11: 相对寻址

设 (PC)=1234H,(X1)=0037H,(X2)=1122H(H代表十六进制),确定下列指令的有效地址:

(A) 4420H

(B) 2244H

(C) 1322H

(D) 3521H

(E) 6723H

解析:

机器字长 16 位,按字编址。写出指令 EA。

(A) 0100 01 00 0010 0000

直接寻址,EA = 20H

(B) 0010 00 10 0100 0100

X2变址,1122H + 44H = 1166H = EA

(C) 0001 00 11 0010 0010

相对寻址,1235H + 22H = 1257H

(D) 0011 01 01 0010 0001

X1变址, 0037H + 21H = 0058H

(E) 0110 01 11 0010 0011

相对寻址, 1235H + 23H = 1258H

评注:直接寻址 v.s. 相对寻址。直接寻址 A,相对寻址(PC)+ A。

综合题-5

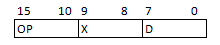

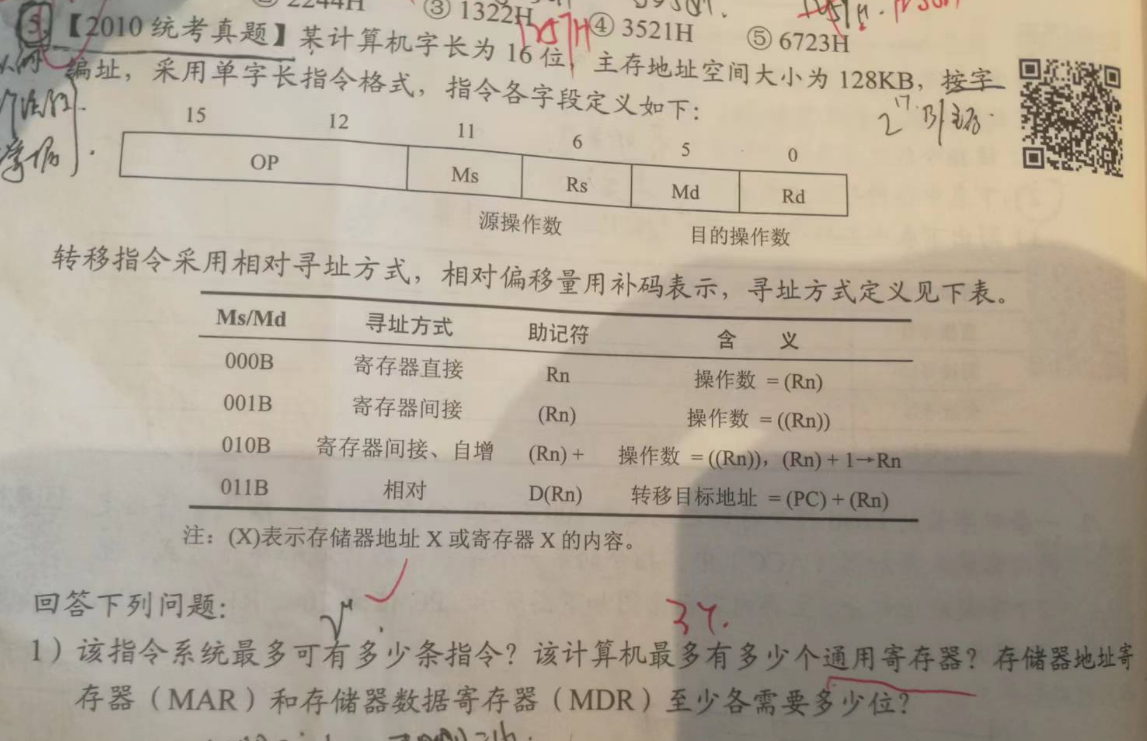

【2010】某计算机字长为 16位,主存地址空间大小为 128 KB,按字编址,采用单字长指令格式,指令各字段定义:

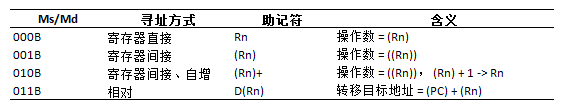

转移指令采用相对寻址方式,相对偏移量用补码表示,寻址方式定义。

回答:

(1)该指令系统最多可有多少条指令?该计算机最多有多少个通用寄存器?存储器地址寄存器(MAR)和存储器数据寄存器(MDR)至少各需要多少位?

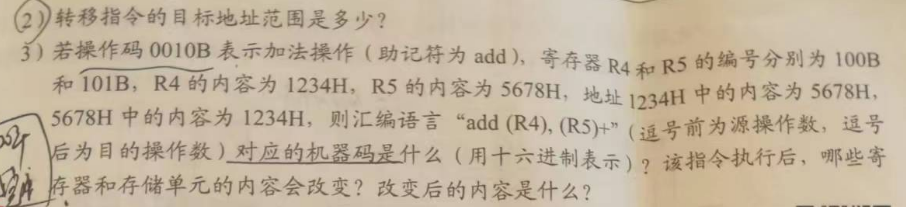

(2)转移指令的目标地址范围是多少?

(3)若操作码 0010B 表示加法操作(助记符为 add ),寄存器 R4 和 R5 的编号分别为 100B 和 101B ,R4 的内容为 1234H, R5 的内容为 5678H,地址为 1234H 中的内容为 5678H ,5678H 中的内容为 1234H,则汇编语言 “add (R4),(R5)+” (逗号前为源操作数,逗号后为目的操作数)对应的机器码是什么(十六进制)?该指令执行后,哪些寄存器和存储单元的内容会改变?改变后的内容是什么?

解析:

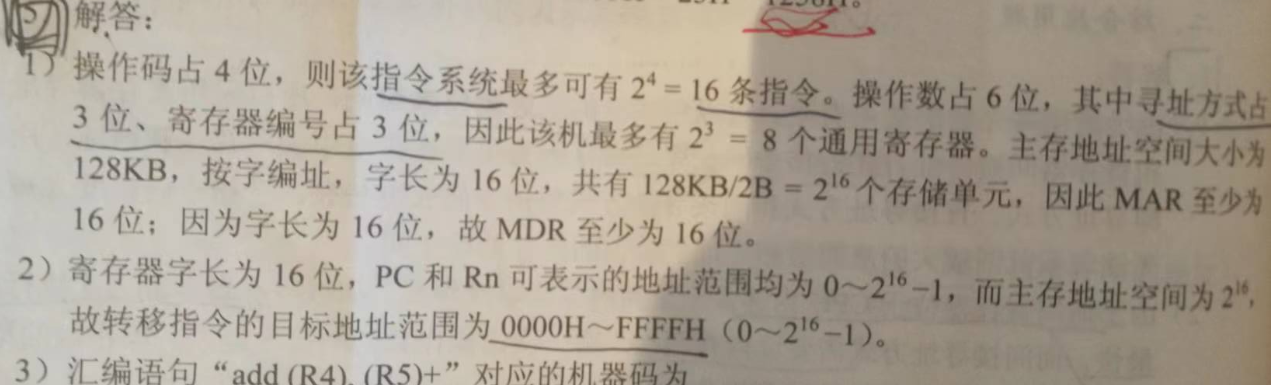

(1)

指令条数,取决于操作码位数,可以表示 2^4 = 16 条指令。

这里注意,要看懂示意图。11表示 Ms 左端,6 表示 Rs 右端。于是推导出,源寄存器,目的寄存器,都为 3 位。故 2^3 = 8 个通用寄存器。这里要注意,Rs, Rd 都是连接到同一组寄存器。

主存大小 128KB,单元大小 2B(按字编址,16位一个字),于是存储单元个数 = 128KB / 2B = 2^16 B = 64KB

MAR 16 根,MDR 16根(按字编址,16位一个字)

(2)求 转移目标地址,不会。

PC 和 寄存器寻址 Rn 范围,取决于寄存器位数,寄存器 16 为,因此范围 0 - 2^16 - 1 —— 这部分答案,应该指的是 MAR 和 MDR

0000H ~ FFFFH

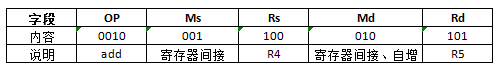

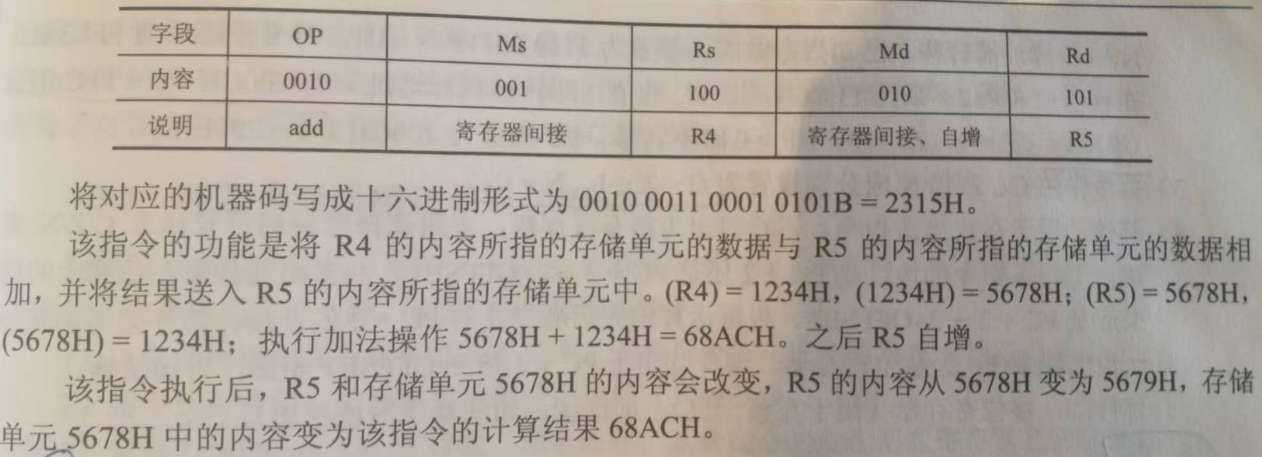

(3)

汇编语句 “add(R4), (R5)+” 对应机器码

内容连在一块:

0010 001 100 010 101 = 0010 0011 0001 0101 = 2315H

这道题目,考察一个基本知识点,就是机器码是怎么来的。依据一套指令系统,动作对应的 0-1 编码,寄存器对应编号,源主存、源寄存器、目的主存、目的寄存器,组织方式,组装起来成为机器码。

((R4)) + ((R5)) = (1234H) + (5678H) = 5678H + 1234H = 68ACH 该结果存储在 R5

R5,主存 5678H 地址的内容会变。

(R5) = 5679H

(5678H) = 68ACH

注意:真题,必须掌握。

综合题-6

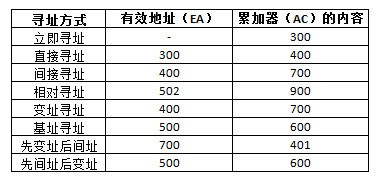

一条双字长的取数指令(LDA)存于存储器的 200 和 201 单元,其中第一个 200,变址寄存器 IX 的内容为 100,基址寄存器的内容为 200,存储器相关单元的内容如下表所示:

下表的各列分别为寻址方式,该寻址方式下的有效地址及取数指令执行结束后累加器(AC) 的内容,试补全下表:

解析:

相对寻址,要计算 (PC)自增的值。(PC) = 200 自增至 202,offset = 300,EA = 502

先变址后间址,变址 100 + 300 = 400,(400)=700,EA = 700

先间址后变址,直接寻址 (200) = 300,间址 (300)=400,变址 100 + 400 = 500,EA = 500

综合题-7

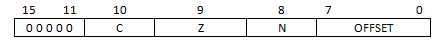

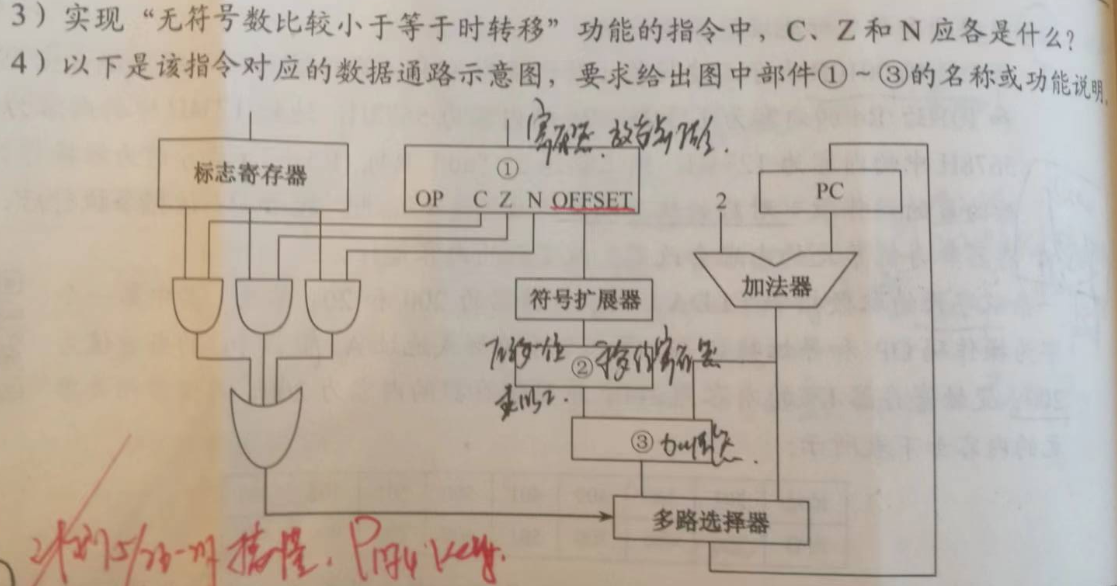

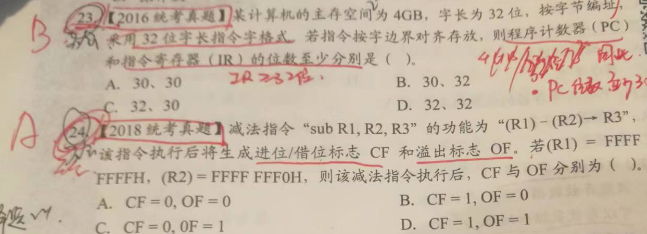

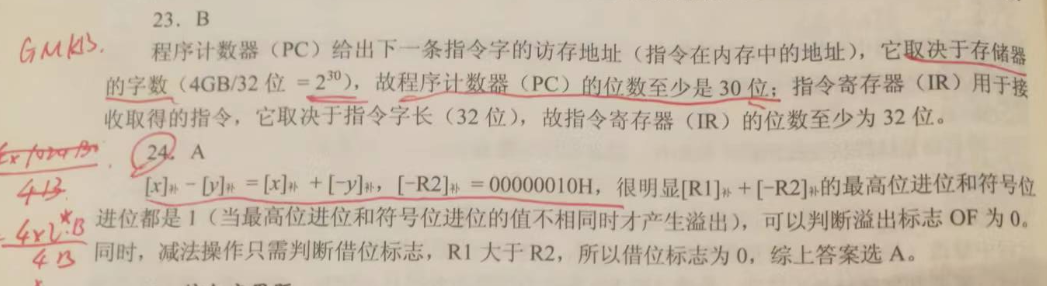

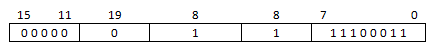

【2013】某计算机采用 16位定长指令字格式,其 CPU 中有一个标志寄存器,其中包含进位/错位标志 CF、零标志 ZF 和符号标志 NF。假定为该机设计了条件转移指令,格式如下:

其中,00000 为操作码OP,C,Z,N 分别为 CF,ZF,NF的对应检测位,某检测位为 1 时表示需检测对应标志,需检测的标志位中只要有一个为 1 就转移,否则不转移,否则不转移。例如,若 C=1,Z=0,N=1,则需检测 CF 和 NF 的值,当 CF=1,或 NF =1 时发生转移;OFFSET 是相对偏移量,用补码表示。转移执行时,转移目标地址为 (PC)+2 + 2*OFFSET ;顺序执行时,下一条指令地址为 (PC) + 2。回答:

(1)该计算机存储器是按字节编址还是按字编址?该条件转移指令向后(反向)最多可跳转多少条指令?

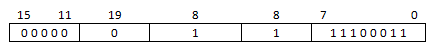

(2)某条件转移指令的地址为 200CH ,指令内容如下图所示,若该指令执行时 CF=0,ZF=0,NF=1,则该指令执行后 PC 的值是多少?若该指令执行时 CF=1,ZF=0,NF=0,则该指令执行后 PC 值为多少?写出计算过程。

(3)实现“无符号数比较小于等于时转移” 功能的指令中,C,Z和 N应各是什么?

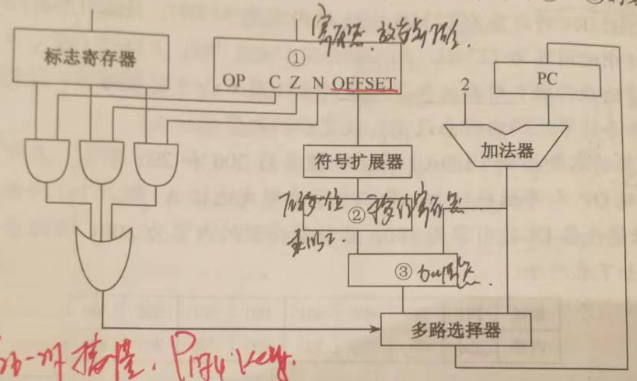

(4)以下是该指令对应的数据通路示意图。给出图中 1 - 3号部件名称、功能。

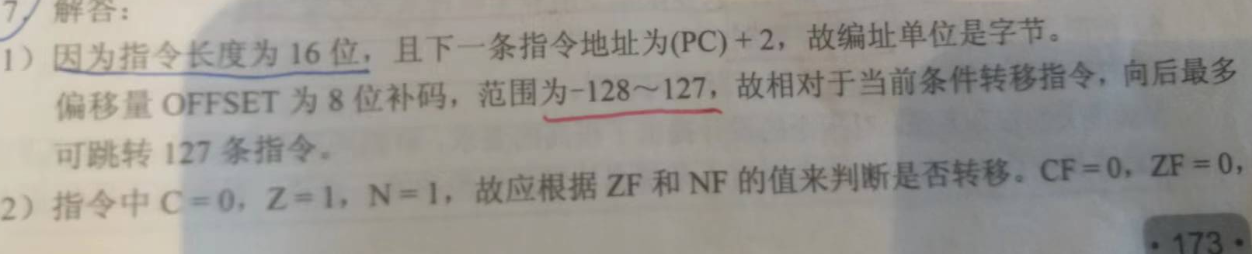

解析:

(PC)+2 + 2*OFFSET —— 这个公式最好记住

(1)

由于(PC)+2 按字节编址。

OFFSET 因为是补码,范围 -128 - 127,向后跳转最多 127 条指令。

(2)

转移指令地址 200CH

指令操作码 0000 0 011 1110 0011 B

注意到,CZN为并集的关系,只要为 1 的位置,一个为1,就转移。

CZN 为 001,转移,转移地址 (PC)+2+2*offset = 200CH + 2H+ 2* 1110 0011B = 200CH + 2H + 1100 0110B = 200CH + 2H + FFC6H = 1FD4H

CZN 为 100,不转移,地址 (PC) + 2 = 200CH + 2H = 200EH

Remark: 这类转移指令的算法,记住!因为经常考!

(3)

“无符号数比较时小于等于时候转移”

第一,无符号,符号位 0;

第二,进位1,零位1(因为没有符号);

综上,C=1,Z=1,N=0

(4)

部件1 - 指令寄存器;

部件2 - 移位寄存器;

部件3 - 累加器/加法器

2 和 3 主要完成,(PC)+2+2*offset

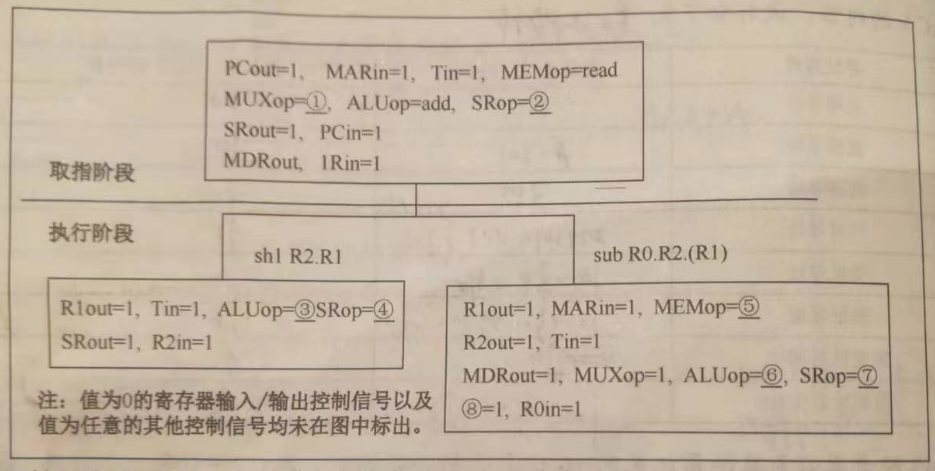

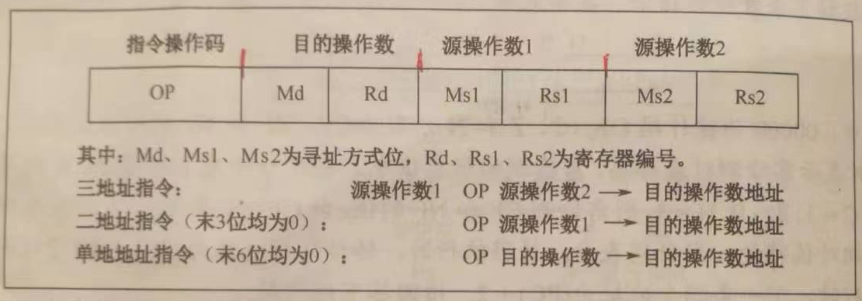

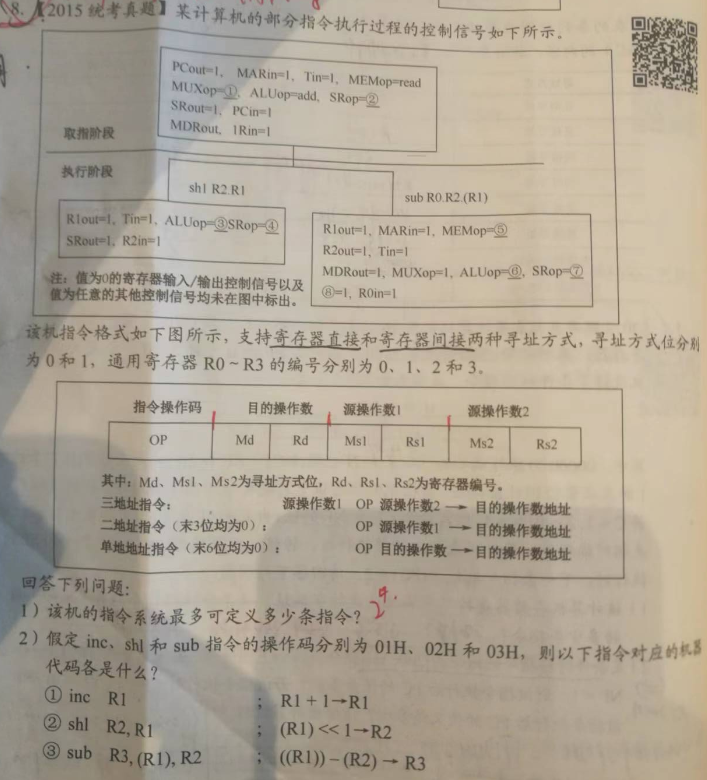

综合题-8

【2015】该机器指令格式如【图-2】所示,支持寄存器直接和寄存器间接两种寻址方式,寻址方式位分别为 0 和 1 ,通用寄存器 R0 - R3 编号分别为 0,1,2,3

图-1

图-2

回答问题:

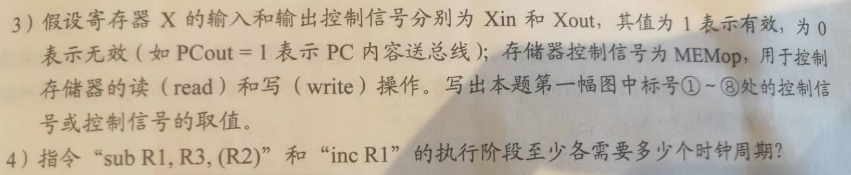

(1)该机的指令系统最多可定义为多少条指令?

(2)假定 inc, shl, sub 指令的操作码分别为 01H, 02H, 03H ,则以下指令对应的机器代码是什么?

(A) inc R1 ; R1+1 -> R1

(B) shl R2, R1 ; (R1) << 1 -> R2

(C) sub R3, (R1), R2 ; ((R1)) - (R2) -> R3

(3)假设寄存器 X 输入和输出控制信号分别 Xin 和 Xout ,其值为 1 表示有效,为 0 表示无效(如 PCout =1 表示 PC 内容送总线);存储器控制信号为 MEMop,用于控制存储器的读(read)和写(write)操作。写出第一幅图中 1 - 8 控制信号或者控制信号取值。

(4)指令 “sub R1, R3, (R2)” 和 "inc R1" 的执行阶段至少各需要多少个时钟周期?

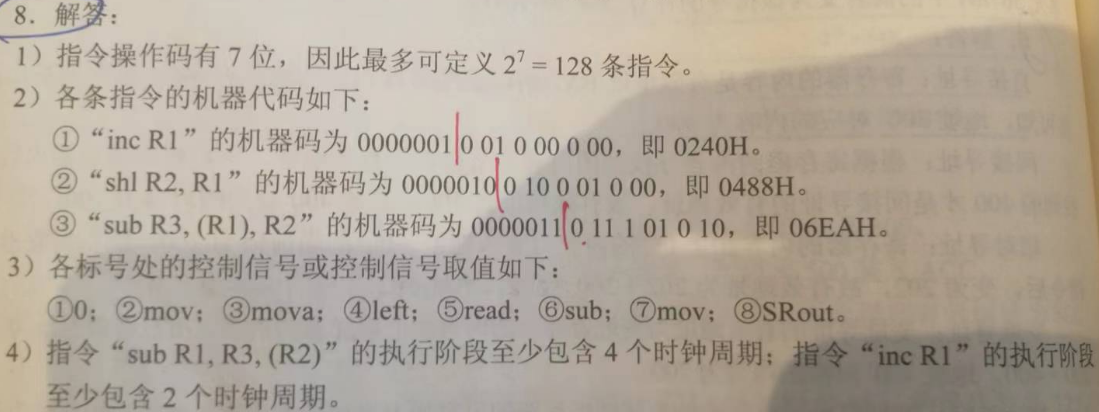

解析:

(1)指令条数 = 2^7 = 128 条指令。 7位这个信息,哪里找到的?

看到第二小题,我终于理解了!

每个操作数,1位寻址方式(0表示寄存器直接寻址,1表示寄存器间接寻址),2位表示寄存器号码(共4个寄存器) —— 这类推导方式注意一下!

一共 3 个操作数,于是占据 3 * 3 = 9位

操作数位数 = 16 - 9 = 7位!

(2)已知 inc, shl, sub 操作码 01H 02H 03H。指令格局也已知了。

inc R1 0000 001 001 000 000 = 0000 0010 0100 0000 = 0240H

shl R2, R1 0000 010 010 001 000 = 0000 0100 1000 1000 = 0488H

sub R3, (R1), R2 0000 011 011 101 010 = 0000 0110 1110 1010 = 06EAH

(3)

这一小题,依据上述指令,标注图。

1.MUXop=0 原因,单总线结构,需要另一个输入口。取址阶段不需要两个操作数,MUXop=0,MUX是多输入,单输出。

2.SRop = mov 寄存器操作,靠移动比特形成地址数据;

3.ALUop = mova 左移操作

4.SRop = left shl R2, R1。这里我没太理解,应该是寄存器的数据左移。

5.MEMop = read 这一步是 R1 内容作为地址,在主存定位,所以是 read

6.ALUop = sub 这一步是减法操作,操作数1 在 R1 获取地址,在主存获取地址;操作数2 又R2 内容给出,通过 MUX 输出到 ALU 另一端。输入操作就是 SUB

7.SRop = mov 运算完毕,操作寄存器进行存结果

8. SRout = 1 结果从寄存器输出吗?是的!

(4)

指令 sub R1, R3, (R2) 至少 4 CLOCK CYCLE

指令 inc R1 至少 2 CLOCK CYCLE

将能够同时进行的指令放在同一行,数行数。

CISC v.s. RISC

CISC 是Complex ,RISC 是 Reduced

前者一般 200指令以上,多用微程序,占据 CPU 50%;

后者指令 100条左右,多用硬布线(硬件自动完成),占据 CPU 10%。一定采用流水线技术,非常多的通用寄存器。

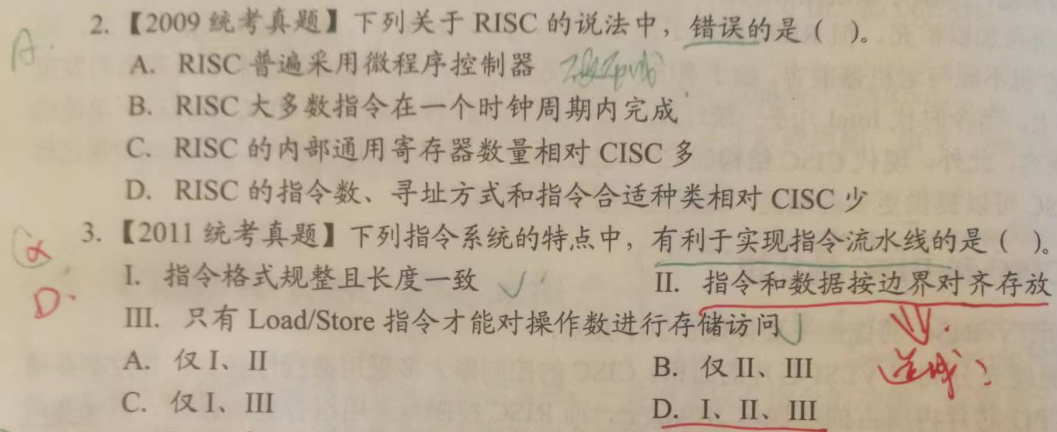

【2009】下列关于 RISC 说法中,错误的是()

A RISC 普遍采用微程序控制器

B RISC 大多数指令在一个时钟周期内完成

C RISC 内部通用寄存器数量相对 CISC 多

D RISC 指令数、寻址方式和指令合适种类相对 CISC 少

答案:A

【2011】下列指令系统特点中,有利于实现流水线的是()

(I)指令格式规整且长度一致

(II)指令和数据按边界对齐存放

(III)只有 Load/Store 指令才能对操作数进行存储访问

A 仅 I,II

B 仅 II, III

C 仅 I,III

D I,II,III

答案:D

2024年1月10日

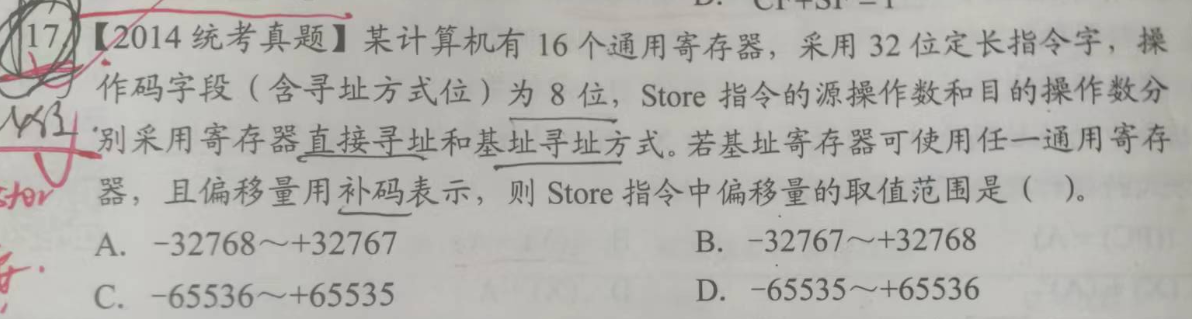

【2014】某计算机有 16 个通用寄存器,采用 32 位定长指令字,操作码字段(含寻址方式位)为 8 位,Store 指令的源操作数和目的操作数分别采用寄存器直接寻址和基址寻址方式。若基址寄存器可使用任一通用寄存器,且偏移量用补码表示,则 Store 指令中偏移量的取值范围是()

A -32768 ~ +32767

B -32767 ~ +32768

C -65536 ~ +65535

D -65535 ~ +65536

答案:A

解析:

1 指令含有两个操作数,操作数 1 使用的是直接寻址,16 个通用寄存器,于是留出 4 比特;

操作数 2 使用的是基址寻址,这也是一种相对位移,但是对程序员透明。公开资料显示,基址寻址用的是段寄存器。

段寄存器,一种寄存器存放 16 位,拿出来用的时候,后四位全 0 ,用于记录一些特殊的 20 位地址。

笔者个人的理解(证据尚不充分),基址寻址留出的 4位,应该是段寄存器的后四位。换言之,段寄存器记住某个地址前 16 位,后四位存于指令,指令的绝对起点就可以确定。

2.于是,该指令结构 OP 8位 + 操作数1 4位 + 操作数2 4位,于是还剩 32 - 8 -4 -4 = 16 位,表示偏移

偏移范围:-32768-32767

【16位指令长,按字节编址,立即推导出,(PC) + 2->PC 】

Page 164

18.某机器指令长为 16 位,主存按字节编址,取指令时,每取一个字节 PC 自动加 1,当前指令地址为 2000H ,指令内容为相对寻址的无条件转移指令,指令中的形式地址为 40H,则取指令后及指令执行后 PC 的内容为()

A2000H,2042H

B 2002J,2040H

C 2002H,2042H

D 2000H,2040H

答案:C

解析:

1.取指令之后,(PC)+2 -> PC , 2002H

2.执行之后,加上偏移量,2042H

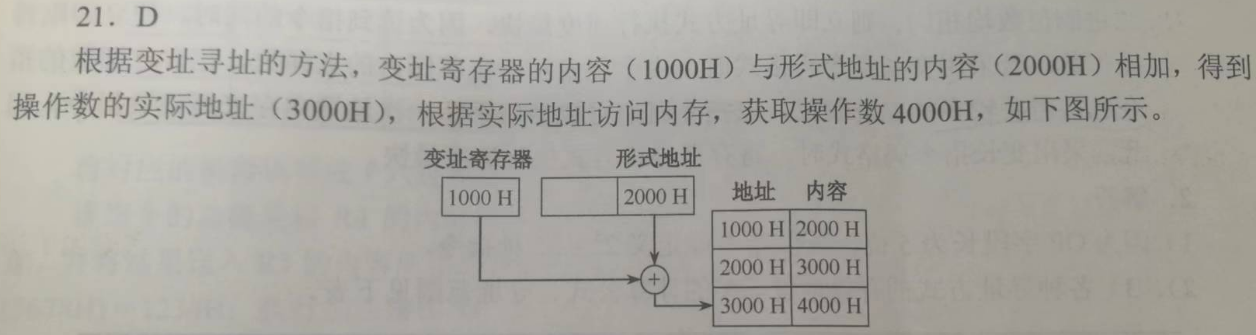

【2013】假设变址寄存器 R 的内容为 1000H,指令中的形式地址为 2000H,地址 1000H 中的内容为 2000H ,地址为 2000H 的单元中的内容为 3000H,地址为 3000H 的单元中的内容为 4000H ,变址寻址下,访问到的操作数是()

A 1000H

B 2000H

C 3000H

D 4000H

答案:D

解析:

1. 王道这里编排了三道连续的寄存器间址寻址

2.((寄存器) + 形式地址) 取出地址对应的内容

3.结合后面两道题一起阅读。

Page 164

22. 假设某条指令的第一个操作数采用寄存器间接寻址方式,指令中给出的寄存器编号为 8,8号寄存器的内容为 1200H,地址为 1200H 的单元中的内容为 12FCH,地址为 12FCH 的单元中的内容为 38D8H ,而地址为 38D8H 的单元中的内容为 88F9H ,则该操作数的有效地址为()

A 1200H

B 12FCH

C 38D8H

D 88F9H

答案:A

解析:

1.寄存器间接寻址,寄存器内的内容为地址,还要间址一次;

2.(1200H) =12FCH 其中,有效地址 1200H,操作数 12FCH

所以选择 A

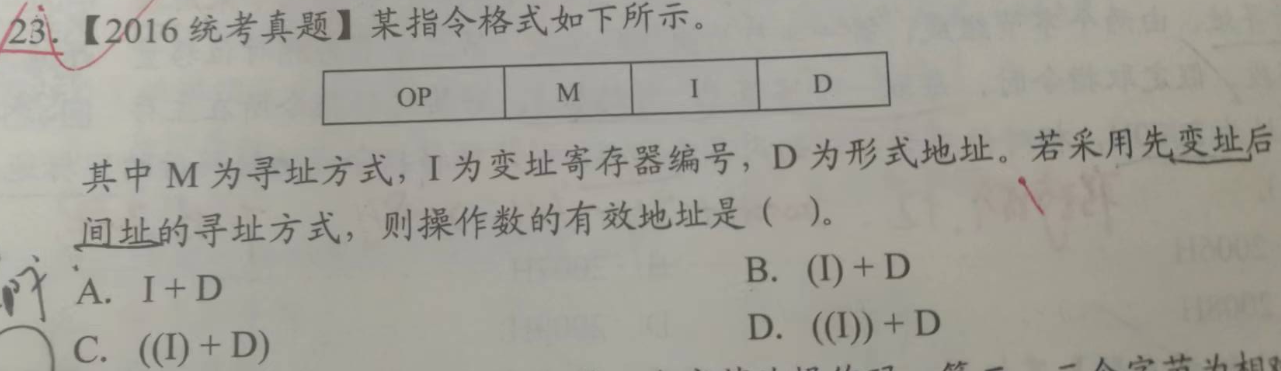

【2016】 某指令格式如下所示:

OP + M + I + D

其中 M 为寻址方式,I 为变址寄存器编号,D 为形式地址。若采用先编址后间址的寻址方式,则操作数的有效地址是()

A I+D

B (I) +D

C ((I)+D)

D ((I))+D

答案:C

解析:

1.变址存执,寄存器的内容为原点地址,直接当作地址用;

2.指令的形式地址,是偏移量的地址,需要加上原点间址;

3.((I)+D )

【小端存储、十进制相对寻址位移】

Page 164

24.设相对寻址的转移指令占 3B ,第一个字节为操作码,第一个字节为操作码,第二、三 个字节为相对位移量(补码表示),而且数据在存储器中采用以低字节为字地址的存放方式。每当 CPU 从存储器取出一个字节时,即自动完成 (PC)+1 -> PC 。若 PC 的当前值为 240 (十进制),要求转移到 290 (十进制),则转移指令的第二、三字节的机器代码是()。若 PC 的当前值 为 240(十进制),要求转移到 200(十进制),则转移指令的第二、三字节的机器代码是()

A 2FH,FFH

B D5H,00H

C D5H,FFH

D 2FH,00H

答案:D,C

解析:

1. 因为都是十进制,因此相对位移直接加上数字即可;

2.因此,如果起始地址 240,下一条指令为 243 ,这个时候偏移量 = 290 - 243 = 47 = 0000 0000 0010 1111B = 002FH

小端存放,则为 2FH,00H

3.其实地址 240,下一条指令 243,偏移量 = 200 - 243 = - 43 = 1111 1111 1101 0101B = FFD5H

小端,D5H,FFH

4.取址地址,是先 +1

2024年1月7日

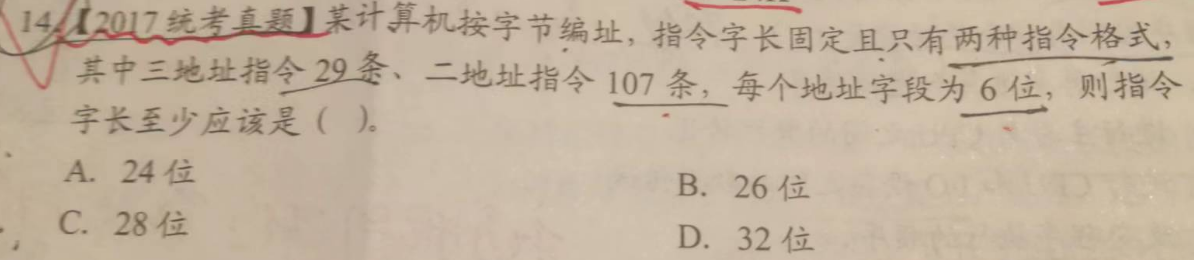

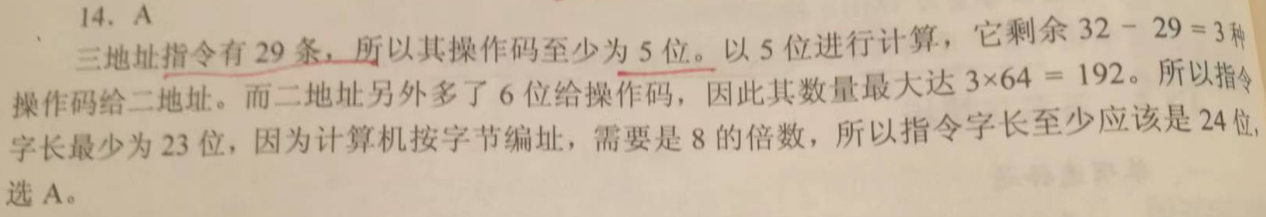

【2017】某计算机按字节编址,指令字长固定且只有两种指令格式,其中三地址指令 29 条,二地址指令 107 条,每个地址字段为 6 位,则指令字长至少应该是()。

A 24位 B 26 位 C 28位 D 32位

答案:A

解析:

1.首先,题目中“每个地址字段为 6 位” 、“指令字长固定” 即 “每段是6个比特”。

2.一级指令 29 条,需要 5 个比特。二级地址 107条,留给二级地址 (32-29) * 2^6 = 3 * 64 = 192 > 107

3.不难发现,留给二级地址是绰绰有余。因此 5 + 3*6 = 23位

按字节编址,故取整 24位。

这样就解题解完了吗?

三地址指令 OP+A1+A2+A3,共访问 4 次主存。

三地址指令,是同时存放三个地址在指令中。

针对 29条指令,需要 5 比特;剩余 32-29 = 3 比特,对应 3*64 = 192 比特(将 192 个条目的地址表分割成三份,并列放置);于是,依据三地址指令结构,应该是 5+6+6+6 = 23 位

又由于按字节编址,故为 24 位。

其他题目也显示,指令必须是 8 的整数倍。

【例题-1】

处理器共有 32 个寄存器,使用 16 位立即数,指令系统 142 条指令。

指令类型一个输入寄存器,一个输出寄存器,一个立即数寄存器。8比特 + 5比特 + 5比特 + 16比特 = 34 比特

映射到 8 的整数倍 ,于是留出 40位。

为什么要映射到 8 的整数倍?

答曰:8位的字节也是 计算机系统 中广泛采用的标准,包括许多通用计算机和 微处理器 。 使用8的倍数作为指令字长,可以提高计算机的兼容性和互操作性,使得软件和硬件的设计更加简单和统一

参考资料:

https://www.zhihu.com/question/619568863

https://zhuanlan.zhihu.com/p/368777813

【2011】偏移寻址通过将某个寄存器的内容与一个形式底子好相加来生成有效地址,下列寻址方式中,不属于偏移寻址方式的是()

A 间接寻址 B 基址寻址 C 相对寻址 D 变址寻址

答案:A

解析:间接寻址,即按照地址找对应内容。

【2017】下列寻址方式,最适合按下表顺序访问一位数组元素的是()

A 相对寻址 B 寄存器寻址 C 直接寻址 D 变址寻址

答案:D

解析:

1.使用过相对位移的,只有【基址寻址】和【变址寻址】

2.其中,基址寻址是对程序员透明的;变址寻址是程序员可以修改的;

【2009】某机器字长为 16 位,主存按字节 编址,转移指令采用相对寻址,由两个字节组成,第一字节为操作码字段,第二字节为相对位移量字段,假定取指令时,每取一个字节 PC 自动加 1 。若某转移指令所在主存字段地址为 2000H ,相对位移量字段的内容为 06H,则该转移指令成功转移后的目标 地址是()

A 2006H B 2007H C 2008H D 2009H

答案:C

解析:

1.首先,指令字长 16位,按字节编址,因此程序跳转下一条的时候, (PC) -> (PC)+2

2.某转移指令(无论是什么指令),在主存中位置 2000H ,为起始位置;

3.因此,位移 06H,起始位置 2000H。这条指令之后的一条指令位置 2000H + 2H = 2002H

加上相对位移,2002H + 06H = 2008H

故选择 C

【2011】某机器有一个标志寄存器,其中有进位/错位标志 CF、零标志 ZF、符号标志 SF 和溢出标志 OF,条件转移指令 bgt (无符号整数比较大于时转移)的转移条件是()

A CF + OF = 1

B SF_ + ZF = 1

C (CF+ZF)_ = 1

D (CF+SF)_ = 1

答案:C

解析:

1.本题主要针对【无符号整数比较大于时转移】

2.无符号,SF可以不看;大于,看 ZF;无符号比较,看CF。

所以两个无符号数比较大小,只需

要做减法,判断最高位是否产生了借位,从而判断大小。

3.综上,CF+ZF=0 ,因为 A- B 大于 0 ,没有进位,也不等于0。写成 (CF+ZF)_ = 1

以下是牛客网参考答案:

无符号整数比较,如A>B,则A-B无进位/借位,也不为0。故而CF和ZF均为0。

参考:

https://www.nowcoder.com/questionTerminal/2b43498ee92c43b1a9ef0ca3b8d6aec7

https://zhidao.baidu.com/question/878109899986685692.html

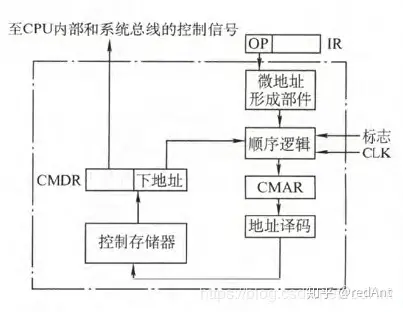

【一些补充知识】

微程序到底编写在哪里的?是写在硬件上的吗?

答曰:微程序是目前大多数 PC 采取的方案。CPU内部可以分为,控制器不见、执行部件。

微程序由微指令构成和,事先编写好放在 CM (控制存储区)中,一般是不可改写的。

控制存储器(CM)在 CPU 内部吗?

答曰:控制存储器(CM)用来存放实现全部指令系统的所有微程序,它是一种只读型存储器 .一旦微程序固化,机器运行时则只读不写。

控制存储器在CPU内,是CPU的组成部分。对应的 CMAR、CMDR。

控制存储器的容量为微指令数与字长的乘积。

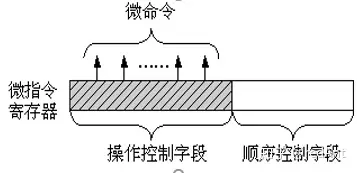

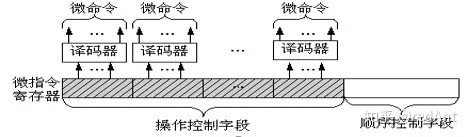

直接编码方式

字段直接编码方式

以下是笔者搜到的 微程序实验报告中的图:

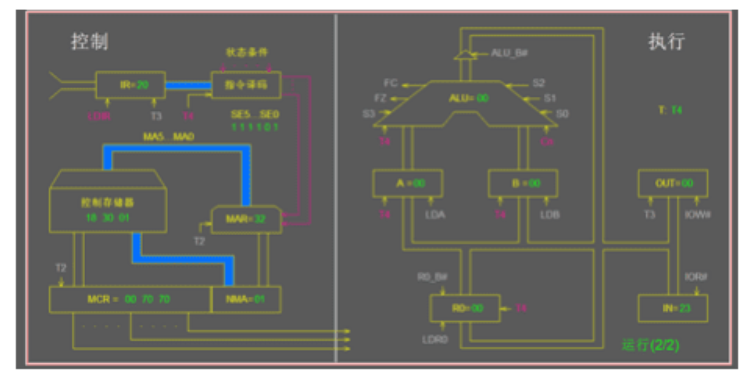

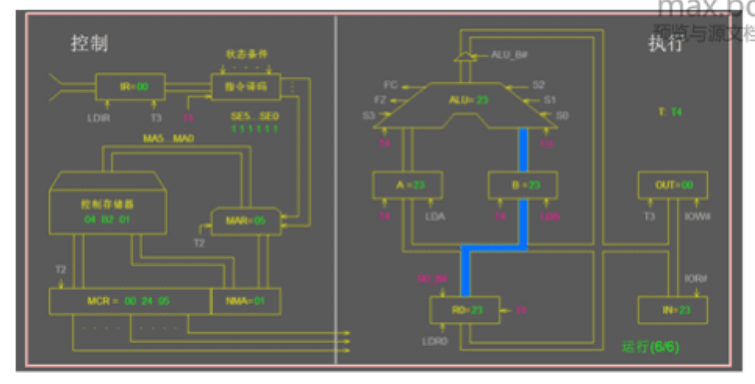

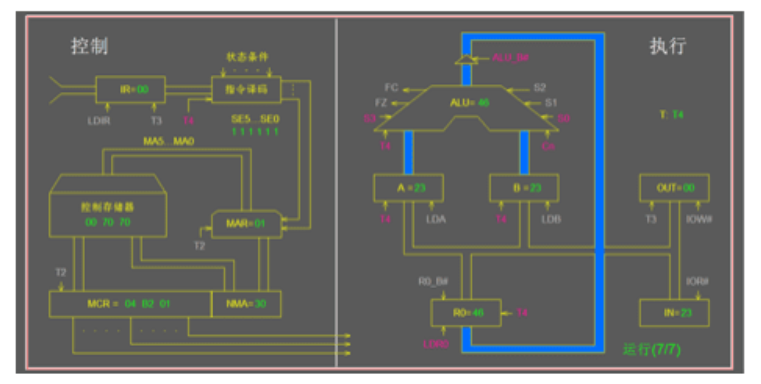

为了进一步了解,指令系统,到底在干什么?和 CPU 的关系。

看以下组图。

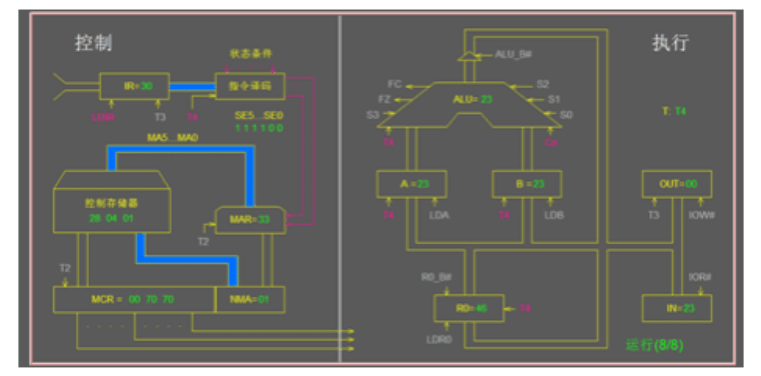

1. 左边是指令取址,以及译码,指令发出之后,如下所示:

2.CPU内部的工作,即操作数 1 传到 ALU 左端输入端;

3.CPU内部工作,操作数 2 从 ALU 右端输入;

4.ALU运算玩之后,输出到 R0 寄存器;

至此,指令可写为

(A1) Add (A2) -> R0 或者

add A1, A2(R0);

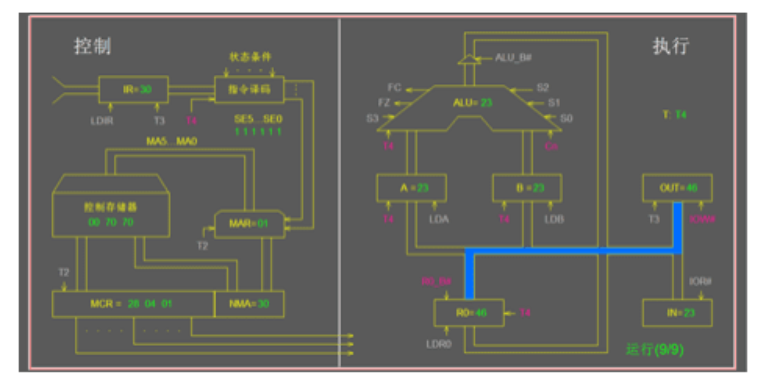

5.左边 CM 再次取址并译码 —— 因为 字太模糊,只翻译确认的部分。

6.结果从 R0 寄存器输出。

指令为

(R0) -> M

这一工作过程,可以看出,左边 CM 在完成一次运算需要取址几次,或者,取址一次,CPU内部要做多少个动作。

参考:

https://max.book118.com/html/2017/0220/92762791.shtm

2023年12月

关于地址计算的原题,图我就不撤了!!

关于间接寻址,获取地址内容还是地址。

12.数组用变址寻址,EA = (IX)+A

数组情况下,PC 只需要指向 (IX) 即可

15. 注意,题目告知获取一个字节 (PC) 自增一。

判错的依据,溢出OF=1,符号SF=1。因此,这个情况的补集,选择C。

答案:

17. 本题主要考指令字长,各个操作位的作用。

- 源操作数,存放寄存器,16 种可能;

- 目的操作数,存放寄存器,16 种可能。

21.题目

地址 = 1000H+2000H = 3000H

对应地址为 3000H,获取操作数 4000H

23.题目

如果变址直接寻址,(I)+D

如果变址间接寻址,((I)+D)

26. 这道题目主要就是编址,因为有一步操作,即 offset * sizeof(double) ,因此选择32

技巧,可以先算出 offset=256,存着的不是这个数值,而是 256/8 = 32 —— 就这么简单!

答案:

5.题目

- 主存大小 = 2^(17) B

- 字长 = 16 bit

答案:

ShoelessCai 解析

(1)

观察操作码的示意图。操作码位数 = 15 - 12 + 1 = 4 bit

一共可以表示 16 条指令;

11 - 6 + 1= 6 bit

寻址方式和寄存器个数没看懂。答案表示,2^(3) 表示寻址方式,但是王道书上介绍的寻址有 10 种,这样看来,是 2^(4) -- 留个疑问

寄存器个数也是留了 3 个位,于是连 8 个寄存器。

字长 = 16 bit = 2 字节

于是存储单元 个数 = 128 KB / 2字节 = 2^(16) 个

为了能够标出 2^(16) 个门牌号,需要 16 根 MAR

由于字长 16 位,所以 MDR 16 根。

(2)

这个指令寻址范围: 0 - 2^(16)-1 (由指令位数决定的)

主存单元数量:0 - 2^(16) 与寻址范围取交集,如果物理分割没那么多单元数,有再多 MAR 也没有

综上,转移指令的范围, 0 - 2^(16)-1

(3)

R4 内容 1234H , 写成 (R4) = 1234H

(1234H) = 5678H

(5678H) = 1234H

运行完指令

(R5) = 5679H

因为是 R5 寄存器指针往后移动,因此,推断加法结果存在 5678H

1234H + 5678H = 0001 0010 0011 0100 B + 0101 0110 0111 1000 B = 0110 1000 1010 1100 B = 68AC H

(5678H) = 58ACH

暂时先学到这种程度,我考完再来学习。

7.题目

答案:

回答:

(1)

指令长度 16 位,程序运行完之后,(PC) -> PC + 2 说明按字节编址

Offset = 8 bit 最多向后跳转 127 条指令,即 offset = 0111 1111

向前最多跳转 128 条, 即 offset = 1000 0000

(2)

CF || NF || ZF 时候转移

第一条指令,CF 0 ZF 1 NF 1 表示要检测后两位,由于题目中 后两位均为1,转移。

转移的含义,起始地址 + 2*offset + 2(字长16,按字节编址,转移目标地址,题目给出的!)

offset = 1110 0011B= E3H = FFE3H

2*offset = 1- 1- 1100 0110 B = FFC6H

转移地址 = 200CH + FFC6H + 0002H = 1FD4H (左边填充位,溢出的扔掉)

第二条指令,CF 1 ZF 0 NF 0 不检测后两位,需要检测的 CF=0,不转移。

不转移含义,起始地址 + 2

(3)

(4)

8.题目

前几年大概看到这类题我直接 SKIP 了

答案:

答案:B

汇编语言程序员可见的是程序计数器(PC),即汇编语言程序员通过汇编程序可以对某个寄存器进行访问。汇编程序员可以通过指定待执行指令的地址来设置 PC 的值,如转移指令、子程了提高指令执行速度,CISC 也往往采用流水线技术,因此流水线技术并非RISC 的专利。

* RISC 普遍用硬布线!!

ShoelessCai.com 值得您的关注!

?

(2)某条件转移指令的地址为 200CH ,指令内容如下图所示,若该指令执行时 CF=0,ZF=0,NF=1,则该指令执行后 PC 的值是多少?若该指令执行时 CF=1,ZF=0,NF=0,则该指令执行后 PC 值为多少?写出计算过程。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 无需6万激活码!GitHub神秘组织3小时极速复刻Manus,手把手教你使用OpenManus搭建本

· Manus爆火,是硬核还是营销?

· 终于写完轮子一部分:tcp代理 了,记录一下

· 别再用vector<bool>了!Google高级工程师:这可能是STL最大的设计失误

· 单元测试从入门到精通