计算机组成原理 —— CH3 存储系统 | 虚拟存储器

这篇文章我仍然会持续更新的。

2024年1月4日

之前我们整理过所谓的“多体存储”,更多是针对主存,即主存组织的方式,是 N路组相联,然后用 N根总线,可以实行比较好的并发度。这里的关键点是,涉及计算机的时候,计算好主存的工作一行的时间就是一个存储周期,区别在于一个存储周期内,并发度的差异。

这里我们看一道例题,是 Cache 采用组两联的模式。为啥要选择这道题目呢?就是更好地理解 Cache 组相联,进程是如何换入换出的。

【2009】某计算机Cache 有 16 块,采用二路组相联映射方式(即每组2块)。每个主存块大小为 32B,按字节编址,主存 129 号单元所在主存块应装入 Cache 组号是()

A 0 B 2 C 4 D 6

答案:C

解析:

1.129号单元,我们要获取信息,对应 Cache 内部 129个字节;

2.每一行 32B。129 / 32 = 4 …… 1因此,第 129 号从第5行开始放,即 4号 Cache 组。

【2012】假设某计算机按字编址,Cache有4行,Cache和主存之间交换的块大小为1个字。若 Cache 的内容初始为空,采用 2 路组相联映射方式和 LRU 替换策略,则访问的主存地址依次为 0,4,8,2,0,6,8,6,4,8 时,命中 Cache 的次数是()

A 1 B 2 C 3 D 4

答案:C

解析:

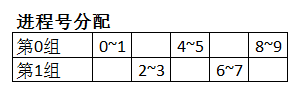

依据题意,我们发现 Cache 分组的时候,进程号分配到每个组的结果:

因此,真正跑进程的时候,是这样的:

总结:

这道题要注意,Cache 分组的时候,总的进程号的集合,要怎么分割,并且分配到对应组号。

P126

【地址映射表大小,什么意思?】

10.存储系统,主存容量是 Cache 容量的 4096 倍,Cache 被分成 64 个块,当主存映射地址和 Cache 映射地址采用直接映射方式时,地址映射表大小应为()

A 6x4097 bit

B 64x12 bit

C 6x4096 bit

D 64x13 bit

答案:D

解析:

1.【主存容量是 Cache 容量的 4096 倍】,即主存大小 / Cache 大小 = 2^12。留出 12 比特,表示有多少个主存块

2.主存块长度,64字节

3.地址映射表大小,含义即一串地址所映射的空间,有多少大?

综上,地址映射表大小为 64x13 bit,或者写得更加清晰一些,64B * 2^13 这是所有的 Cache 能容纳的量。

【2016】有如下 C 语言 :

for (k=0; k<1000; k++)

a[k]=a[k]+32;

若数组 a 和变量 k 均为 int 型,int 型数据占 4B,数据 Cache 采用直接映射方式,数据区大小为 1KB、块大小为 16B,该程序段执行前 Cache 为空,则该程序段执行过程中访问数组 a 的 Cache 缺失率为()

A 1.25% B 2.5% C 12.5% D 25%

答案:C

解析:

1.这道题要注意,a[ i ] = a[ i ] + 32 这句话要访问两次,一次是读取原来的 a[ i ] 的数据,第二次是将运算的结果存入 a[ i ]

2.上述两次访问,每经过 4 个数组元素,就要访问一次主存。之后的3个数据元素,两次访问,均在 Cache 访问即可。

3. 1000 个元素的数组,共访存 2000 次,其中,250次是缺失的。故 Cache 缺失率 = 250 / 2000 = 12.5%

综上,缺失率为 12.5%

【关于主存地址 和 Cache 地址】

王道单科书 2020年 Page 127

14. 对于高速缓存、主存、硬盘构成的三级存储体系,CPU 访问该存储系统时发送的地址为()

A 高速缓存地址 B 虚拟地址 C 物理地址 D 磁盘地址

答案:C

解析:

1.这道题考的是,主存地址就是 Cache 地址!主存地址就是 Cache 地址!主存地址就是 Cache 地址!

2.Cache地址到底怎么算的呢?

应该是二进制封闭性,依据主存块,Cache 行数,以及 倒轧出 Tag,重新分割主存地址的时候,必然能在 Cache 中找到数据。

【2014】采用指令 Cache 与数据 Cache 分离的主要目的()

A 降低 Cache 缺失损失

B 提高 Cache 命中率

C 降低 CPU 平均访存时间

D 减少指令流水线资源冲突

答案:D

解析:

1.这道题暂时用背的吧!

2.按照其他题目的 Info,Cache 如果分离指令和数据的话,【有效位+tag + Cache 数据】。如果 tag 剥离出来的话,这样可以识别不同的主存区域,提升流水线效率。

【2017】某 C 语言程序段如下:

for ( i=0; i<=9; i++ ) {

temp=1;

for ( j=0; j<=i; j++ ) {

sum += temp;

}

}

下列关于数组 a 的访问局部性描述中,正确的是()

A 时间局部性和空间局部性皆有

B 无时间局部性,有空间局部性

C 有时间局部性,无空间局部性

D 时间局部性和空间局部性皆无

答案:A

解析:

1. 程序一旦运行之后,部分数据会存在 Cache 中,空间局部性

2. 如果采用 LRU 之类的,可以认为采用时间局部性。循环语句本身就具有时间局部性。

【逻辑地址 v.s. 物理地址】

总结:逻辑地址依据 Cache 的映射需要;物理地址依据内存大小需要。

前者是,Cache 行数覆盖的 bit + 主存块内部覆盖的 bit

后者是,物理块数覆盖的 bit + 主存块内部覆盖的 bit

Page 127

17. 设有 8 页的逻辑空间,每页有 1024B,它们被映射到 32 块的物理存储区中,则按字节编址,逻辑地址的有效位是(),物理地址至少是()位。

A 10, 12

B 10, 15

C 13, 15

D 13, 12

答案:C

解析:

总结:逻辑地址依据 Cache 的映射需要;物理地址依据内存大小需要。

前者是,Cache 行数覆盖的 bit + 主存块内部覆盖的 bit

后者是,物理块数覆盖的 bit + 主存块内部覆盖的 bit

【2010】某计算机的主存地址空间大小为 256 MB ,按字节编址。指令 Cache 和数据 Cache 分离,均有 8 个Cache 行,每个 Cache 行大小为 64 B,数据 Cache 采用直接映射方式。现有两个功能相同的程序 A 和 B,其伪代码如下所示:

程序 A:

int a[256][256]

...

int sum_array1 () {

int i,j,sum=0;

for ( i=0; i<256; i++ )

for ( j=0; j<256; j++ )

sum += a[i][j];

return sum;

}

程序 B:

int a[256][256];

...

int sum_array2 () {

int i,j,sum=0;

for ( j=0; j<256; j++ )

for ( i=0; i<256; i++ )

sum += a[i][j];

}

假定 int 类型用 32 位补码表示,程序编译时,i, j, sum 分别在寄存之中,数组 a 按行优先方式存放,其收地址是 320 (十进制数)。回答下列问题:

(1) 不考虑用于 Cache 一致性维护和替换算法的控制位,数据 Cache 的总容量为多少?

(2) 数组元素 a[0][31] 和 a[1][1] 各自所在的主存块对应的 Cache 行号是多少(Cache 行号从 0 开始)?

(3) 程序 A 和 B 的数据访问命中率各是多少?哪个程序的执行时间更短?

解析:

(1) 8行,每块 64B,直接映射。Cache 总容量 = 8*64 = 2^9

数据 Cache 前还有几位表示 Tag,分别是 有效位、脏位、替换位、Tag,由于题目中说脏位和替换位不计。因此,数据 Cache 结构,有效位(1 bit) + Tag (19 bit) = 标记项

2^9 + 20bit * 8 = 512 B + 20 B = 532 B

(2)一行 64B,数据是 Int。

a[0][31] = ( 320 + 0 * 256 * 4 + 31 * 4 ) / 64B = 6……60

因此 Cache 号为 6号,即第 7 块;

a[1][1] = ( 320 + 1 * 256 * 4 + 1 * 4 ) / 64B = 21……4

逻辑上,22号块,放置在第 6 块主存块,故 Cache 号为 5 号。

(3)由于一个主存块放置 16 个元素,如果按列优先,即程序B,每次都不命中。

因为第一行装入 a[0][0] ~ a[0][15],但是第二个循环访问的是 a[1][0]

针对程序 A,每16个元素,访存一次,一共 16 次访存。

每 16 个元素,只有第一个元素不命中,因此命中率 15 / 16,整个数组命中率 16*15 / 16*16 = 93.75%

程序 A 要快很多,因为程序 B 有更多缺失率。

【2013】某32位计算机,CPU主频为 800MHz,Cache 命中时的 CPI 为 4,Cache 块大小为 32B;主存采用 8 体交叉存储方式,每个体的存储字长为 32 位、存储周期为 40ns;存储器总线宽度为 32 位,总线时钟频率为 200MHz ,支持突发传送总线事务。每次读突发传送总线事务的过程包括:送首地址和命令、存储器准备数据、传送数据。每次突发传送 32B,传送地址或 32 位数据均需要一个总线时钟周期。回答问题。

(1)CPU和总线的时钟周期各为多少?总线的带宽(即最大数据传输率)为多少?

(2)Cache 缺失时候,需要用几个读突发传送总线事务来完成一个主存块的读取?

(3)存储器总线完成一次都突发传送总线事务所需的时间是多少?

(4)若程序执行过程中共执行了 100 条指令,平均每条指令进行 1.2 次访存,Cache 缺失率 5%,不考虑替换等开销,则 BP 的 CPU 执行时间多少?

解析:

(1)总线时钟周期 = 1/200MHz = 5 ns

CPU时钟周期 = 1/800MHz = 1.25 ns

由于总线带宽总共是 32 位,因此 ,总线带宽 = 4B / 5ns = 4B * 200 MHz = 800 MHz

(2)Cache 缺失时候,需要一个读突发传送总线事务。

(3)一次读突发传送总线事务的时间 = 总线获取地址的时间(一个总线周期) + 主存交互的时间(存储周期) + 总线传输时间

读突发传送总线事务 = 5ns + 40ns + 8 * 5ns = 85ns

上述数值,8的含义为 8 体交叉存储,因为这些数据准备好之后,是一个一个传输的。

(4)访问 Cache,成功,或者不成功。

成功所需时间 = 总线传输周期 = 5ns

不成功所需时间 = 1.2 * 5% * 85 = 5.1 ns

访问 Cache 的平均时间 = 5ns + 5.1ns = 10.1ns

因此。100条指令的平均访问 Cache 的时间 = 10.1 * 100 = 1010 ns

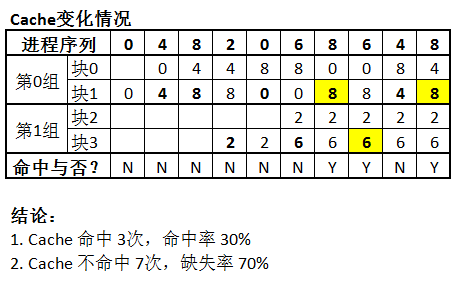

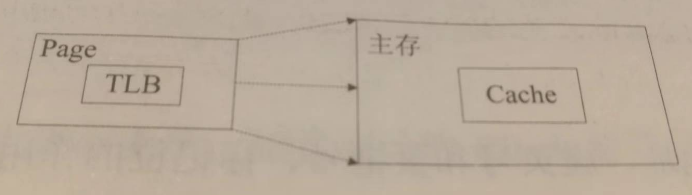

【2016】某计算机采用页式虚拟存储管理方式,按字节编制,虚拟地址为 32 位,物理地址为 24 位,页大小为 8 KB,TLB 采用全相联映射,Cache 数据区大小 64KB,按二路组相联的方式组织,主存块大小为 64 B,存储访问过程示意图,如图所示。

回答:

(1)图中 A~G 位各多少?TLB 标记中 B 的内容是什么?

(2)将块号 4099 主存块装入 Cache 时候,所映射的 Cache 组号是多少?对应的 H 字段内容是什么?

(3)是 Cache 缺失处理的时间开销大,还是缺页处理的时间开销大?为什么?

(4)为什么 Cache 可以采用直写策略?而修改页面内容总是采用回写策略?

解析:

(1)页内偏移 13bit,D=13,C=11,A=19

B=19

G=6

数据区大小 64KB,二路组相联,主存块大小 64B,64KB / (2*64B)= 9 bit, 覆盖块号;

F=9, E=9

Tag H = 9

(2)4099 = 1024*4 + 3 = 2^12 + 3 —— 注意到,这是具体到块号的

故 00 0001 000 0 0000 0011 B

块号 = 3

H = 00 0001 000B

(3)Cache 缺失带来的开销小,主存访问缺失带来的开销大。因为访问外存的代价很大。

(4)主要是因为外存和主存的速度差距较大,因此,虚拟存储技术,如果缺页,采用写回法;

Cache - 主存之间的速度差异较小,因此,缺失的话,采用直写法。

Page 129

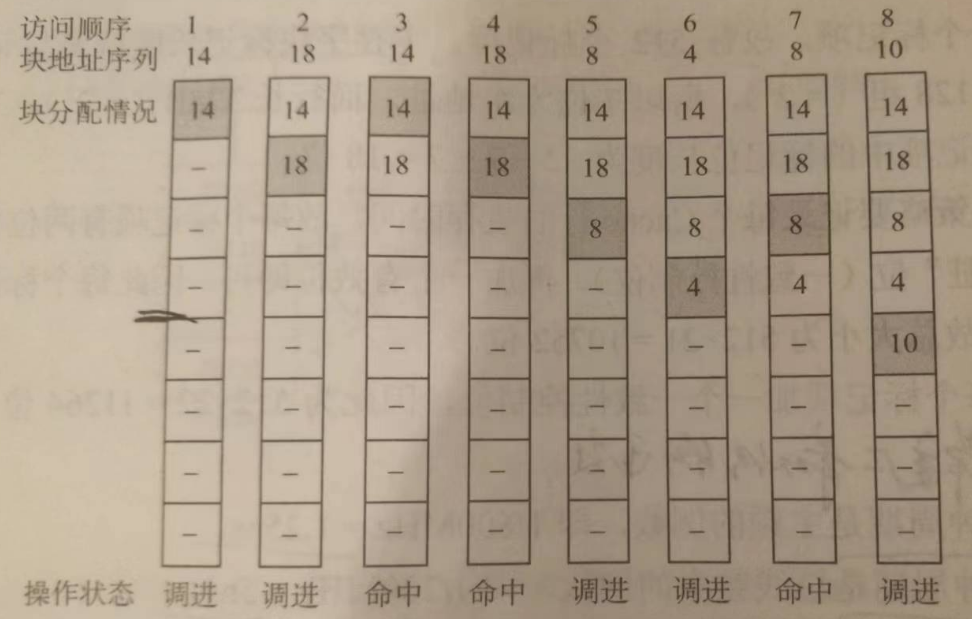

8. 有一全相联 Cache 系统,Cache 由 8 个块构成,CPU 送出的主存地址流序列,分别为 01110,10010,01110,10010,01000,00100,01000,01010。十进制为 14,18,14,18,8,4,8,10

(1)求每次访问后,Cache 的地址分配情况。

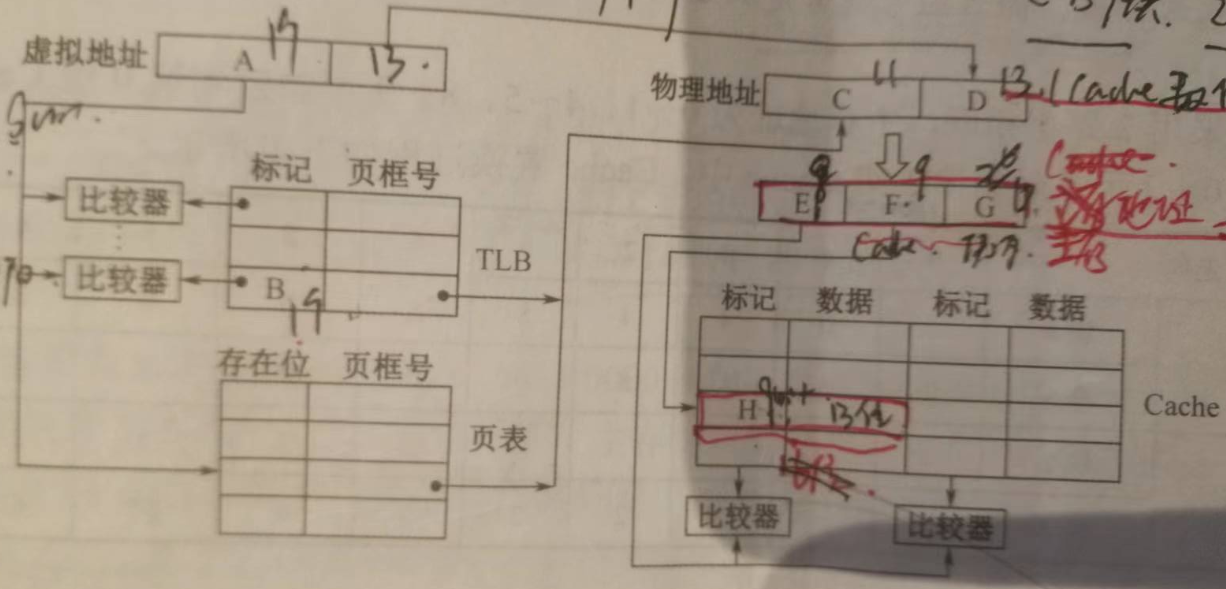

(2)当 Cache 的容量分成 4 个块,地址流为 6,15,6,13,11,10,8,7。求采用先进先出替换算法的相应地址分配和操作。

解析:

(1)这里虽然用 5 个比特,但是还是8个块。

(2)

【2010】下列命令组合的一次访存过程中,不可能发生的是()

A TLB 未命中,Cache 未命中,Page 未命中

B TLB 未命中,Cache 命中,Page 命中

C TLB 命中,Cache 未命中,Page 命中

D TLB 命中,Cache 命中,Page 未命中

解析:

TLB是页表的副本,因此 TLB 不命中,Page必然不命中。

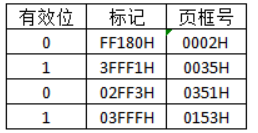

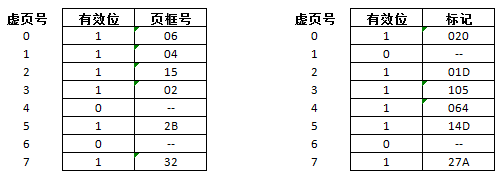

【2013】某计算机主存空间大小 256 MB,按字节编制,虚拟空间大小 4GB,采用页式存储管理,页面大小为 4KB,TLB(快表)采用全相联映射,有 4 个页表项,内容如下表所示:

则虚拟地址 03FF F180H,进行虚实地址变换的结果是()

A 015 3180H

B 003 5180H

C TLB 缺失

D 缺页

答案:A

解析:

1.逻辑地址空间 32 位。页面偏移 = 12比特,页表项位移 = 2比特,页目录号 = 18比特

2. 03FF F180H = 0000 0011 1111 1111 11 11 0001 1000 0000 B

【3号】页面,Tag = 03FFFH,有效位=1,因此在内存里面。

3.页内偏移 =180H,加上页框号 0153H

故物理地址 = 015 3180H

【2015】假定编译器将赋值语句 “ x = x + 3; ” 转换为指令 “add xaddr, 3”,其中 xaddr 是 x 对应的存储单元地址。若执行该指令的计算机采用页式虚拟存储管理方式,并配有相应的 TLB ,且 Cache 使用直写方式,则完成该指令功能需要访问主存的次数至少是()

A 0 B 1 C 2 D 3

答案:B

解析:取数时候可以不访主存

【2015】假定主存地址为 32 位,按字节编制,主存和 Cache 之间采用直接映射方式,主存块大小为 4个字,每字 32 位,采用回写方式,则能存放 4K 字数据的 Cache 的总容量的位数至少是()

A 146K B 147K C 148K D 158K

答案:C

解析:

1.主存块大小 = 4*32 = 128 bit = 16B —— 覆盖需要 4位

块数 = Cache 大小 / 主存块大小 = 4K * 32 / 128 bit = 2^17 / 128 = 2^10 块 —— 需要10个比特

Tag = 32 - 10 - 4 = 18 位

故主存字块标记 18位,注意,这里涉及【标记】直接翻译成【Tag】。

2.计算 Cache 总容量

这道题 指令 Cache + 数据 Cache,即数据 Cache 之前,加了 20 比特。

指令 Cache(一行):有效位(1位) + 脏位(1位) + Tag(18位)

指令 Cache = 2^10 * 20bit = 20K 位

数据 Cache = 4K* 32位 = 128K 位

故 Cache 总容量 = 指令 Cache + 数据 Cache = 20K + 128K = 148K 位

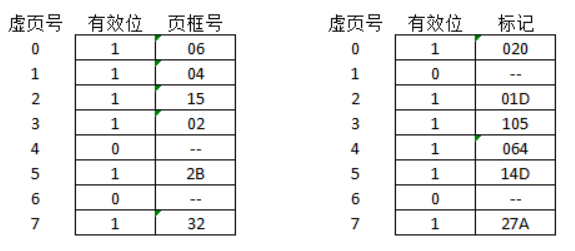

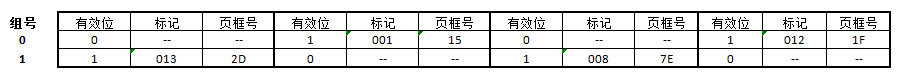

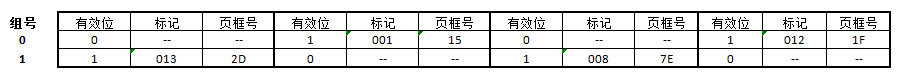

【2011】某计算机存储器按字节编址,虚拟(逻辑)地址空间大小为 16MB,主存(物理)地址空间大小为 1MB,页面大小为 4KB;Cache 采用直接映射的方式,共 8 行;主存与 Cache 之间交换的块大小为 32B。系统运行到某一时刻时,页表的部分内容和 Cache 的部分内容如下面的左图和右图所示,图中页框号及标记字段的内容为十六进制形式:

回答问题:

(1)虚拟地址共有几位?哪几位表示虚页号?物理地址共有几位?哪几位表示页框号(物理页号)?

(2)使用物理地址访问 Cache 时,物理地址应划分成那几个字段?要求说明每个字段的位数,及物理地址中的位置。

(3)虚拟地址 001C60H 所在的页面是否在主存中? 若在主存中,则该虚拟地址对应的物理地址是什么?访问该地址时是否 Cache 命中?要求说明理由。

(4)假定为该机配置一个四路组相联的 TLB,共可存放 8 个页表项,若其当前内容(十六进制)如下图所示。则此时虚拟地址 024BACH 所在的页面是否在主存中?要求说明理由。

注:灰色只为了便于识别

解析:

(1)虚拟空间 16MB = 2^24 bit;物理空间 1MB = 2^20 bit;页面大小 = 4KB = 2^12 bit

虚页号 = 12 bit ; 页框号 = 8 bit

(2)主存物理地址 页框号 + 页内位移。共 20比特

如果是Cache,主存块大小 32B,Offset = 5;因为 8 行 Cache 行 ,Index = 3;Tag = 12 bit

主存地址,映射 Cache : Tag 12 + Index 3 + Offset 5 。含义,标记,主存块号,主存块内偏移

(3)由地址结构可知,虚页号 = 001,页内偏移 = C60H。

虚页号=1 ,页框号=04,有效位=1。物理地址 04C60H = 0000 0100 1100 011 0 0000 B

Cache行号 = 3,Tag = 105,有效位=1。但是 105H != 04H ,因此未命中。

【Takeaway】依据 Cache 行号找到表格,有效位为1 还不够,还需保证 Tag 和主存地址的 Tag,内容是一致的。其位数必然是一致的。

(4)这道题很有意思!

一共有 8 个页表项,四路组相联,故分为 2组。此时,应该在 Tag 的右边留出一位,作为组号。

虚拟地址 = 0000 0010 010 0 1011 1010 1100 B

也是因为留了右边的一个比特,作为组号表示,变相地右移了。

左边的 Tag = 0000 0001 0010 = 012H

查表发现 012H 对应的有效位为 1 。故在主存中,页框号 1F,物理地址 1FBACH。

物理地址的十进制算法

物理地址 = 页框号 * 页面大小 + 页内偏移

2023年12月 内容

1. 虚拟存储器

主要是采用局部性原理,将主存、外存地址空间同一编址,形成庞大的地址空间,在这个空间内,用户可以自由编程,而不必在乎实际主存容量和主存中实际存放的位置。

2.页式虚拟存储器

3.段式虚拟存储器

4.段页式虚拟存储器

5.快表(TLB)

访问主存查页表,再访问主存取得数据。

快表只是慢表的一个副本,而且只存放了慢表中很少的一部分。

虚拟存储器 —— 考研重点

* 选择题、大题都会出现。

*

【2010】下列命令组合的一次访存过程中,不可能发生的是()

A TLB 未命中,Cache 未命中,Page 未命中

B TLB 未命中,Cache 未命中,Page 命中

C TLB 命中,Cache 未命中,Page 命中

D TLB 命中,Cache 命中,Page 未命中

答案:D

解析:

1.关于 Cache 和 TLB

快表 (TLB) 是存在 主存里的。但是,TLB 的内容,是 Page 副本。Page 存在 外存里的。

同样地,Cache 是存在 CPU里的。但是,Cache 内容是主存的一个副本。

2.这些主体查询方式

- 如果命中 Cache,无需调用主存内容。

- 如果 Cache 不命中,TLB(主存中的)命中,直接与主存交互。注意,TLB命中的情况下,Page一定命中;

- TLB 不命中,再去检查 Page

【2013】某计算机主存空间地址大小为 256MB,按字节编址。虚拟地址空间大小为 4GB,采用页式存储管理,页面大小为 4KB, TLB(快表)采用全相联映射,有 4 个页表项,内容如下表所示:

则对虚拟地址 03FF F180H 进行虚实地址变换的结果是()

A 015 3180H

B 003 5180H

C TLB缺失

D 缺页

答案:A

解析:

1.页面大小 4KB,于是,页内地址 12位;

地址空间大小 4GB,虚拟地址 32位;

前 20 位页号。

2.虚拟地址 03FFF180H

页号 = 03FFFH

页内 = 180H

3.表格中 03FFFH 对应 0153H 为页框号

于是 变换结果 0153 180H

【2015】假定主存地址32位,按字节编址,主存和Cache之间采用直接映射方式,主存块大小为 4 个字,每字 32 位,采用回写方式,则能存放 4K 字数据的 Cache 总容量位数至少是()

A 146K

B 147K

C 148K

D 158K

答案:C

解析:

今天花了 40 分钟左右的时间,讲述业务问题。主要供大家参考吧。

1.【主存地址 32 位】这句话含义,意味着表示 【门牌号的 SLOT 有 32 个,即用 32 bit 表示 index + tag + offset 】。接着,怎么区分 index + tag +offset

2.首先是 offset ,主存块大小 4 个字,每个字 32 位,于是内部寻址空间 4 * 32 = 16B ,该空间需要占据 4 位。因此 offset = 4

其次 ,tag 应该显示 Cache 行数。即有多少行,就留出多少bit。

3.Cache 能存放 4K个字,即 Cache 容量至少 4KB,主存块大小是 4个字(4B)。于是,Cache 行数 = 4KB / 4B = 1K = 2^(10) 行

所以 tag = 10

最后推出 index = 32 - 10 - 4 = 18 BTW 从题目之后的信息看,18位不作什么用处的。

4.除了不起作用的 index 之外,再留 1 位脏位、1 位有效位。

所以,每行留出 18 + 1 + 1 = 20 bit 用于其他用处。

总共占据 20 bit * 2^(10) = 20K bit

5.Cache 可存放 4K 字 ,即 4K * 32 bit = 128K bit

综上 20K bit + 128K bit = 148K bit

【注意】

A 主要识别 Cache 可容纳 4K 字 —— Cache 存储容量

B Cache 总容量 = 存储容量 + 标记阵列容量

C 每一行 18+1+1+ 4*32 bit

行数 = 2^(10)

【2011】某计算机存储器按字节编址,虚拟(逻辑)地址空间大小为 16 MB,主存(物理)地址空间大小为 1MB ,页面大小为 4KB;Cache 采用直接映射方式,共 8 行;主存与 Cache 之间交换的块大小为 32 B。系统运行到某一时刻时,页表的部分内容和 Cache 的部分内容分别如下面的左图和右图所示,图中页框号及标记字段的内容为十六进制形式。

回答下列问题:

(1)虚拟地址共有几位,哪几位表示虚页号?物理地址共有几位,哪几位表示页框号(物理页号)?

(2)使用物理地址访问 Cache 时,物理地址应划分成哪几个字段?要求说明每个字段的位数及物理地址中的位置。

(3)虚拟地址 001 C60H 所在的页面是否在主存中?若在主存中,则该虚拟地址对应的物理地址是什么?访问改地址时,是否 Cache 命中?理由。

(4)假定为该机配置四路组相联 TLB,共可存放 8 个页表项,若其当前内容(十六进制)如下图所示,则此时虚拟地址 024BACH 所在页面是否在主存中?理由。

解答:

before start

(A)虚拟 2^(24) B

物理地址空间 2^(20) B

页面大小 2^(12) B

【主存与 Cache 之间交换的块大小为 32 B】=主存块 32 B

Cache ,tag = 3, offset = 5 按字节编址

Cache 大小 = 8 * 32B = 256B = 2^(8) B

初步结论:只能有部分 页面 进入 Cache

哪些是物理页号?

开始答题:

(1)虚拟地址共有几位,哪几位表示虚页号?物理地址共有几位,哪几位表示页框号(物理页号)?

页内地址 12 位;

虚拟地址 24 位,高 12 位虚页号;

物理地址 20 位,高 8 位为 页框号(物理地址) 。

(2)使用物理地址访问 Cache 时,物理地址应划分成哪几个字段?要求说明每个字段的位数及物理地址中的位置。

都是进程选择,因此 物理地址 20位用于映射Cache。

由于 8 行芯片,tag = 3

由于 32 B 主存块, offset = 5

index = 20 - 3- 5 = 12

(3)虚拟地址 001 C60H 所在的页面是否在主存中?若在主存中,则该虚拟地址对应的物理地址是什么?访问这个地址时,是否 Cache 命中?理由。

虚拟地址 0000 0000 0001, 1100 0110 0000

虚页号 01,页框号 04,木有标记,说明没有命中 Cache。

物理地址 = 0000 0100, 1100 0110 0000 = 04C60H

(4)假定为该机配置四路组相联 TLB,共可存放 8 个页表项,若其当前内容(十六进制)如下图所示,则此时虚拟地址 024BACH 所在页面是否在主存中?理由。

四路组相联,TLB 8 行,组数 = 8 / 4 = 2 组

留出低位 1 位表示组号,高11位,虚页号。

虚地址 = 0000 0010 010,0, 1011 1010 1100

虚页号 = 012H (高位补零) 组号 = 0 —— 去 TLB中找。之前两表是地址映射。

命中 TLB,有效位=1,页框号 = 1F。说明在主存中。

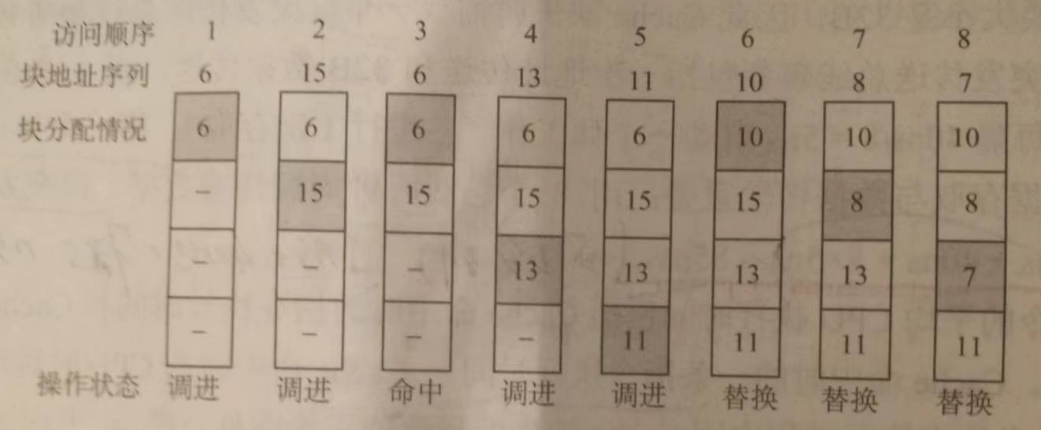

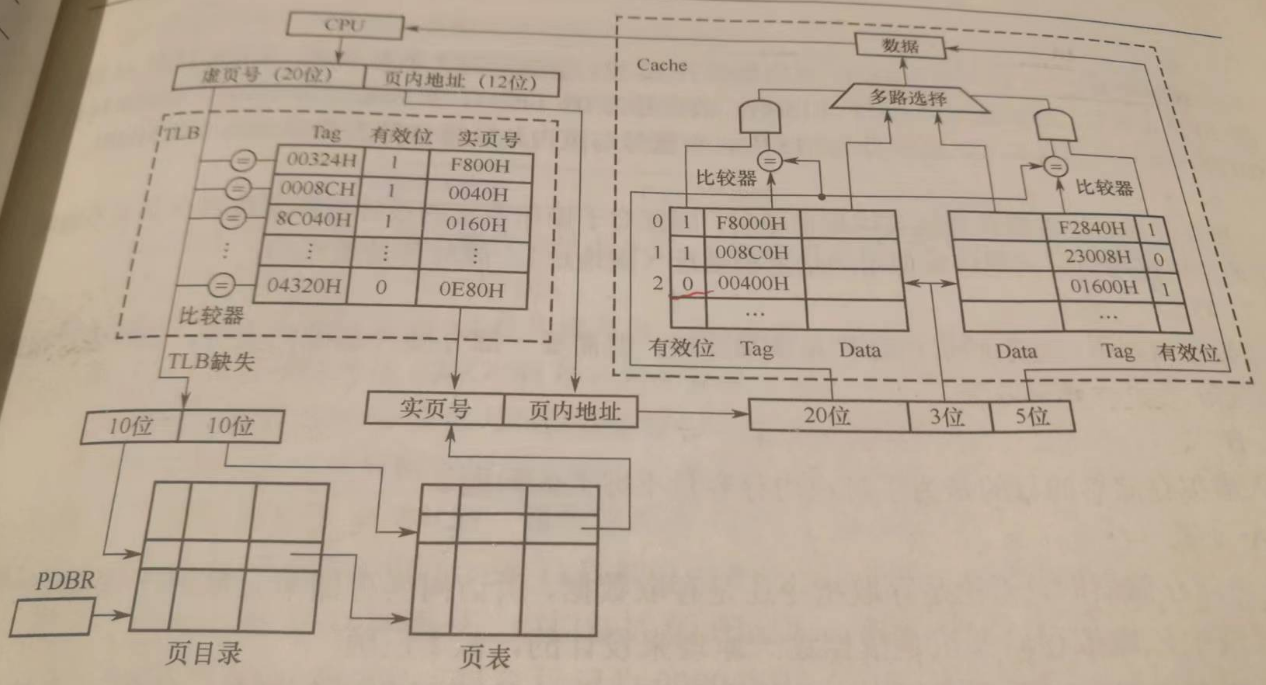

【2018】某计算机采用页式虚拟存储管理方式,按字节编址。CPU进行存储访问的访问的方式如下图所示,根据该图回答。

问题:

(1)主存物理地址占据多少位?

(2)TLB 采用什么映射方式?TLB 是用 SRAM,还是用 DRAM 实现?

(3)Cache 采用什么映射方式?若 Cache 采用 LRU 替换算法和回写策略,则 Cache 每行中除数据(Data)、Tag 和有效位外,还有哪些附加位?Cache 总容量是多少?Cache 中有效位的作用是什么?

(4)若 CPU 给出的虚拟地址为 0008 C040H,则对应的物理地址是多少?是否在 Cache 中命中?说理由。若 CPU 给出的虚拟地址为 0007 C260H,则该地址所在主存块映射到的 Cache 组号是多少?

回答:

(1)物理地址由实页号决定

实页号 + 页内地址

其中,实页号 16 位,页内 12 位。物理地址 28 位。

(2)TLB全相联映射,原因应该是一整块数据搬入。

材料用的是 SRAM,非易失性存储器,无需刷新,造价高,用于高速存储。

也是因为 TLB 是用于省时间的,因此用 DRAM 还有刷新等问题。

(3)二路组相联。

LRU 需要 1比特做记号,回写策略,1比特脏位。脏位=1,需要写回内存。

tag = 20

index = 3

offset = 5

【注意】贴 Tag 最容易,Tag 放在最左边。

Cache 组数 = 8组

每组 2 个芯片

数据位1,脏位1,LRU标记1.

每一个芯片 = 20bit + 32 * 8bit

于是 Cache 总容量 = 8*2*(20+ 32*8+1+1+1) = 4464 bit

(4)实页号 + 页内 = 0040 040H = 0000 0000 0100 0000 0000, 010, 0 0000 B

Tag = 00400H

组号=2

因为对应行显示有效位 = 0,所以不命中。 —— 并不是找到对应行就命中

虚拟地址 = 0007 C260H

offset = 260H = 0010 0110 0000 B —— 主要后 8 位

Cache 组号 = 011 = 3

映射到 Cache 组号 3。 —— 本题目 Takeaway ,即使TLB未命中,也能找到 Cache 记录。

ShoelessCai.com 值得您的关注!

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 分享一个免费、快速、无限量使用的满血 DeepSeek R1 模型,支持深度思考和联网搜索!

· 基于 Docker 搭建 FRP 内网穿透开源项目(很简单哒)

· 25岁的心里话

· ollama系列01:轻松3步本地部署deepseek,普通电脑可用

· 按钮权限的设计及实现