计算机组成原理 - 存储系统

本章节的学习还是以梳理历年真题为主。

【2011】 下列各类存储体中, 不采用随机存取方式的是()

A EPROM

B CD-ROM

C DRAM

D SRAM

答案: B

* 主存 - 辅存 构成 “虚拟存储系统”。

接下来,练习一道非真题。

P 94

问题:CPU 执行一段程序时,Cache 完成存取的次数为 1900 ,主存完成存取的次数 100,已知 Cache 存取周期 50ns,主存存取周期 250 ns。设主存与 Cache 同时间访问。

(1)Cache-主存系统效率。

(2)平均访问时间是多少。

解答:

(1)Cache 命中率 H = Cache Hit / (Cache Hit + Memory Hit) = 1900 / (1900 + 100) = 95%

平均访问时间 = 0.95 * 50 ns + (1-0.95) * 250 ns = 47.5 ns + 12.5 ns = 60 ns

系统效率 = Cache访问时间 / 平均访问时间 = 50 / 60 = 83.3%

(2)平均访问时间 = 60ns

注意公式:

- Cache Hit-rate= Cache Hit / ( Cache Hit + Memory Hit )

- 记住“Cache 命中率 = Cache命中次数 / (Cache命中次数 + Memory命中次数)”。

- 平均访问时间 = Cache hit-rate * Cache Time + ( 1 - Cache hit rate ) * Memory Time

【2014】某容量为 256MB 的存储器由若干 4M X 8 位的 DRAM 芯片构成,该 DRAM 芯片地址引脚和数据引脚总数是()

A 19

B 22

C 30

D 36

答案:A

解析:

【2010】下列有关 RAM 和 ROM 的叙述中,正确的是()

(I)RAM 易失性存储器,ROM 是非易失性存储器

(II)RAM 和 ROM 都采用随机存储的方式进行信息访问

(III)RAM 和 ROM 都可用作 Cache

(IV)RAM 和 ROM 都需要进行刷新

A 仅 I 和 II

B 仅 II 和 III

C 仅 I, II 和 III

D 仅 II,III 和 IV

答案:A

解析:

1.Cache 造在 CPU 内部,用的是 SRAM。

2.ROM 无需刷新

【2012】下列关于闪存的叙述中,错误的是i()

A 信息可读可写,并且读、写速度一样快

B 存储元由 MOS 管组成,是一种半导体存储体

C 掉电后信息不丢失,是一种非易失性存储器

D 采用随机访问方式,可替代计算机外部存储器

答案:A

解析:

1.写,肯定是慢于读取的

【2015】下列存储器中,在工作期间需要周期性刷新的是()

A SRAM

B SDRAM

C ROM

D FLASH

答案: B

解析:

1.ROM不需要刷新

2.RAM中也是动态的 RAM 需要刷新。

* 主存储器 与 CPU 连接

* 位扩展,字扩展,位字同时扩展

* 片选信号: 1.线选法 2.译码片选法

* 存储器与 CPU 连接: 地址线、数据线、读写命令、片选线,四种连接。

【2009】某计算机主存容量为 64KB,其中 ROM 区为 4KB,其余为 RAM 区,按字节编址。现要用 2K x 8位的 ROM 芯片和 4K x 4 位的 RAM 芯片来设计该存储器,需要上述规格的 ROM 芯片数和 RAM 芯片数分别是()

A 1, 15

B 2, 15

C 1, 30

D 2, 30

答案:D

解析:

1.RAM 芯片作位扩展 4K x 4位 * 2

2.ROM 区域 4KB,RAM 区域 60KB

因此,#ROM = 2块; #RAM = 60 / 4 * 2 = 30块

选择 D

【2010】假定用若干 2K x 4位的芯片组成一个 8K x 8位的存储器,则地址 0B1FH 所在芯片最小地址()

A 0000H

B 0600H

C 0700H

D 0800H

答案:

解析:这道题目的关键是。一个比特对应着一块芯片。

1.位扩展 2K x 4位 * 2

2.需要 4 组芯片

3.[ 地址 XXXX 所在芯片最小地址 ] 含义,如果芯片从 0000H 开始放置,那么 0B1FH 所属的地址,是哪几号芯片。

4.一组两片,一行。另外,一块芯片 2^(11) ,一个 SLOT 一个字节(8bit)。于是:

第一行: 0000H - 07FFH

第二行: 0800H - 0FFFH

第三行: 1000H - 17FFH

第四行: 1800H - 1FFFH

5.本质上,第一行有 11个低位1

第二行,12个地位1

第三行,13个地位1

第四行,14个地位1

6.其中, 0B1FH = 0000 1011 0001 1111 B

由低到高的 12 个 SLOT = 1,因此属于第二行。起始地址 0800H,选择B 。

【2016】某存储器容量 64KB,按字节编址,地址 4000H - 5FFFH 为 ROM 区,其余为 RAM 区。若采用 8K x 4 位的 SRAM 芯片进行设计,则需要该芯片的数量是()

A 7

B 8

C 14

D 16

答案:C

解析:

1. 首先进行位扩展 8K x 4位 * 2

2. 共 64KB,即 2^(16) bit,ROM 区域大小 1FFFH = 2^(13) bit

RAM 大小为 2^16 - 2^13 = 7 * 2^13 字节 = 56KB

3.于是,组数 = 56KB / 8K = 7组

共计 7 * 2 = 14 块芯片。选择 C。

【2011】某计算机存储器按字节编址,主存地址空间大小为 64MB,现用 4M x 8位的 RAM 芯片组成 32MB 的主存储器,则存储器地址寄存器 MAR 位数至少是()

A 22位

B 23位

C 25位

D 26位

答案:D

解析:

1.MAR 位数,应该是留给芯片的 SLOT 的数量。

2.由于不同寻址方式,最稳妥,就是 一个 SLOT 连接一根地址线。SLOT 连到其他区域。

综上,#MAR = 64MB = 2^(26) 根

【注意】

1.通常题目都是,按字节编址,即 8 bit 一行。

2.偶尔,以 4B 编址,这类情况,芯片是字扩展,还是位扩展,还是混合呢?

3.芯片组合,主要考虑,有门牌号的放在一行,4B = 32 bit,即编号的比特一行 32 个,第二行第一个bit 再写个号码。

因此,此时,芯片 只要不是 32位的,都作位扩展,直至芯片存储单元和所需要的一致。

4.例如,需要 32K存储体,现在芯片规格 8K * 8 bit 。采用【位扩展】,即 8K * 8bit * 4。

芯片数量是一样的,关键是总线 连数据线引脚,还是地址线引脚。

【注意】

1.数据线 - 位扩展;地址线 - 字扩展

2.例如:24根地址线,32根数据线。512K * 8位 芯片,需要几片?

回答:

第一,数据线 32 根,即 32 位,因此 4块芯片一组;

第二,24根地址线,意味着 2^(24) SLOTs,一组芯片 512K = 2^(19)

需要芯片的组数 = 2^(24) / 2^(19) = 2^(5) = 32

每组芯片 4 块,共计 32 * 4 = 128 块。

【注意】

1.译码器由地址线连接,而且永远连接【高位】,连接哪一条呢?

2.连接的地址线,依据地位的地址线占用情况。即 先计算需要 字扩展的地址线,地位全部占据之后,再连接高位地址线。

上述,是综合各类资料。

【2018】 假定 DRAM 芯片中存储阵列的行数 r ,列数为 c,对于一个 2K x 1位的 DRAM 芯片,为保证其地址引脚数最少,并尽量减少刷新开销,则 r, c 的取值分别是()

A 2048, 1

B 64, 32

C 32, 64

D 1, 2048

答案:C

解析:

1.首先,“引脚数最少” ,即最少的芯片达到想要的效果 -- 怎样排列最有效率!!

2.其次,DRAM 采用地址复用技术。

尽量选用 行列 值差得不大的。

DRAM 按行刷新,因此 行数要少。存储芯片字长

3.综上,2K x 1位的芯片要怎么排列?

因为地址复用,所以 行和列数量要接近;

又由于 按行 读取,因此行数较少。

* 总线带宽 > 存储字长

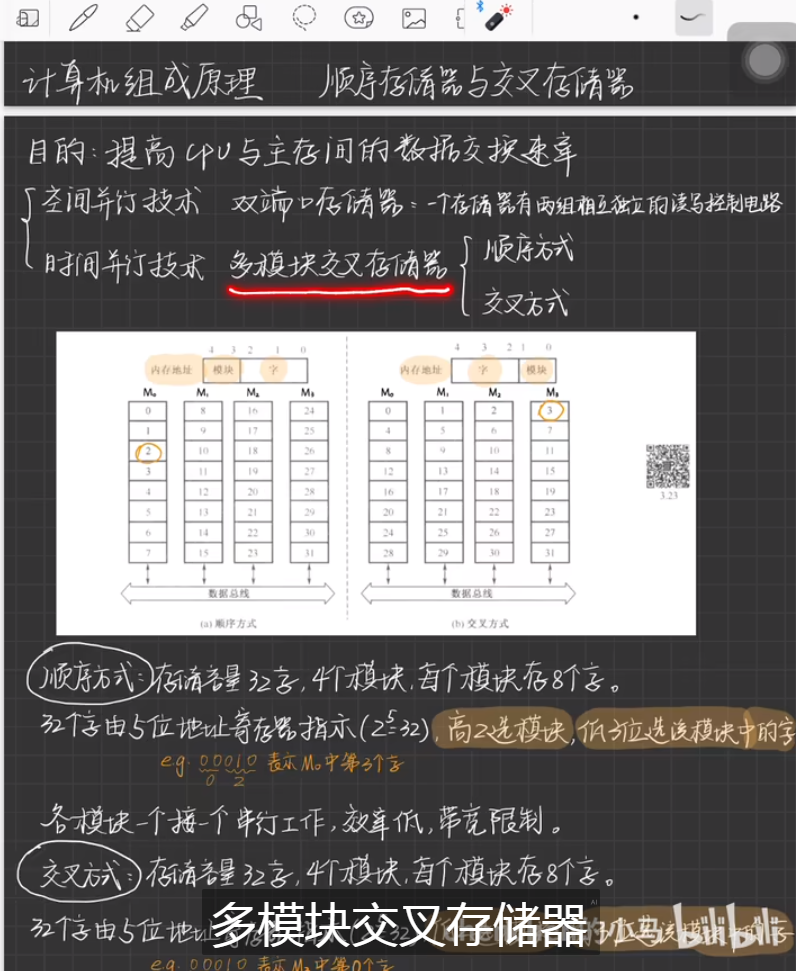

接着,几种提高 CPU 与 主存交互速率的技术。

多模块存储器(408考试重点)

2023年12月15日

复习集计算机组成原理,多模块存储体时候遇到困难。

如上图,先知道所谓的双端口 RAM 和 多模块存储体 其实是两种提升 CPU 主存交互的两种解决方案。

低位交叉多模块存储器,主要是模块化和并行。

一个存储周期内,可以同时读取好几个模块 —— 基本 IDEA

例题-1:存储体存储周期 110 ns,总线传输周期(存取周期)为 10 ns,采用低位交叉编址的多模块存储器时,存储体数应该是()

A 小于 11

B 等于 11

C 大于 11

D 大于等于 11

答案:D

解析:

1.模块个数 = 存储周期 / 总线传输周期 = 11个

2.模块个数 大于等于 11

例题-2:四体并行低位交叉存储器,每个模块容量 64K x 32 位,存取周期 200ns,总线周期(存取时间/存取周期) 50ns,下述说法正确的是()

A 在 200 ns 内,存储器能向 CPU 提供 256 位二进制信息

B 在 200 ns 内,存储器能向 CPU 提供 128 位二进制信息

C 在 50 ns 内,每个模块能向 CPU 提供 32 位二进制信息

D 以上均不对

答案:B

解析:

1.首先是模块的个数,个数 = 200 ns / 50 ns = 4

2.4 * 32 位 = 128 位。即 1 个存储周期内可以 传输 128 位信息。数据总线 32 根,用逻辑门,分成 128 位信息。

这两道题搞懂,应该是算是基本理解 how it works

【2015】某计算机使用四体交叉编址存储器,假定在存储器总线上出现的主存地址(十进制)序列为 8005,8006,8007,8008,8001,8002,8003,8004,8000,则可能发生访存冲突的地址是()

A 8004, 8008

B 8002,8007

C 8001,8008

D 8000,8004

答案:D

解析:

1.四体低位交叉

8000, 8001, 8002, 8003

8004, 8005, 8006, 8007

8008

2.冲突地址怎么识别?

考察前后紧邻的地址序号,是否在同一列上。

3.注意到:

第一列,8000,8004,8008,是否有紧邻的。有 8004,8000。

第二列,8001,8005 是否紧邻? 没有。

第三列,8002,8006 是否紧邻? 没有。

第四列,8003,8007 是否紧邻? 没有。

故选择 D 。

【2017】某计算机主存按字节编址,由 4 个 64M x 8位 的 DRAM 芯片采用交叉编址方式构成,并与宽度为 32 位的存储器总线相连,主存每次最多读写 32 位数据。若 double 型变量 x 的主存地址为 804 001AH ,则读取 x 需要的存储周期数是 ()

A 1 B 2 C 3 D 4

答案:C

解析:

1.首先,知道 x 主存地址 1000 0000 0100 0000 0000 0001 1010

2.最低 2 位 “10”,说明从编号为 2 的芯片开始存。如下所示:

芯片0 芯片1 芯片2 芯片3

XXXX XXXX 1000 0000

0100 0000 0000 0001

1010

3.因为存储的芯片编号2,因此要读 3 个周期。

4.为什么变量的最低两位显示存储芯片的编号?

因为,4块 低位交叉的芯片模式。在计算机编址技术规则下,最低两位拿出来用作【体号】。BTW,如果是高位交叉,则是最左边两位拿出来作为【体号】。

Cache 高速缓存储器

1.Cache 每块由若干个字节组成,块长,或者称为 “行长”。

2.如果 CPU 选择同时访问 Cache 和 主存的,如果 Cache 命中,则停止访问主存。否则,停止访问主存,并替换 Cache。

3.替换 Cache 还分为全写法(write through) 和 写回法(write back)。

Cache 命中率

Cache_hit_rate = #Cache_hit / ( #Cache_hit + #Memory_hit )

Cache - Mem 平均访问时间

Cache - Mem Average Time = Cache_hit_rate * T_cache + ( 1 - Cache_hit_rate ) * T_Mem

Cache - Mem 映射方式

1.直接相联映射

Cache 块号,在 Mem 里也是按照 Cache 块号一一对应。

2.组相联映射

Cache 分组,Mem 里是按照组号编号。例如,Cache分成 4 组。那么,Mem 里 0, 4, 8 对应同一块 Cache。

Cache 替换算法

1.随机替换

2.先进先出 FIFO

3.最近最少使用 LRU。用 count,命中一次,count = 0

4.最近最不常使用 LFU。用 count, 新建立时候 count=0,被访问一次,count++

替换 Cache 写策略

1.全写法

写命中,同时写入 Cache 和 主存。

2.写回法

写命中,修改 Cache;换出时候,Cache 内容写回主存。

【2009】假设某计算机的存储系统由 Cache 和主存组成,某程序过程中访存 1000 次,其中访问 Cache 缺失(未命中)50次,则 Cache 的命中率是()

A 5% B 9.5% C 50% D 95%

答案:D

解析:

1.根据公式 Cache_hit_rate = #Cache_hit / ( #Cache_hit + #Mem_hit ) = #cache_hit / #total

Cache_hit_rate = (1000 - 50) / 1000 = 95%

2.注意公式中,是命中次数,并非缺失次数。

选择 D

【2009】某计算机的 Cache 共有 16 块,采用二路组相联映射方式(即每组 2 块)。每个主存块大小为 32 B,按字节编址,主存 129 号单元所在主存块应装入的 Cache 组号是()

A 0 B 2 C 4 D 6

答案:C

解析:

1.注意到 主存大小 = 2^(5) B

一块主存块,编号最多 0 - 31

第 129 号主存,在第 5 个主存块中。此前,分别为 0-31, 32- 63, 64-95, 96-127,128(0) 129(2)。

2.由于二路组,因此129 对应 4 号。

注意:

按照答案,组号编号 0,2,4,6,8,10,12,14

主存中对应模式,每个 主存块 可以放 4 轮Cache,如下:

0(0),1(2),2(4),3(6),4(8),5(10),6(12),7(14)

8(0),9(2),10(4),11(6),12(8),13(10),14(12),15(14)

16(0),17(2),18(4),19(6),20(8),21(10),22(12),23(14)

24(0),25(2),26(4),27(6),28(8),29(10),30(12),31(14)

……

128(0),129(2)

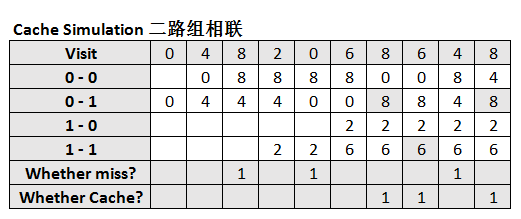

【2012】假设某计算机按字节编址,Cache 有 4 行,Cache 和主存之间的交换块大小为 1 个字。若 Cache 内容初始为空,采用 2 路组相联映射方式和 LRU 替换策略,则访问的主存地址依次为 0,4,8,2,0,6,8,6,4,8 时,命中 Cache 次数是()

A 1 B 2 C 3 D 4

答案:C

解析:

1.Cache 4行,二路组,说明如图所示。

1个字 = 32 bit

主存地址 0-1,2-3,4-5,6-7,8-9(64 bit)

其中,

第 0 组,0-1, 4-5, 8-9

第 1 组,2-3, 6-7

【注意】这里主存地址的编号,因为主存地址序列如此。每个编号对应一个字。

2.二路组相联,Cache 命中情况

* CPU 与 Cache/主存 之间交互,单位为 "字";

* Cache 与主存之间交互,单位 "块"

* 页面失效率 = 缺失次数 / 作业数

具体到题目,页面缺失率 = 6/20 = 30%

注意,首次进入的作业,如果木有 HIT 到,也要计入 缺页。

* 主存和 Cache 怎么映射?

1.计算主存有多少个地址位。通常,都是低位的若干位表示 Cache 内部地址;

2.Cache 内部的行号,和一行内部的位置。用低位表示。

3.Cache 和主存的地址映射,一定要很熟悉。

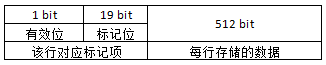

地址映射表大小

* 主存大小是 Cache 的 4096 倍

* Cache 行数 64 行

* 显然,要映射出 Cache 大小,需要 12 个bit

* 需要 1 个bit,表示有效与否

* 地址映射表的大小 = 64 * 13 bit

关于 Index, Tag, Offset 计算

* Cache 每组 8 * 16 B = 2^(7) B -- 这个做法是错误的

订正: Cache 组数 = 2^(3) SLOTs

* Cache 容量 = 2^(14 ) SLOTs

组数 = 2^(11) 组

主存地址 0001 0010 0011 0100 0101 0110 0111

注意:这里 offset + tag + index

* 重要指标

Offset = 3

Tag = 11

Index = 28 - 11 - 3 = 14

* 主存地址 000, 1 0010 0011 01, 00 0101 0110 0111

offset, tag, index

tag = 0000 0100 1000 1101 = 048DH

注意:

1.易错点,把内部 16B 也拆开来精确到字节,其实 offset 对应的单位的是 SLOT。这意味着,对应的芯片为单位。不用拆到字节。

2.易错点,低位交叉方案。 offset + tag + index

tag 左边位数不足的,补“0”。

3.最小单位,要么是字节,要么芯片。

【2016】如下 C 语言程序段:

for (k=0; k<1000l k++)

a[k] = a[k] + 32;

若数组 a 和变量 k 均为 int 型占据 4B,数据 Cache 采用直接映射方式,数据区大小为 1KB,块大小为 16B,该程序段执行前 Cache 为空,则该程序段执行过程中,访问数组 a 的Cache 缺失率约为()

A 1.25%

B 2.5%

C 12.5%

D 25%

答案:C

解析:

1.这段程序,有四个 整数,k, a[k],a[k], 32

2.读取某个变量时候,读取需要访存一次,计算后存结果再访存一次。共两次访存。

3.综上,4个未知变量,需要访存 8次,而只有首次访存的时候会产生缺页。其他其次可以直接获取变量值,缺页率 = 1/8 = 12.5%

4.这道题很多 info 是多余的!一定要知道考卷考什么。

本题目比较难,可以直接背出来!

【2014】采用指令 Cache 和 数据 Cache 分离的主要目的是()

A 降低 Cache 的缺失损失

B 提高 Cache 命中率

C 降低 CPU 平均访存时间

D 减少指令流水线资源冲突

答案:D

解析:直接背

【2017】某 C 语言程序段如下:

for ( i=0; i<=9; i++ ) {

temp=1;

for ( j=0; j<i; j++ ) temp *= a[j];

sum += temp;

}

下列关于数组 a 的访问局部性描述中,正确的是()

A 时间局部性和空间局部性均有

B 无时间局部性,有空间局部性

C 有时间局部性,无空间局部性

D 时间局部性和空间局部性皆无

答案:A

解析:

1.循环本身就是一种时间局部性。现在在运行的运算,很可能未来还需要运行;

2.空间局部性,某个变量自我迭代。

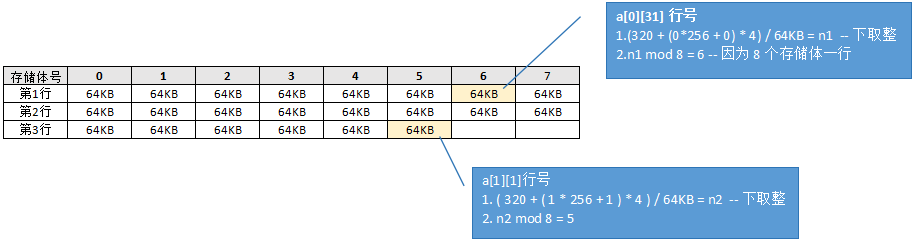

【2010】某计算机的主存地址空间大小 256MB,按字节编址。指令 Cache 和 逻辑 Cache 分离,均有 8 个 Cache 行,每个 Cache 行大小为 64B,数据 Cache 采用直接映射的方式,现有两个功能相同的程序A 和程序 B ,其伪代码如下所示:

假定 int 类型数据用 32 位补码表示,程序编译时,i, j, sum 均分配在寄存器中,数组 a 按行优先方式存放,其首地址为 320 (十进制数)。请回答下列问题,要求说明理由或给出计算过程。

(1)不考虑用于 Cache 一致性维护和替换算法的控制位,数据 Cache 的总容量为多少?

(2)数组元素 a[0][31] 和 a[1][1] 各自所在的主存块对应的 Cache 行号是多少(Cache 行号从 0 开始)?

(3)程序 a 和 b 数据访问命中率各是多少?哪个程序的执行时间更短?

答案:

(1)主存大小 = 2^(28) B

Cache 每行大小 = 2^(6) B

Cache 大小= 8 * 2^(6) + 20 = 532 B

(2)数组 a 按行存放,首地址 320 位,数组占 4B。

a[0][31]: 所在 Cache 第几行?

a[1][1] 所在 Cache 第几行?

这道题目我想了蛮久的,氧气还耗尽了!于是昨天又睡了 5 个小时i!!HAHA

现在成果来了!

(3)命中率不会,直接跳掉。

本题数组应该是已然存在的,因此循环一次,只有区数一个动作。

因此先不纠结。

应该是按行存取的速度快(程序A),和硬件结构一致。

【2013】某 32 位计算机,CPU 主频为 800MHz ,Cache 命中时的 CPI 为 4,Cache 块大小为 32B;主存采用 8 体交叉存储方式,每个体的存储字长 32 位,存储周期为 40 ns;存储器总线宽度为 32 位,总线时钟周期频率 200 MHz,支持突发传送总线事务。每次读突发传送总线事务的过程包括:送首地址和命令、存储器准备数据、传送数据。每次突发传送 32B,传送地址或 32位数据均需要一个总线时钟周期。请回答,给出计算过程。

(1)CPU 和总线的时钟周期各为多少?总线的带宽(即最大数据传输率)为多少?

(2)Cache 缺失时,需要用几个读突发传送总线事务来完成一个主存块的读取?

(3)存储器总线完成一次读突发传送总线事务所需的时间是多少?

(4)若程序 BP 执行过程中共执行了 100 条指令,平均每条指令需进行 1.2 次访存,Cache 缺失率 5%,不考虑替换开销,则 BP 的 CPU 执行时间是多少?

答案:

(1)总线周期 = 1/总线频率 = 1/200MHz = 5 * 10^(-9) second/instruction = 5ns

CPU周期 = 1/主频 = 1 / 800MHz = 1.25 * 10^(-9) second/instruction = 1.25ns

总线带宽 = 32 bit/clock * 200 clock/second = 6400 bit/second = 800 Bps

(2)Cache 大小是 32 B,Cache缺失,用一个突发传送总线事务,读取一个主存块。

如果突发传输字节数只有16字节,此时需要传 2 次,不考虑传地址的字节占据。

来自知乎的回答。参考:

https://www.zhihu.com/question/370833548

猝发传输可以连续传送地址连续的数据,因此存取一连串数据的时候只要第一次发地址,后面直接传数据,减少了发地址的时间就增加了传输率

突发传送 32B,总线带宽 800 B/s

于是,突发传送需要时间 = 突发传送 / 总线带宽 = 32B / 800B/s = 0.04 (second)

(3)一次读突发 = 地址传送 + 数据传送 32B

A 传地址时间 = 1个总线周期

B 传数据时间 = 读取存储体时间 + 传数据时间

因为 8体交叉存储,需要 8 个时钟周期传输数据。

C 一次读突发 = 传地址时间(1个总线周期) + 读取存储体时间(存储周期) + 8 * 单个存储体事务时间

* 每隔 40 ns 刷新一次,刷新 8 个存储体,平摊在每个存储体时间 = 40 ns / 8 = 5ns

* 一次读突发总线事务总时间 = 5ns + 40ns + 8 * 5ns = 85 ns

(4)注意几个点

A CPU 额外开销由缺失造成,处理 一次额外事务 需要时间 85 ns

多少次额外事务呢?

平均每条指令,额外事务占据CPU执行 1.2 次,缺失率(执行无效的比例)

1.2 * 5% * 85 ns = 5.1 ns

B 每条指令 CPU 执行时间 = CPI * CPU周期(second/clock) = 4 * 1.25 ns = 5ns

C 一条指令的平均 CPU 执行时间 = 5.1 + 5 = 10.1 ns

D 程序一共 100 条 指令,程序执行时间 = 100 * 10.1 = 1010 ns

【2016】某计算机采用页式虚拟存储管理方式,按字节编址,虚拟地址为 32 位,物理地址为 24 位,页大小为 8KB;TLB 采用全相联映射; Cache 数据区大小为 64KB,按 2 路组相联方式组织,主存块大小为 64B。存储访问过程的示意图如下。

回答下列问题:

(1)图中字段 A - G 的位数各是多少?TLB 标记字段 B 中存放的是什么信息?

(2)将块号为 4099 的主存块装入 Cache 时,所映射的 Cache 组号是多少?对应的 H 字段内容是什么?

(3)是 Cache 缺失处理的时间开销大还是缺页处理的时间开销大?为什么?

(4)为什么 Cache 可以采用直写策略,而修改页面内容时总是采用回写策略?

答案:

在开始答题之前(只适用于不熟悉 知识点的同学),梳理出所有隐藏的条件。

1) Cache 行数

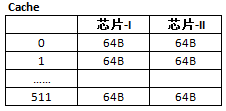

Cache 行数 = 64 KB / (2*64B) = 512 行

如图

2) 理论拨出多少主存?

一个物理地址连一个字节 B

一共可以连 2^(24) 个字节 = 16 MB

-- 符合本题的主存区域大小

3)主存可以容纳多少个 Cache?

#Supposed Cache =16MB / 64KB = 2^(24) B / 2^(16) B = 2^(8) 个 = 256 个

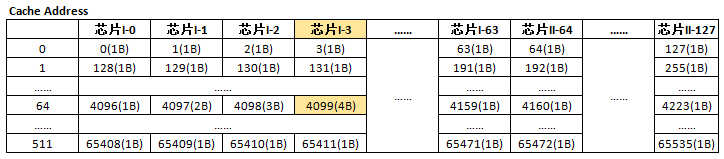

(1)页面大小 8KB,offset = 13 bit

物理地址 D=13

Cache 行数 = 64KB / (2*64B) = 512 行, tag = 9 即 F=9

由上述公式知道,一个单位(主存块)大小 64B = 2^(6) B , offset = 6 即 G = 6

由题目,C=11, A=19, E=9

(2)Cache 有 1024 块主存块,一块主存块 0-63。

4099 mod 64 = 3 Cache 组号 3

注意:也算是 Takeaway ,组号的含义,一行当中的编号,从 0 - 127。

关于计算机编址

* 按字节编址,就是增加1,地址增加 1B;

* 注意这个地址,是十进制。

具体到本题

因为 4099 是地址! 因此,我们的思路是,将 4099 写成二进制。

4099 = 4096 + 3 = 00 0001 0000 0000 0011 B

依据 index(9), tag(9)

4099 = 00 0001 000, 0 0000 0011 B

H字段对应 物理地址 中的 F,F = 0 0000 1000B

[H]内容 = 0 0000 1000B

【注意】

给出的地址,根据按字节编址,要对颗粒度有概念,这样就能知道 “ 增加 1 个单位时候,增加多少物理块 ” 。

(3)是 Cache 缺失处理的时间开销大还是缺页处理的时间开销大?为什么?

答:Cache 处理时间开销小,缺页处理开销大。因为缺页需要访问主存。

(4)为什么 Cache 可以采用直写策略,而修改页面内容时总是采用回写策略?

答:首先,“修改页面” 概念,即主存 - 外存交互。

其次,因为写外存慢很多,因此采用回写这种不同步操作会更省时间。Cache - 主存的写操作,同时修改的直写策略不会有太多时间差问题。

半导体随机存储器

(1)SRAM

静态 RAM,易失性存储器,断电即信息小时。

(2)SRAM

动态 RAM,非易失性存储器,每隔 2ms 刷新一次。地址线复用。

(3)ROM

ROM 中的信息不丢失,即使电源切断有不会主动丢失信息。

12/15 下午 1:30 果然不能通宵,一通宵白天只想睡觉。

【2014】某容量 256 MB 存储器由若干 4M x 8位 DRAM 芯片构成,该 DRAM 芯片的地址引脚和数据引脚总数()

A 19

B 22

C 30

D 36

答案:A

解析:

1.数据线 8 根

2.地址线数量 = lb( 4M ) = 22

3.DRAM 地址线复用,因此 使用 11根地址线

4.引脚数 = 8+11 = 19

【2010】下列有关 RAM 和 ROM 说法正确的是()

(I)RAM易失性存储器,ROM非易失性存储器

(II)RAM 和 ROM 都采用随机存取方式进行信息访问

(III)RAM 和 ROM 都可用作 Cache

(IV)RAM 和 ROM 都需要进行刷新

A 仅 I 和 II

B 仅 II 和 III

C 仅 I,II,III

D 仅 II,III,IV

答案:A

解析:直接记忆即可

【2012】下列关于闪存叙述中,错误的是()

A 信息可读可写,并且读写速度一样快

B 存储元由 MOS 管组成,是一种半导体存储器

C 掉电后信息不丢失,是一种非易失性存储器

D 采用随机访问方式,可替代计算机外部存储器

答案:A

解析:记忆即可

【2015】下列存储器中,在工作期间需要周期性刷新的是()

A SRAM

B SDRAM

C ROM

D FLASH

答案:B

解析:SDRAM 需要周期性刷新

ShoelessCai.com 值得您的关注!

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· winform 绘制太阳,地球,月球 运作规律

· AI与.NET技术实操系列(五):向量存储与相似性搜索在 .NET 中的实现

· 超详细:普通电脑也行Windows部署deepseek R1训练数据并当服务器共享给他人

· 【硬核科普】Trae如何「偷看」你的代码?零基础破解AI编程运行原理

· 上周热点回顾(3.3-3.9)