存储体介绍:包括片选,字扩展,位扩展

1.片选信号

结合之前考试的经验,这里搞懂几个知识点。

位扩展:一个芯片连接一个数据位

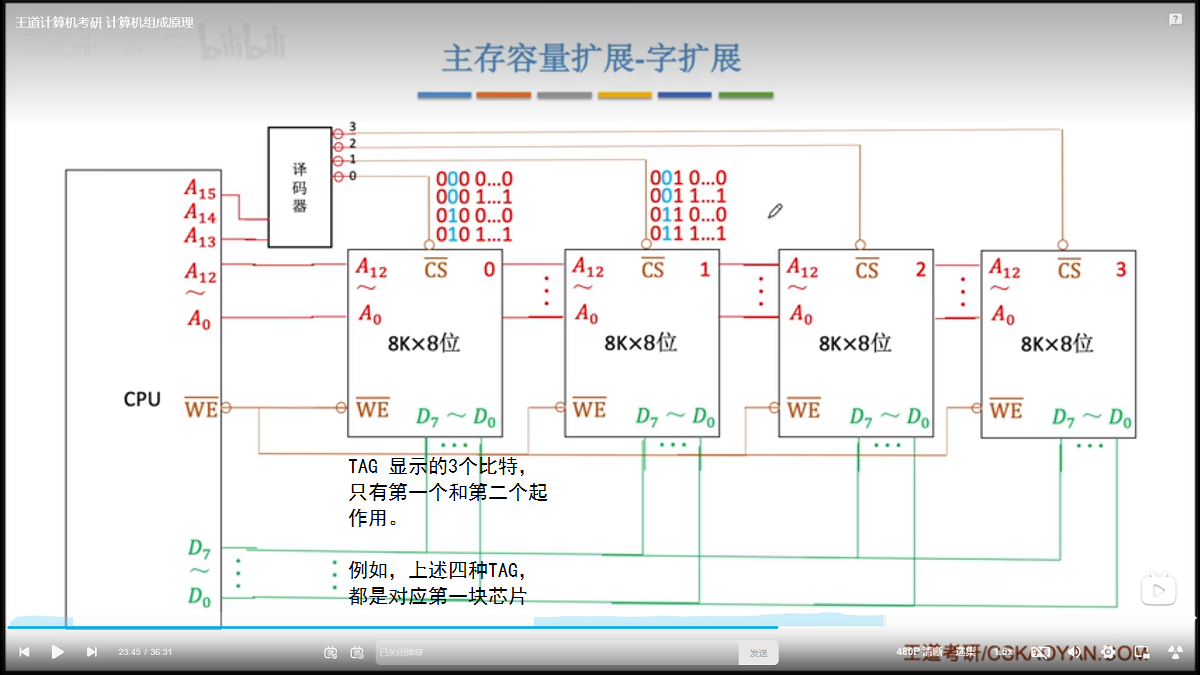

字扩展:一个芯片连接一个地址位。这里的地址位可以冗余,例如,74138 的 2/4 位译码器,接入 A 13, A15,此时地址位表示是 3 个比特,中间比特不起作用,仍然表示 4 块芯片,但是地址有冗余。

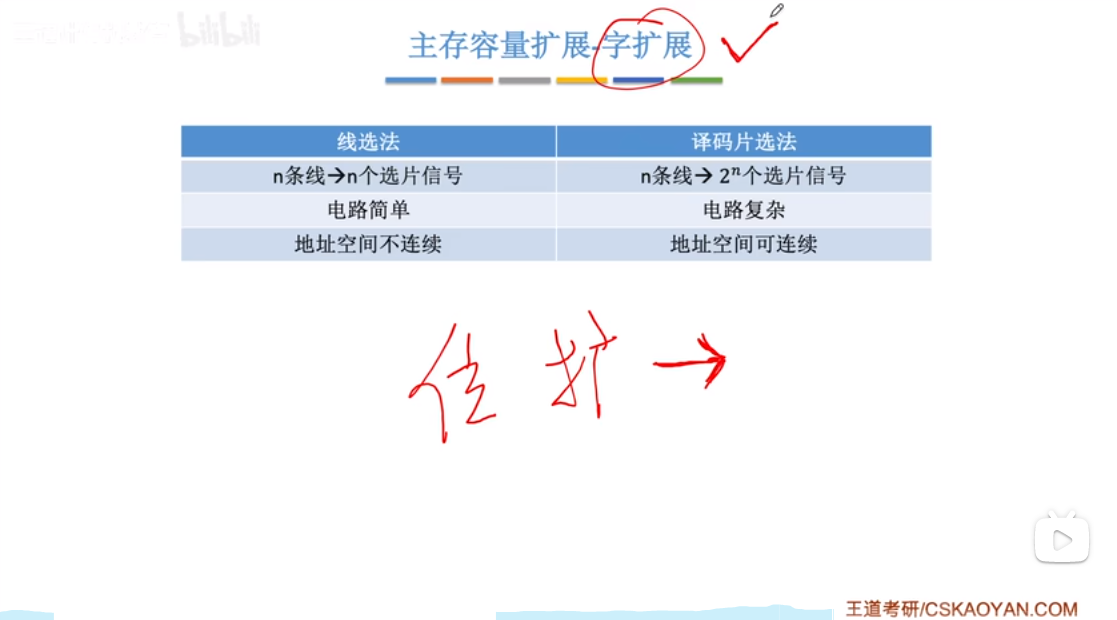

以下这张 PPT 大概了解一下,线选,即一根线连一个芯片(犹如 MDR,数据线用法);译码片选,即一根线表示 2^n 个地址,地址线都是在指数上的。

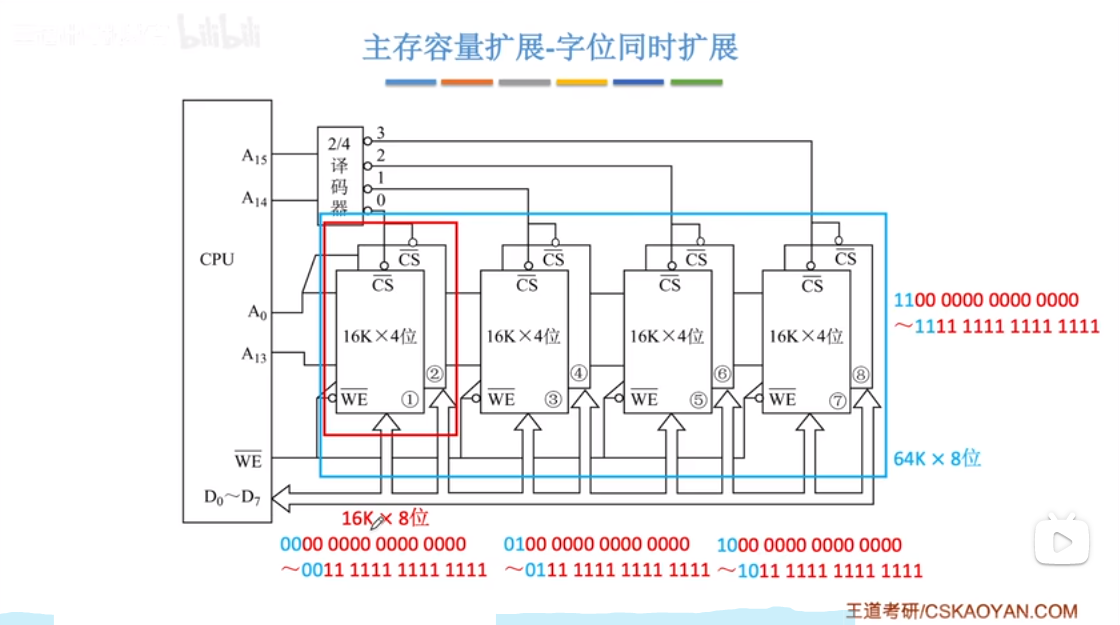

以下 PP T是位字同时扩展。一是位扩展,将数据位撑满,即 8 个比特。二是字扩展,即一个地址线,一个芯片,译码器可以 enlarge 。

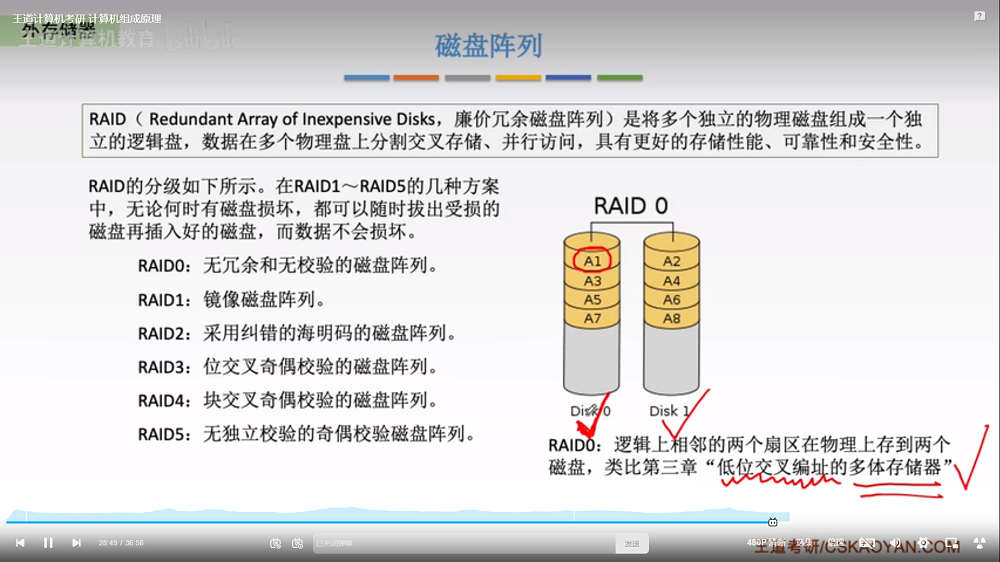

磁盘阵列

1.RAID0 -- 条带,提升存取速度

2.RAID1 -- 直接复制一份数据;容量减少一半,意味着所有数据存两份;

3.RAID2 -- 海明校验,可恢复数据,即哪一块磁盘数据被擦除,用海明校验方式恢复。

固态硬盘 SSD

1.固态硬盘非磁盘,是用若干个 RAM组成。一块 RAM 内部,分成若干块,一个块内,分成若干页。

2.写入前,擦除一整块,因此通常都会写入前将块内容复制到其他物理块;

3.写操作,以页为单位,读取操作以块为单位。写一次,读无限次。

4.随机访问性能高,速度高于机械硬盘。

磨损均衡技术

1.存入数据的时候,电影“读多写少”,这种使用性质,使得系统判断这项数据应该写在老块上,新块承担写操作。

2.称为,磨损均衡技术。

Cache 概念

1.Cache 是主存复制在 CPU 内部的一块内容,物理形态在 CPU 内部,内容和主存部分内容完全一致。SRAM 实现。

2.CPU 运行速度和主存是不匹配的

3.基本原理。空间局部性:现在用的内容,其物理周围,未来很可能被使用。时间局部性,现在用的,未来很可能被使用。

Cache 命中率

1.未来试图访问的信息,在 Cache 中占据的比例;

2.缺失率 M = 1 - H

平均访问时间 t

1.先访问 Cache 再访问 主存

平均访问时间 t = 命中率 * 访问 Cache 时间 + (1 - 命中率)* (访问 Cache 时间 + 访问主存的时间)

2.Cache 和 主存 一起访问

平均访问时间 t = 命中率 * 访问 Cache 时间 + (1 - 命中率) * 访问主存时间

Cache 写策略

* 写策略的含义,即 Cache 换入换出时候,如何操作?

1. 写命中 -- 写回法

* 能够 HIT Cache,不立即写入

* 换出时才写回主存

* 脏位 = 1

* 数据可能不一致(非同时)

2.写命中 -- 全写法

* 同时写入 Cache 和 主存 (全的含义)

* 速度慢,数据一致

* 有 Write Buffer 提升速度

* Buffer 可能塞满,进程可能阻塞

3.写不命中 -- 写分配法

* Cache 命中 且 修改

* 写分配法 + 写回法

4.写不命中 -- 非写分配法

* 只写主存,不调入 Cache

* 非写分配法 + 全写法

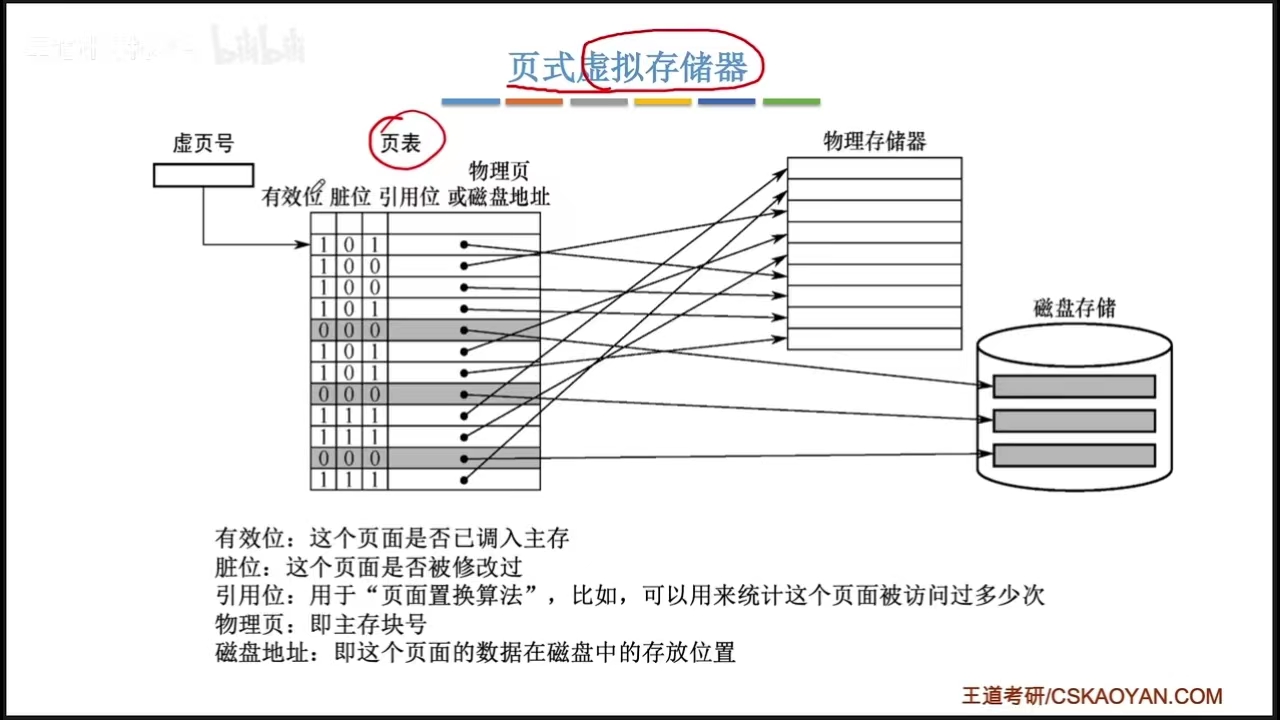

虚拟存储器(主要在OS)

1.在计算机显示的程序,分成好几个 Page 存储在磁盘,如果要运行的时候,调入主存。

一个页面,与磁盘的“块”对应。

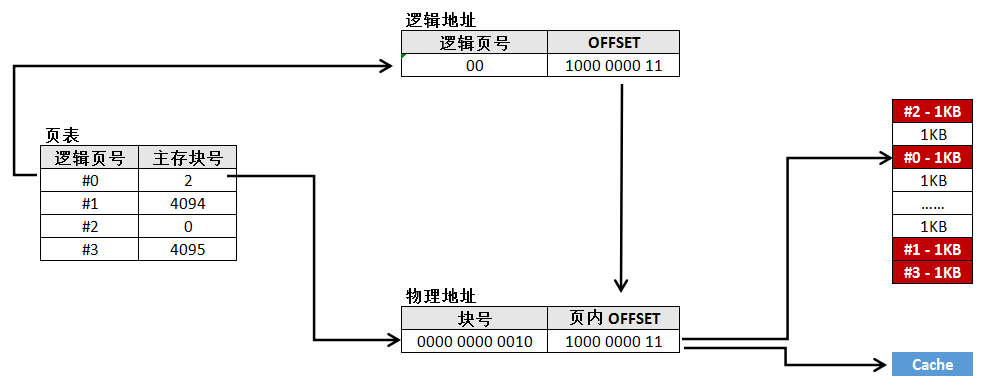

2.地址映射

虚拟地址:逻辑地址

实际地址:物理地址

3.页表

和 Cache 机制一样,页表存着关于 主存地址 和 外存地址 对应着的内容。类似于字典,或者查表。

页表属于某种数据结构,我的理解是,在系统软件中,页表以一种特殊的数据结构发挥作用。

CPU 在这个过程做什么工作?

简言之,查页表,访主存。

分享一下本人的笔记

虚拟存储机制

* 主要是主存和外存交互

* 有效位 = 1,则去主存中找;有效位 = 0,去外存中找。

欢迎关注 ShoelessCai.com ,值得您的关注!