自己动手写CPU——寄存器堆、数据存储器(基于FPGA与Verilog)

上一篇写的是基本的设计方案,由于考研复习很忙,不知道下一次什么时候才能打开博客,今天就再写一篇。写一写CPU中涉及到RAM的部件,如寄存器堆、数据存储器等。

大家应该在大一刚接触到计算机的时候就知道ROM、RAM了吧。但也记不得那些繁杂的名称,只知道ROM是只读存储器,RAM是可读写存储器。其实知道这些也就够了。CPU内寄存器堆、数据存储器等部件都是可读出可写入的部件,所以全部属于RAM,其实在ISE中是可以直接进行调用IP核来完成这些操作的,但今天暂且不谈IP核,或许后期会对IP核模块进行详细的阐述。

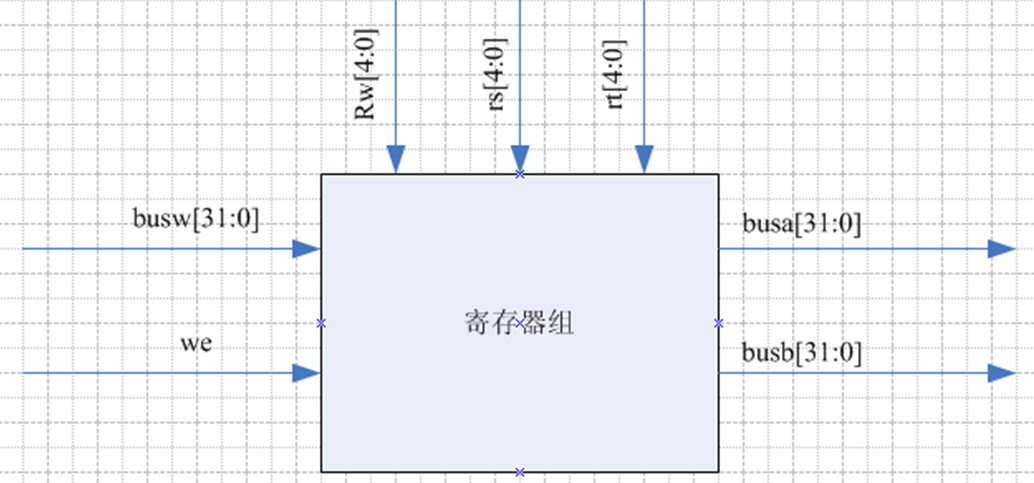

首先来说一说寄存器组,由于指令时MIPS指令,采用32位定长指令字,存数据的寄存器地址位宽都为5位,所以寄存器堆为32x32位的寄存器组。书上或者老师给的一些原理图都复杂的看不懂,其实只要理解透彻了寄存器堆是很简单的。如图为寄存器堆的输入输出结构图。

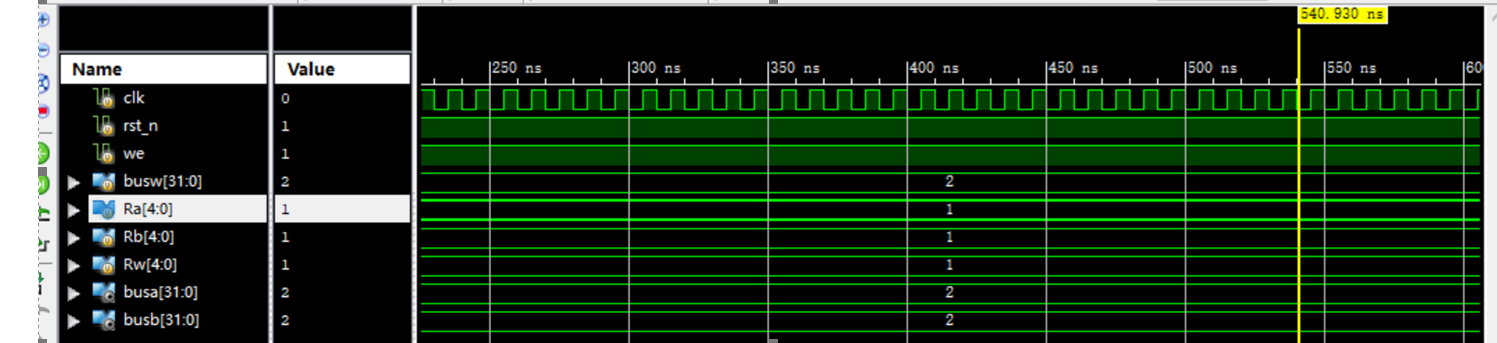

首先说写入,要将32位的数据写入32x32的寄存器堆中,那么必定有一个写使能信号(we),还得有一个写入数据寄存的地址(Rw)。当写入使能(we)为1时,表示我现在要向寄存器中写入数据了,那么立马通过Rw在寄存器组([31:0] Reg_Data [31:0]——32个32位寄存器)找到对应的32位寄存器,例如Rw = 5'd16,那么找到的就应该是32位寄存器组中32’d16的寄存器。找到要写入的寄存器后,将要写入的数据赋给寄存器即可。读出其实和写入是一样的,想要读出一段数据,就必须先找到存放数据的寄存器,那么依旧通过地址来寻找,当Ra = 5'd16时,那么找到的就是32位寄存器组中32’d16的寄存器,再将寄存器中的数据输出即可。仿真后波形如图。 寄存器堆如果理解了,那数据存储器就非常简单了,都是同样的道理,先通过地址找到对应的寄存器,然后将数据输进去或者将里边的数据输出来就可以,在此就不再赘述了。

寄存器堆如果理解了,那数据存储器就非常简单了,都是同样的道理,先通过地址找到对应的寄存器,然后将数据输进去或者将里边的数据输出来就可以,在此就不再赘述了。

以上就是关于寄存器堆和数据存储器的全部,时间有限,可能写的有些粗糙,代码这些东西,还是重在理解,理解透彻了,写出来加上仿真真的是分分钟的事。

今天就......emmmmm到次结束。