千兆以太网芯片88E1111 RGMII模式的驱动

88E1111可工作在10Mb/s,100Mb/s,1000Mb/s下,由于DE2-115开发板在设计的时候只采用了4位数据端口,因此只能采用MII模式(100Mb/s),或者RGMII模式(1000Mb/s),看了官方的DATASHEET后,几乎得到什么,于是就想到了一个办法,就是将官方所给的关于RGMII的例程下到开发板上,然后将88E1111的配置寄存器里面的数据用NIOS II读出来,这样就获得了正确的配置数据,然后就将配置数据用NIOS II配置给芯片,然后就遇到了很奇怪的事情:当我把配置的那几行代码都注释掉以后居然88E1111还可以继续正常运行,后来发现,只要给芯片的硬复位引脚Reset_n一个较长的复位即可,大概10~20ms就可以了。具体如何将芯片通过CONFIG引脚配置成RGMII模式,可以参考DE2-115的原理图。

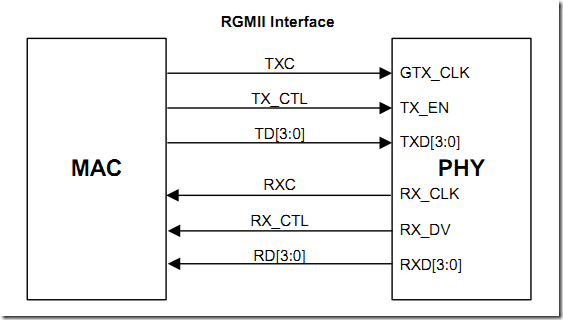

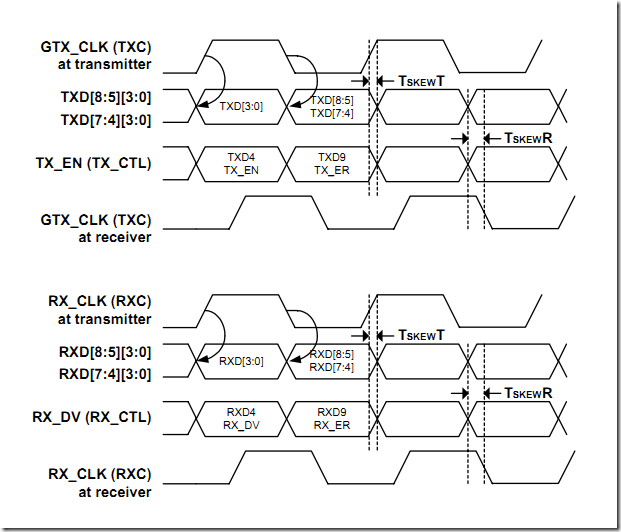

下面就谈谈如何利用时钟的上升和下降沿收发数据。以下两个图是连接图和时序图。

先谈输出端Tx:

Tx端有三个信号,Txd_RGM,Tx_ctrl,Tx_clk,其中Tx_clk是由FPGA提供的125MHz的时钟,Tx_RGM是发送的数据,Tx_ctrl在Tx_clk时钟上升沿发送的是Tx_en,在下降沿发送的是Tx_en和Tx_er的异或值。

Rx端也有三个信号:Rxd_RGM,Rx_ctrl,Rx_clk,其中Rx_clk是由88E1111提供的125MHz的时钟,Rx_RGM表示接收到的数据,Rx_ctrl在Rx_clk的上升沿收到的是Rx_en,在下降沿收到的是Rx_en和Rx_er的异或值。

由于一个always模块中不能同时使用时钟的上升和下降沿,可以调用DDIO模块,当然,也可以不用,下图就是不采用DDIO的一个示意图,这个是用来设计DDR SDRAM的,可以借鉴

1 module rgmii_io( 2 input Tx_clk, 3 input Rx_clk, 4 output Tx_clk_RGM, 5 6 input[7:0] Txd, 7 output [3:0] Txd_RGM, 8 input Tx_en, 9 input Tx_er, 10 output Tx_ctrl, 11 12 input[3:0] Rxd_RGM, 13 output reg[7:0] Rxd, 14 input Rx_ctrl, 15 output reg Rx_dv, 16 output reg Rx_er 17 ); 18 assign Tx_clk_RGM = ~Tx_clk; 19 //****************************************************************************** 20 //Tx control 21 //****************************************************************************** 22 wire Tx_err; 23 reg[3:0] Txd_low,Txd_high; 24 reg Tx_en_d1,Tx_err_d1; 25 assign Tx_err=Tx_en^Tx_er; 26 assign Txd_RGM = Tx_clk ? Txd_low : Txd_high; 27 assign Tx_ctrl = Tx_clk ? Tx_en_d1 : Tx_err_d1; 28 29 always@(posedge Tx_clk) 30 begin 31 Txd_low <= Txd[3:0]; 32 Txd_high <= Txd[7:4]; 33 Tx_en_d1 <= Tx_en; 34 Tx_err_d1 <= Tx_err; 35 end 36 //****************************************************************************** 37 //Rx control 38 //****************************************************************************** 39 wire Rx_er_d1; 40 reg[3:0] Rxd_low,Rxd_high; 41 reg Rx_dv_d1,Rx_err_d1,Rx_dv_d2,Rx_er_d2; 42 reg[7:0] Rxd_d1; 43 assign Rx_er_d1=Rx_dv_d1^Rx_err_d1; 44 wire Rx_clk_n; 45 assign Rx_clk_n=~Rx_clk; 46 47 always@(posedge Rx_clk_n) 48 begin 49 Rxd_low<=Rxd_RGM; 50 Rx_dv_d1<=Rx_ctrl; 51 end 52 53 always@(posedge Rx_clk) 54 begin 55 Rxd_high<=Rxd_RGM; 56 Rx_err_d1<=Rx_ctrl; 57 end 58 59 always@(posedge Rx_clk_n) 60 begin 61 Rxd_d1<={Rxd_high,Rxd_low}; 62 Rx_dv_d2<=Rx_dv_d1; 63 Rx_er_d2<=Rx_er_d1; 64 end 65 66 always@(posedge Rx_clk) 67 begin 68 Rxd<=Rxd_d1; 69 Rx_dv<=Rx_dv_d2; 70 Rx_er<=Rx_er_d2; 71 end 72 endmodule