子模块到顶层模块——例化与调用

在Verilog程序中,不可能将所有的代码放在一个文件里面,不同功能的模块封装在一个文件里面,但最终我们要生成最终的系统电路,必须将这些子模块生成一个顶层模块,那么如何生成这样的顶层模块呢?

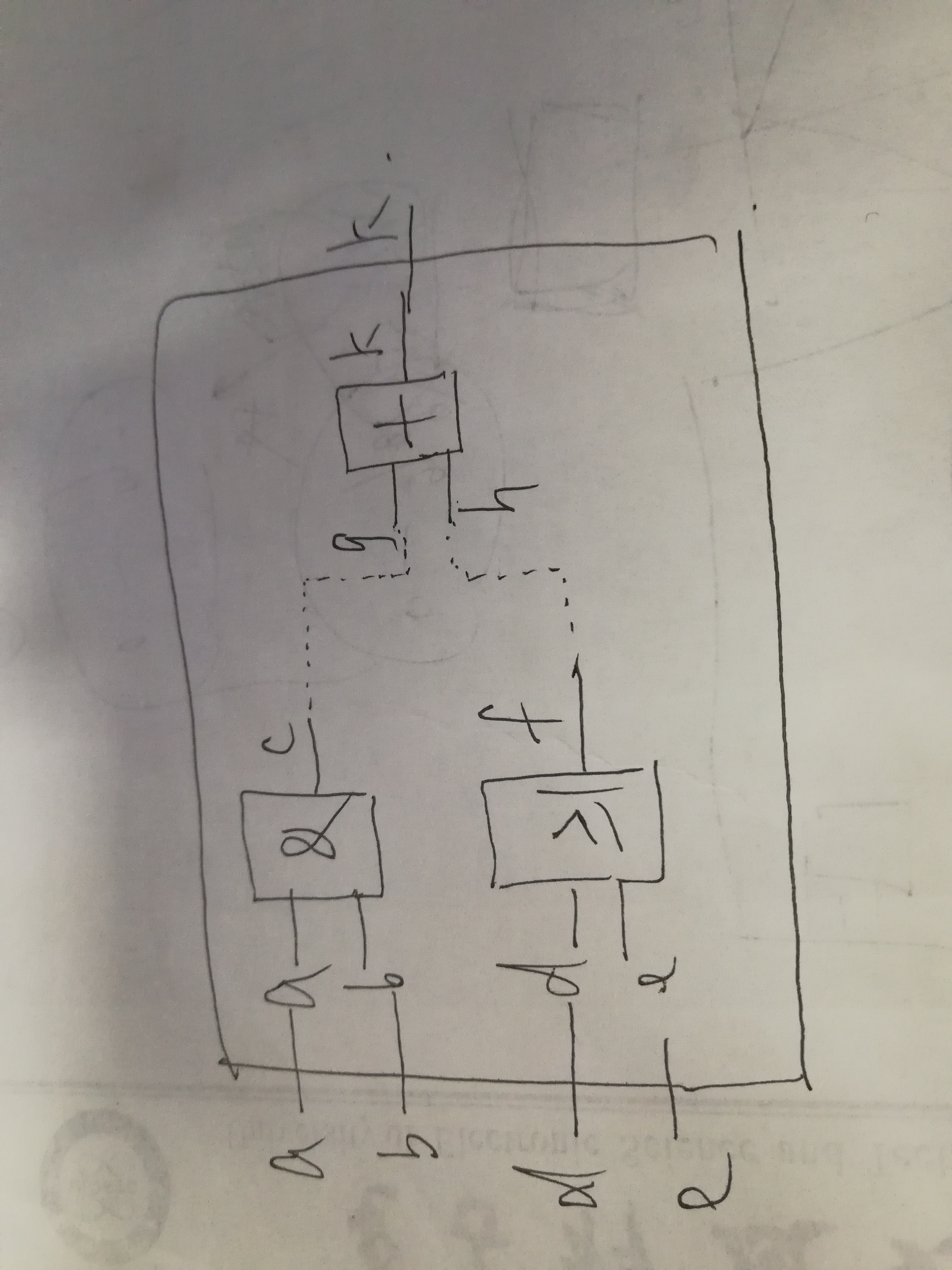

给出一个实例,

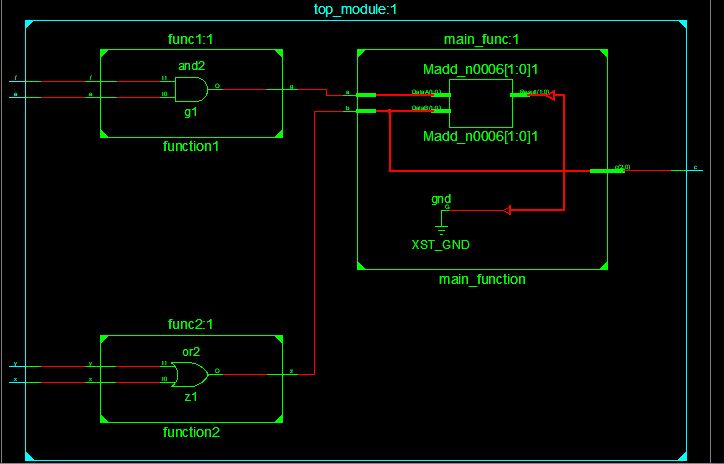

上图中提出了这样一个问题:如何将三个子模块接成一个顶层模块。这三个子模块分别完成了:与,或,加 三种运算,现在需要做的是将三个子模块综合成一个顶层模块,在此我们需要将我们设计的子模块例化成被调用的子模块。关于例化,讨论两个问题:

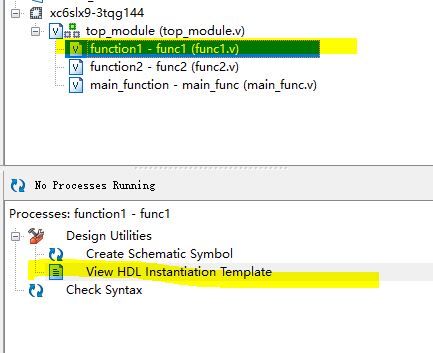

1.不要手打,要用ISE环境中自己例化的结果:

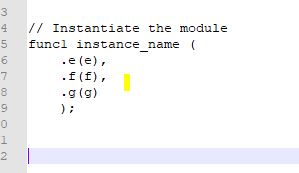

点击该文件,在下面的窗口中出现view HDL instantiation Template!!双击,即可生成对应的模板,如图:

这样生成的例化模板,首先在格式上不会出错,其次,比较简单,不用手动输入端口,要注意变量前面有小数点!!!!

2.如何将分离的模块产生联系??

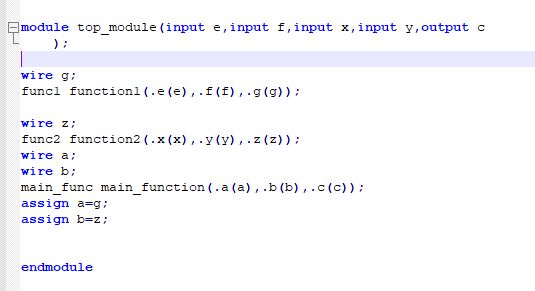

上述三个模块是分离的,将其组合成一个模块的时候,注意到,模块1与模块 ,模块2或模块,都与模块3有联系。具体的联系是:将与模块和或模块的输出接到了相加模块的输入

那么如何表示这种逻辑关系呢?

在这里是组合逻辑电路,上述的逻辑联系本质上是一种线连接,因此采用定义相应的变量为wire,并采用assign的赋值方式,即可完成赋值,如下图:

得到得到综合电路结果如下图:

图示完成了完整的顶层模块构架。再次总结以下3个观点:

1 各个子模块的设计可以相互独立

2 例化子模块的时候,不要手打,采用“view HDL instantiaion Template”!例化更为方便。

3 线端子进行连接的时候,定义wire ,采用assign赋值的方式即可完成!!!

view HDL instantiation Template

stay foolish,stay hungry

浙公网安备 33010602011771号

浙公网安备 33010602011771号