intel VT-X (VMX) spec 解读

所有IA的介绍,参考: Intel® 64 and IA-32 Architectures Software Developer Manuals 内容非常多。

虚拟化相关的主要是看 卷3,23-33章, pdf 如下:

网上大家的分析,基本也是来自于这个文档。

CHAPTER 23 INTRODUCTION TO VIRTUAL MACHINE EXTENSIONS

23.1 OVERVIEW

VMX: virtual-machine extensions

VMX 指令见:《Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 2B》

VMX 其他方面和 system programming considerations 见《 Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 3B. 》

23.2 VIRTUAL MACHINE ARCHITECTURE

• Virtual-machine monitors (VMM)

• Guest software

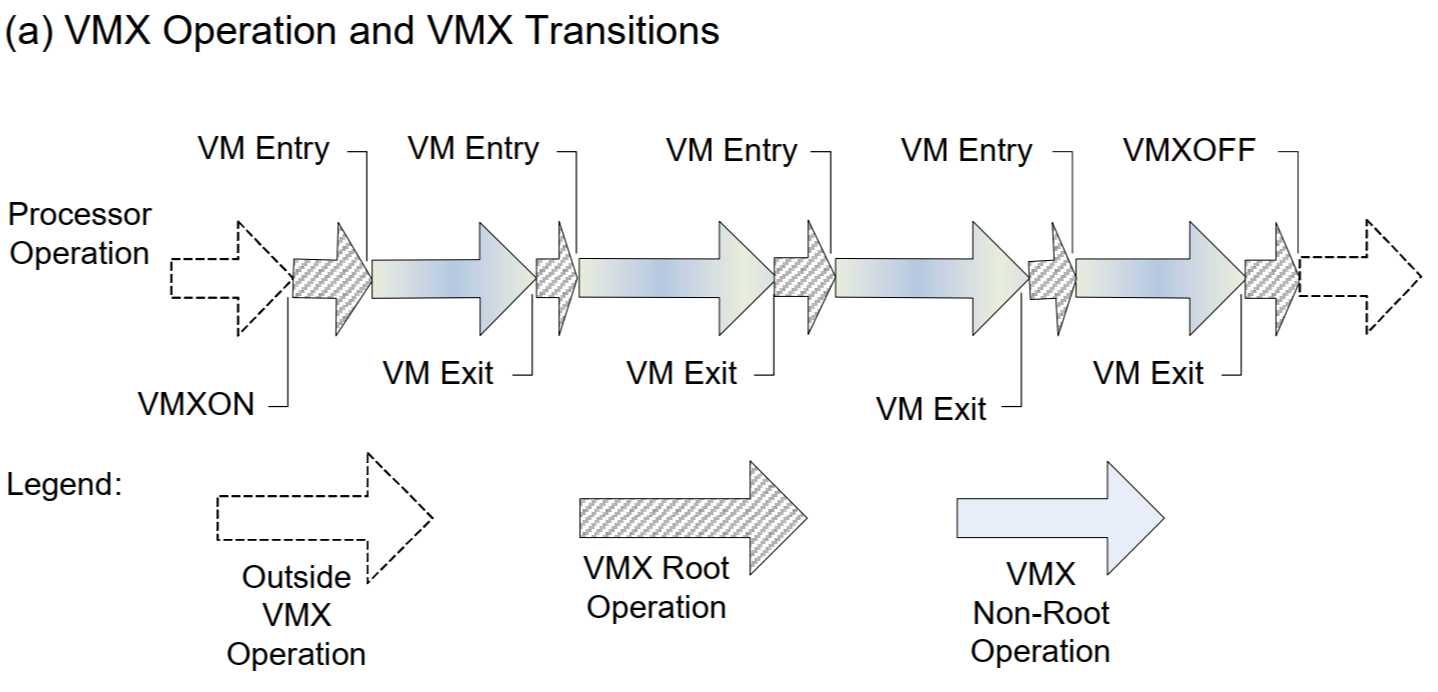

23.3 INTRODUCTION TO VMX OPERATION

- VMX root operation: VMM run in it

- VMX non-root operation: guest software run in it

- VM entries:Transitions into VMX non-root operation

- VM exits: Transitions from VMX non-root operation to VMX root operation ,一些特殊的VMCALL 指令或者事件,导致VM退出到VMM中。

23.4 LIFE CYCLE OF VMM SOFTWARE

VMLAUNCH 和 VMRESUME 指令 for VM Exit/VM Entry

VMXON 和 VMXOFF 指令for VMX启动和结束

23.5 VIRTUAL-MACHINE CONTROL STRUCTURE

VMX非根操作和VMX转换由虚拟机控制结构(VMCS)的数据结构控制。

VMCS 指令来访问VMCS , 读写由VMPTRST 和VMPTRLD两个指令决定,配置通过VMREAD, VMWRITE, 和 VMCLEAR 来操作。

每个虚机的vCPU都是不同的VMCS。

23.6 DISCOVERING SUPPORT FOR VMX

通过CPUID 查看是否支持VMX,CPUID.1:ECX.VMX[bit 5] = 1 , 第三章, “Instruction Set Reference, A-L” of Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 2A.

VMX其他的特性,通过VMX capability MSRs 查看。参考 Appendix A, “VMX Capability Reporting Facility”

23.7 ENABLING AND ENTERING VMX OPERATION

23.8 RESTRICTIONS ON VMX OPERATION

24.1 OVERVIEW

VMCS 指针必须4K边界对齐。

逻辑处理当前VMCS 是激活的VMCS之一。

24.2 FORMAT OF THE VMCS REGION

24.3 ORGANIZATION OF VMCS DATA

24.4 GUEST-STATE AREA

24.4.1 Guest Register State

24.4.2 Guest Non-Register State

24.5 HOST-STATE AREA

24.6 VM-EXECUTION CONTROL FIELDS

VM执行控制字段控制VMX非根操作.

24.6.1 Pin-Based VM-Execution Controls

控制异步事件的处理

24.6.2 Processor-Based VM-Execution Controls

控制同步事件的处理,这些事件主要是由特定指令的执行引起的。

24.6.3 Exception Bitmap

异常位图是一个32位字段,其中每个异常对应一位。 发生异常时,其向量会选择该字段中的一个位。 如果该位为1,则异常导致VM退出。 如果该位为0,通过IDT传递异常, 该异常使用对应的异常向量描述符。

页错误(矢量14的异常)是否导致VM退出, 由异常位图中的第14位 以及由缺页错误产生的错误码和VMCS中的两个32位字段(页错误- 错误码掩码和页错误错误码匹配)。 有关详细信息,请参见第25.2节。

24.6.4 I/O-Bitmap Addresses

VM执行控制字段包括两个64位物理地址的I / O位图A和B(每一个的大小为4 KB)。 I / O位图A的每一位表示一个端口,范围为0000H至7FFFH。 I / O位图B包含8000H至FFFFH范围内的端口的位。

当且仅当“使用I / O位图”控制为1时,逻辑处理器才使用这些位图。如果使用了位图,则如果它访问的端口对应的I / O位为1,则 / O指令的执行将导致VM退出。 有关详细信息,请参见第25.1.3节。 如果使用位图,则其地址必须4 KB对齐。

24.6.5 Time-Stamp Counter Offset and Multiplier

24.6.6 Guest/Host Masks and Read Shadows for CR0 and CR4

24.6.7 CR3-Target Controls

24.6.8 Controls for APIC Virtualization

24.6.10 Executive-VMCS Pointer

24.6.9 MSR-Bitmap Address

24.6.11 Extended-Page-Table Pointer (EPTP)

扩展页表指针(EPTP)包含EPT PML4表的基地址(请参见第28.2.2节),以及其他EPT配置信息。

24.6.12 Virtual-Processor Identifier (VPID)

虚拟处理器标识符(VPID)是一个16位字段。 它仅在支持“启用VPID” VM执行控制(1-setting)的处理器上存在。 有关使用此字段的详细信息,请参见第28.1节。

24.6.13 Controls for PAUSE-Loop Exiting

在支持“退出PAUSE循环” VM执行控制(1-setting)的处理器上,VM执行控制字段包括以下32位字段:

24.6.14 VM-Function Controls

24.6.15 VMCS Shadowing Bitmap Addresses

24.6.16 ENCLS-Exiting Bitmap

24.6.17 ENCLV-Exiting Bitmap

24.6.18 Control Field for Page-Modification Logging

24.6.19 Controls for Virtualization Exceptions

24.6.20 XSS-Exiting Bitmap

24.6.21 Sub-Page-Permission-Table Pointer (SPPTP)

24.7 VM-EXIT CONTROL FIELDS

24.7.1 VM-Exit Controls

24.7.2 VM-Exit Controls for MSRs

24.8 VM-ENTRY CONTROL FIELDS

24.8.1 VM-Entry Controls

24.8.2 VM-Entry Controls for MSRs

24.8.3 VM-Entry Controls for Event Injection

24.8.3 VM-Entry Controls for Event Injection

24.9.1 Basic VM-Exit Information

24.9.2 Information for VM Exits Due to Vectored Events

24.9.3 Information for VM Exits That Occur During Event Delivery

24.9.4 Information for VM Exits Due to Instruction Execution

24.9.5 VM-Instruction Error Field

24.10 VMCS TYPES: ORDINARY AND SHADOW

24.11 SOFTWARE USE OF THE VMCS AND RELATED STRUCTURES

本节详细介绍了在使用VMCS和相关结构时软件应遵循的准则。 它还提供了不遵循准则的后果的描述。

24.11.1 Software Use of Virtual-Machine Control Structures

为确保处理器正常运行,使用活动的VMCS时,软件应遵守某些准则。 如果要将VMCS从一个逻辑处理器“迁移”到另一个逻辑处理器,则第一个逻辑处理器应在另一个逻辑处理器在对VMCS执行VMPTRLD(使VMCS在第二个逻辑处理器上处于活动状态)之前,对VMCS执行VMCLEAR(以使其在该逻辑处理器上处于非活动状态并确保所有VMCS数据都在内存中)。VMCS在多个逻辑处理器上处于活动状态,可能会被损坏(请参阅下文)。

软件不应修改 处于活动状态的VMCS的 VMCS区域中的 shadow-VMCS指示器(请参阅表24-1)。 这样做可能会导致VMCS损坏。 在修改shadow-VMCS指示器之前,软件应为VMCS执行VMCLEAR以确保其未激活。

软件应使用VMREAD和VMWRITE指令来访问当前VMCS中的不同字段(请参见24.11.2节)。 软件绝不应该使用普通的内存操作访问或修改活动VMCS的VMCS数据,部分原因是用于存储VMCS数据的格式是特定于实现的,而不是在体系结构上定义的,并且还因为逻辑处理器可能会维护 VMCS的一些VMCS数据, 该VMCS在处理器上而不是在VMCS区域中激活。

以下各项详细介绍了使用普通内存操作访问VMCS数据的一些危害:

•从具有常规内存读取的VMCS读取的任何数据均不能可靠地反映VMCS的状态。 结果可能会随时间或逻辑处理器的不同而有所不同。

•使用普通内存写操作写入VMCS不能保证对VMCS具有确定性的影响。 这样做可能会导致VMCS损坏(请参阅下文)。

(软件通过这些操作避免危害: 1. 在对VMCS区域的VMPTRLD执行之前删除该VMCS区域的任何线性地址映射,2. 执行该区域的VMCLEAR之后才重新映射它)

如果逻辑处理器退出VMX操作,则该逻辑处理器上活动的任何VMCS可能会损坏(请参阅下文)。

在VMX操作返回之后或在另一个逻辑处理器上使用VMCS 会导致VMCS损坏,为了防止 ,软件应在执行VMXOFF指令或对处理器断电(例如,作为到S3和S4电源状态转换的一部分)之前,对该VMCS执行VMCLEAR。

本部分确定了可能导致VMCS损坏的操作。这些操作可能会导致VMCS的数据变得不确定。如果该VMCS随后在任何逻辑处理器上使用,则行为可能无法预测。

以下各项详细介绍了VMCS损坏的一些危害:

•VM条目可能因为无法解释的原因而失败,也可能加载了不可期望处理器状态。

•处理器可能无法正确支持第25章中所述的VMX非root用户操作,并且可能会生成意外的VM退出。

•VM退出 可能会加载不可期望的处理器状态,将错误的状态保存到VMCS中,或导致逻辑处理器转换为关闭状态。

24.11.2 VMREAD, VMWRITE, and Encodings of VMCS Fields

24.11.3 Initializing a VMCS

在VM 进入使用VMCS之前,软件应使用VMWRITE初始化VMCS中的字段。

否则可能会导致无法预测的行为; 例如,VM进入可能由于无法解释的原因而失败,或者成功的转换(VM进入或VM退出)但可能会以加载了不可期望的处理器状态值。

不必初始化逻辑处理器将不使用的字段,(例如,如果“使用MSR位图”的 VM执行控制为0,则不必统一MSR位图地址。

处理器维护一些VMCS信息,这些信息无法使用VMWRITE指令修改; 其中包括VMCS的启动状态(请参见第24.1节)。 这样的信息可以被存储在VMCS区域的VMCS数据部分中。 由于此信息的格式是特定于实现的,因此在首次分配用作VMCS区域的内存区域时, 软件无法知道处理器怎么从内存区域的内容中确定此信息。

除了其他功能之外,VMCLEAR指令还可以初始化其操作数所引用的VMCS区域中任何特定于实现的信息。

为了避免 特定实现的行为的不确定性,软件应首先在VMCS区域上执行VMCLEAR,然后通过VMPTRLD首次激活对应的VMCS。 (图24-1说明了执行VMCLEAR如何使VMCS进入良好定义的状态。)

软件的使用符合这些限制:

•VM进入首次之前,应先对VMCS执行VMCLEAR。

•对VMCS执行了VMCLEAR之后,应该对使用VMCS的VM进入执行VMLAUNCH操作。

•VMRESUME应该用于 任何后续使用VMCS的VM进入(直到对VMCS的下一次执行VMCLEAR为止)。

通常,VMRESUME将比VMLAUNCH具有更低的延迟。

由于将VMCS从一个逻辑处理器“迁移”到另一个逻辑处理器需要使用VMCLEAR(请参见24.11.1),这会将VMCS的启动状态设置为“清除”,因此这种迁移需要使用VMLAUNCH来执行下一个VM进入。软件开发人员 应该通过避免将VMCS从一个逻辑处理器迁移到另一个逻辑处理器,而导致 VM进入 延迟增加带来的性能成本。

24.11.4 Software Access to Related Structures

除了VMCS区域本身中的数据之外,VMX非根操作还可以由VMCS中的指针引用的数据结构(例如I / O位图)控制。 虽然指向这些数据结构的指针是VMCS的一部分,但数据结构本身不是。 使用VMREAD和VMWRITE不能访问它们,但是可以通过普通的内存写入来访问它们。

软件应确保 当前VMCS引用这些数据结构的 逻辑处理器处于VMX非根操作时,才对该数据结构做修改。否则可能导致无法预测的行为(包括24.11.1节中确定的行为)。

以下数据结构(在相关章节中有详细讨论)有例外:

EPT页表结构和用于定位SPP向量的数据结构(第28.3.3节);

virtual-APIC页面(第29.1节);

发布(post)的中断描述符(第29.6节);

虚拟化例外信息区域(第25.5.7.2节)

24.11.5 VMXON Region

在执行VMXON之前,软件会分配一个内存区域(称为VMXON区域),该内存区域供逻辑处理器用来支持VMX操作。 该区域的物理地址(VMXON指针)在VMXON的操作数中提供。 VMXON指针受 适用于VMCS指针同样的 限制:

•VMXON指针必须4 KB对齐(位11:0必须为零)。

•VMXON指针不得设置任何位超出处理器物理地址宽度

在执行VMXON之前,软件应将VMCS修订标识符(请参见第24.2节)写入VMXON区域。 (特别是,它应将31位VMCS修订标识符写入VMXON区域的前4个字节的30:0比特;位31应清除为0。)

不需要以任何其他方式初始化VMXON区域。 软件应为每个逻辑处理器使用一个单独的区域,并且不应在该逻辑处理器上执行VMXON和VMXOFF之间 访问或修改逻辑处理器的VMXON区域。

否则可能导致无法预测的行为(包括24.11.1节中确定的行为)。

CHAPTER 28 VMX SUPPORT FOR ADDRESS TRANSLATION

28.1 VIRTUAL PROCESSOR IDENTIFIERS (VPIDS)

CHAPTER 31 VIRTUAL-MACHINE MONITOR PROGRAMMING CONSIDERATIONS

31.4 USING VMX INSTRUCTIONS

其他参考:

Hardware Assisted Virtualization Intel Virtualization Technology 这个总结的比较好,可以看看。

PROCESSOR

浙公网安备 33010602011771号

浙公网安备 33010602011771号