Bus Blaster v4 design overview

Bus Blaster v4 design overview

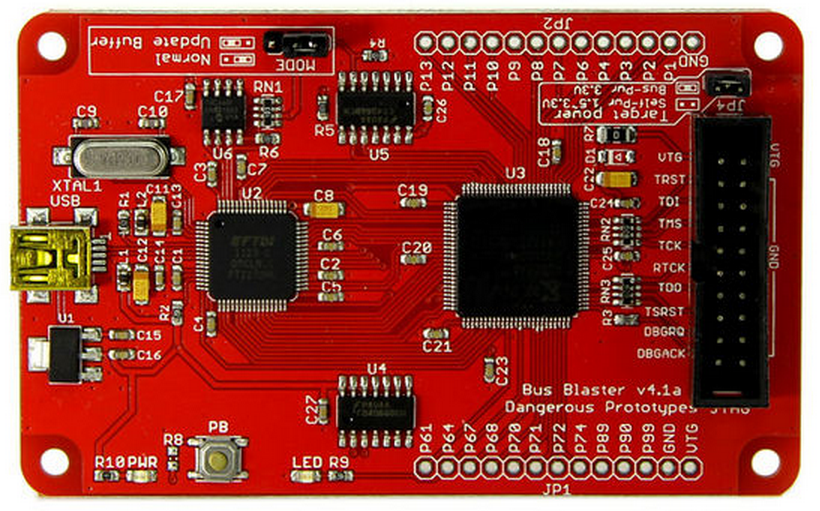

Bus Blaster v4 is an experimental, high-speed JTAG debugger for ARM processors, FPGAs, CPLDs, flash, and more. Thanks to a reprogrammable buffer, a simple USB update makes Bus Blaster v4 compatible with many different JTAG debugger types in the most popular open source software.

- Based on FT2232H with high-speed USB 2.0

- Buffered interface works with 3.3volt to 1.5volt targets

- Reprogrammable buffer is compatible with multiple debugger types

- Compatible with 'jtagkey', 'KT-link' programmer settings in OpenOCD, urJTAG, and more

- Should support Serial Wire Debug when available

- Mini-CPLD development board: self programmable, extra CPLD pins to header

- Open source (CC-BY-SA)

Bus Blaster v4 is a redesign of v3/v2 that supports SWV, an obscure extension to a reduced pincount JTAG protocol most people will never use. Unless you need it, stick with v3 and save a few bucks!

- Can now support the SWV feature of Cortex microcontroller for advance debugging when software support is available

- SWV is little used and not currently supported in software, most users will be better off with Bus Blaster v4 available here

- Fitted in a DP9056 (90x56 mm) standard PCB

- Added series resistors to input and output pins to protect against damage and noise

Bus Blaster v4 is available now for $45. Each unit is tested with a real JTAG target before it ships.

Buffer logic

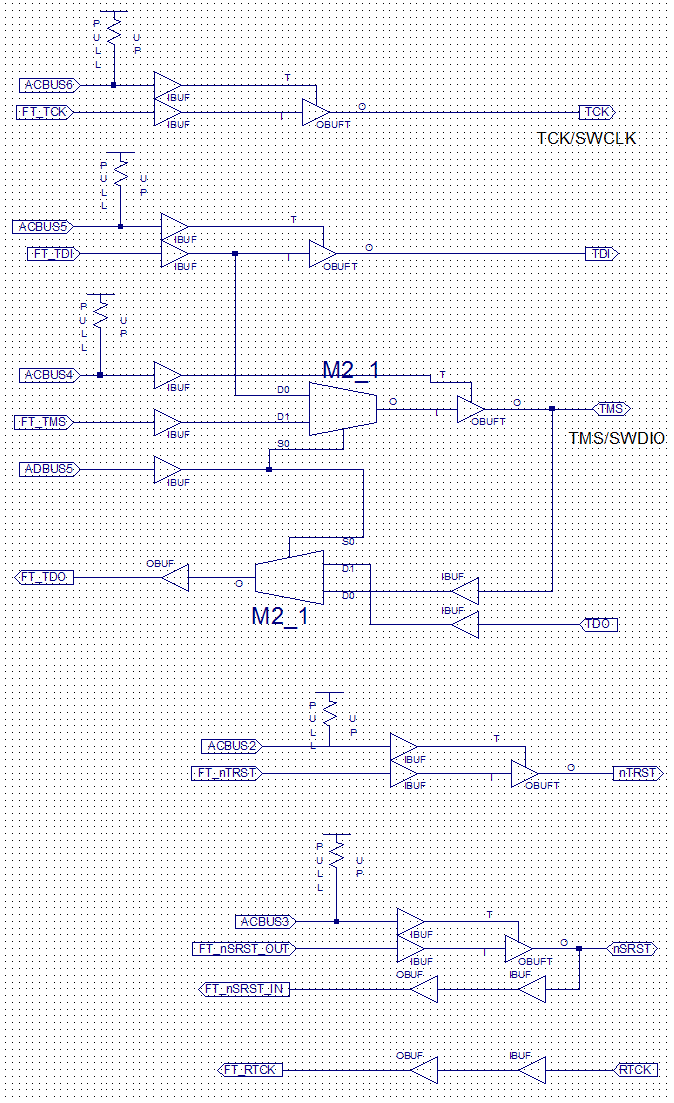

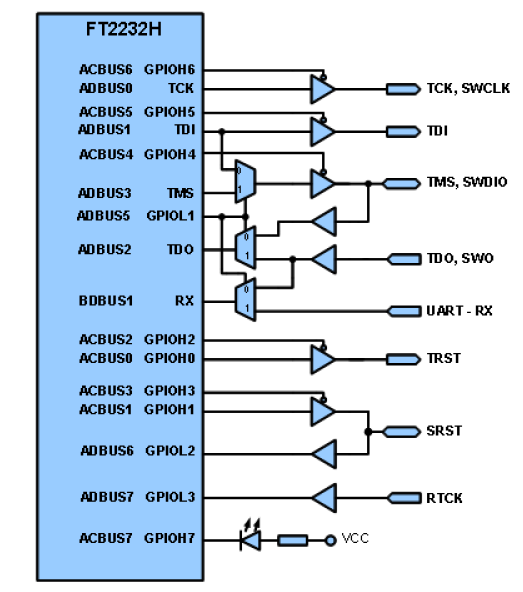

New buffer logic is designed using simple schematic entry, Verilog, or VHDL, and the free ISE Webpack software from Xilinx.

Here are two examples of buffer logic to give you an idea how flexible the design can be.

- See Bus Blaster buffer logic for the latest buffers and programming instructions

Buffer logic for Bus Blaster v4 and Bus Blaster v2/v3 ARE NOT COMPATIBLE!

JTAGkey compatible

KT-link compatible

浙公网安备 33010602011771号

浙公网安备 33010602011771号