Bus Blaster

http://dangerousprototypes.com/docs/Bus_Blaster

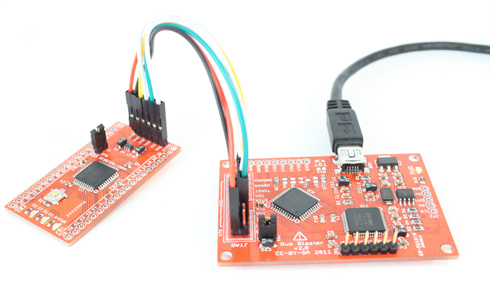

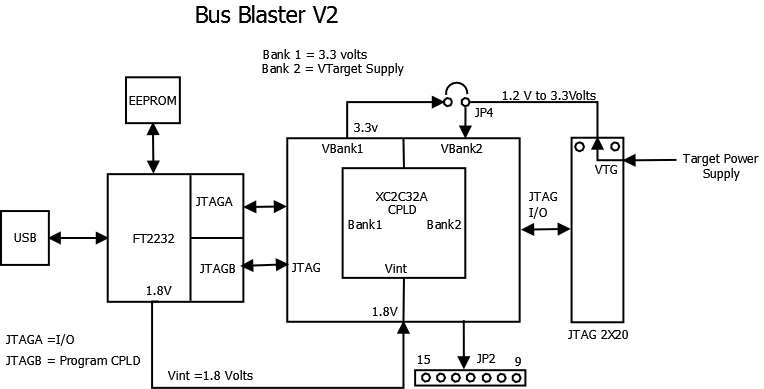

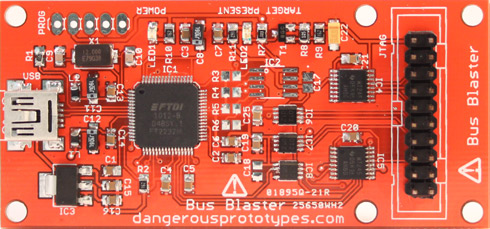

Bus Blaster v2 is an experimental, high-speed JTAG debugger for ARM processors,

FPGAs, CPLDs, flash, and more.

Thanks to a reprogrammable buffer, a simple USB update makes Bus Blaster v2 compatible

with many different JTAG debugger types in the most popular open source software.

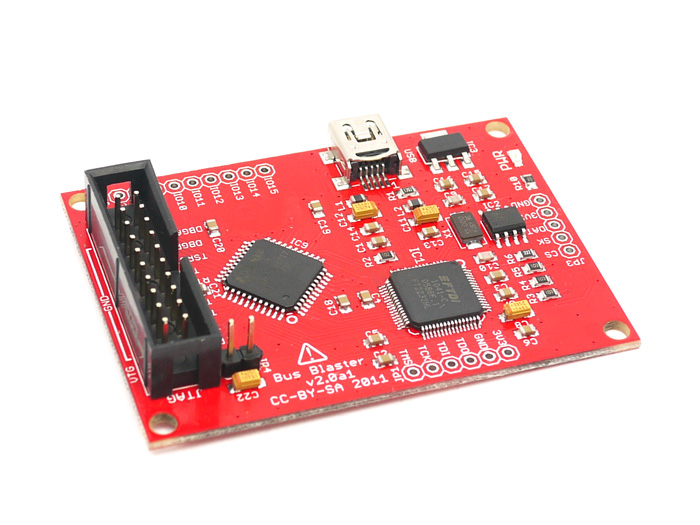

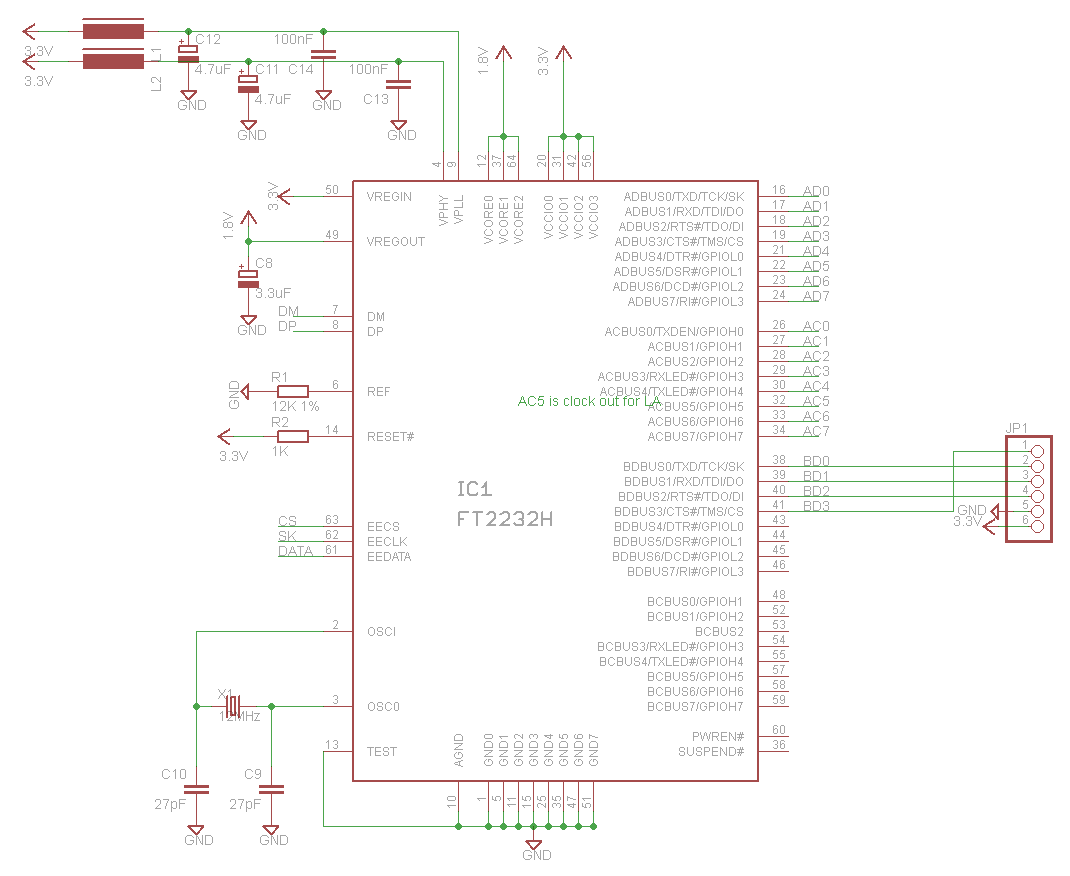

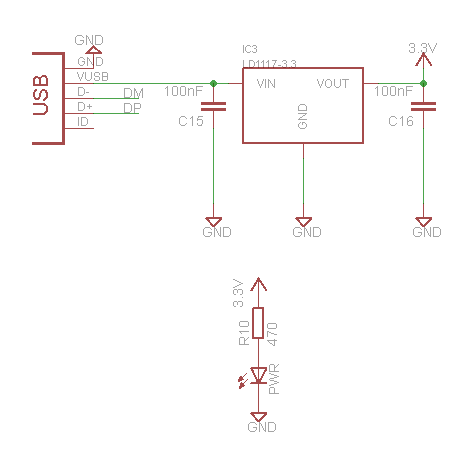

Based on FT2232H with high-speed USB 2.0

Buffered interface works with 3.3volt to 1.2volt targets

Reprogrammable buffer is compatible with multiple debugger types

Compatible with 'jtagkey', 'KT-link' programmer settings in OpenOCD, urJTAG, and more

Should support Serial Wire Debug when available

Mini-CPLD development board: self programmable, extra CPLD pins to header

Open source (CC-BY-SA)

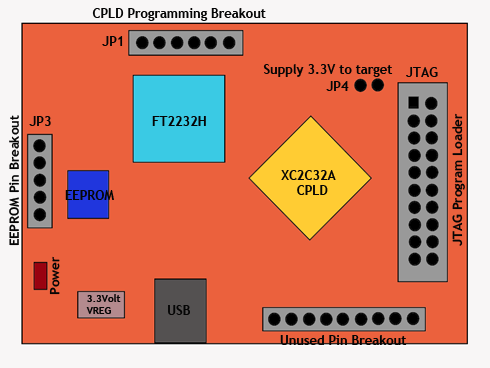

Bus Blaster buffer logic

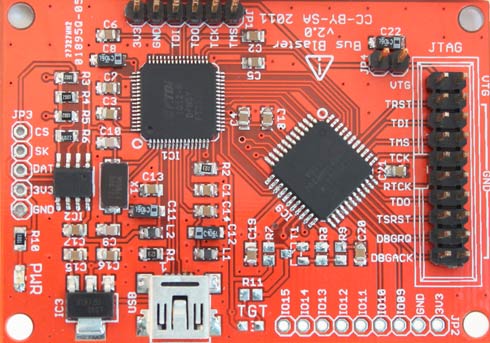

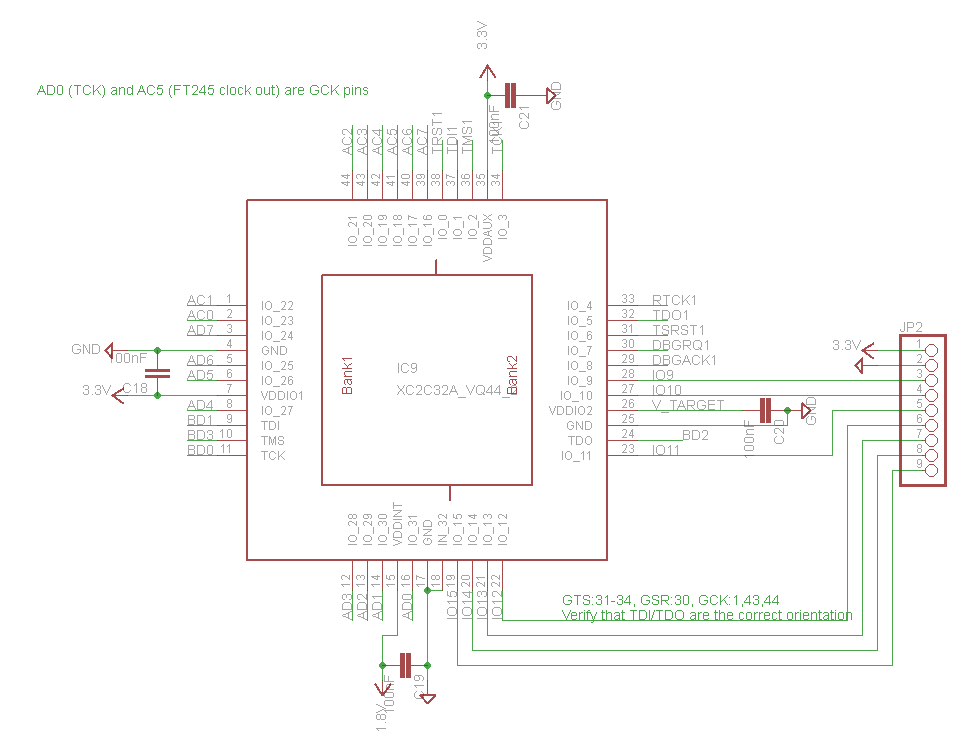

Bus Blaster v2 is buffered by a reprogrammable CPLD instead of discrete logic chips.

New buffer logic can be loaded so the Bus Blaster appears like many common JTAG programmer types.

These are the currently available buffer clones.

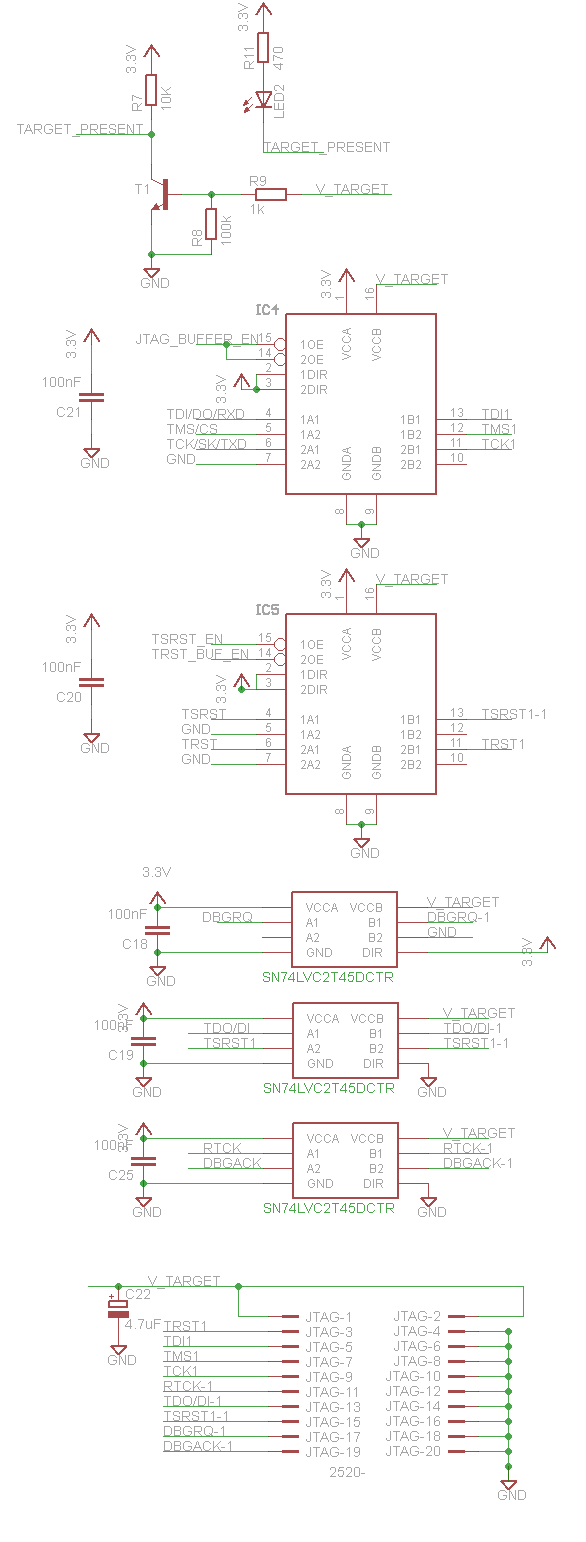

jtagkey

The JTAGkey is probably the most commonly cloned buffer configuration among FT2232-based JTAG programmers.

It is compatible with OpenOCD, urJTAG, and more.

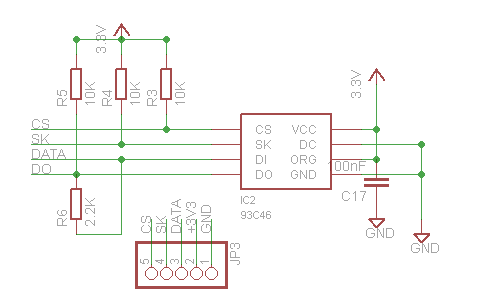

Schematic

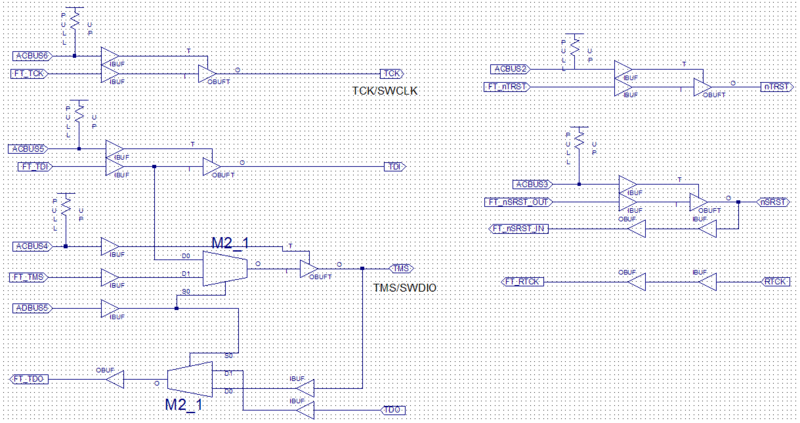

KT-link

The KT-link is the first FT2232 JTAG debugger with support for new SWD and SWV JTAG protocols.

The libswd project is adding support for SWD to OpenOCD and urJTAG, and the KT-link will be the first supported programmer.

Bus Blaster v2 supports SWD only!

Bus Blaster v2 does not support SWV because one required pin is used to program the CPLD

Schematic

Bus Blaster v1

The buffer is NOT 5volt compatible

浙公网安备 33010602011771号

浙公网安备 33010602011771号