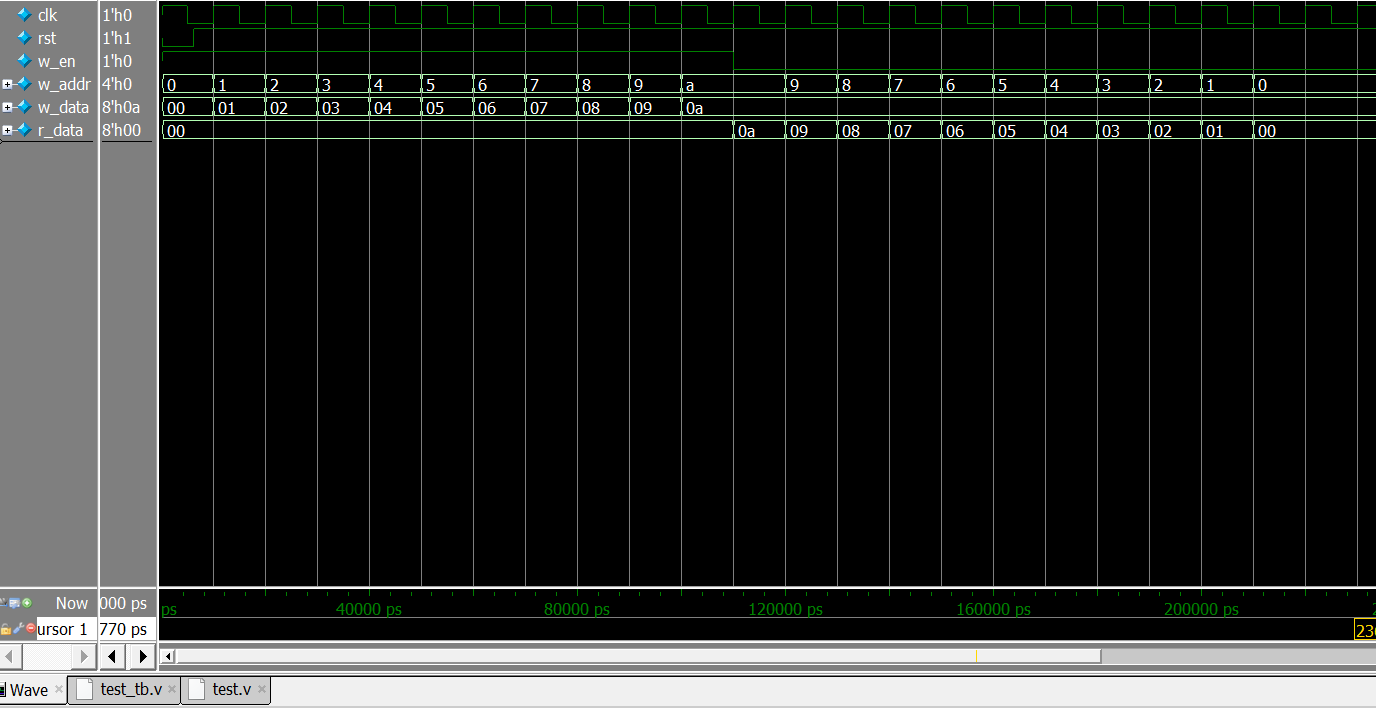

//单端口RAM--读写总线,读写数据总线,8bit*16//通过进行地址编码表示RAM深度。可修改其地址位宽改变其深度。

module test (

input clk,

input rst,

input w_en,//w_en=1时,为写操作。w_en=0时,为读操作。

input [3:0]w_addr,

input [7:0]w_data,

output wire [7:0]r_data

);

reg [7:0]mem[15:0];

integer i;

always @(posedge clk or negedge rst) begin

if(!rst) begin

for (i=0; i<15 ; i=i+1) begin

mem[i] <= 'b0;

end

end

else if (w_en) begin

mem[w_addr] <= w_data;

end

end

assign r_data = (!w_en)?mem[w_addr]:'b0;

/*

always @(posedge clk) begin

if(!rst) begin

r_data <= 'b0;

end

else if (!w_en) begin

r_data <= mem[w_addr];

end

end

*/

endmodule

`timescale 1ns/10ps

module test_tb;

reg clk;

reg rst;

reg w_en;

reg [3:0]w_addr;

reg [7:0]w_data;

wire [7:0]r_data;

test u1(

.clk(clk),

.rst(rst),

.w_en(w_en),

.w_addr(w_addr),

.w_data(w_data),

.r_data(r_data)

);

initial begin

w_addr = 'b0;

w_data = 'b0;

clk = 1'b1;

rst = 1'b0;

w_en = 1'b1;

#6;

rst = 1'b1;

end

always #5 clk = ~clk;

initial begin

w_en = 1'b1;

#110;

w_en = 1'b0;

#120;

end

initial begin

#10;

repeat(10) begin

w_addr = w_addr + 1'b1;

#10;

end

#10;

repeat(10) begin

w_addr = w_addr - 1'b1;

#10;

end

end

initial begin

#10;

repeat(10) begin

w_data = w_data + 1'b1;

#10;

end

end

endmodule

![]()

浙公网安备 33010602011771号

浙公网安备 33010602011771号