verilog设计一个可预置初值的7进制循环计数器

实现预置计数器,当为7进制时,直接修改数据位宽为3bit即可。

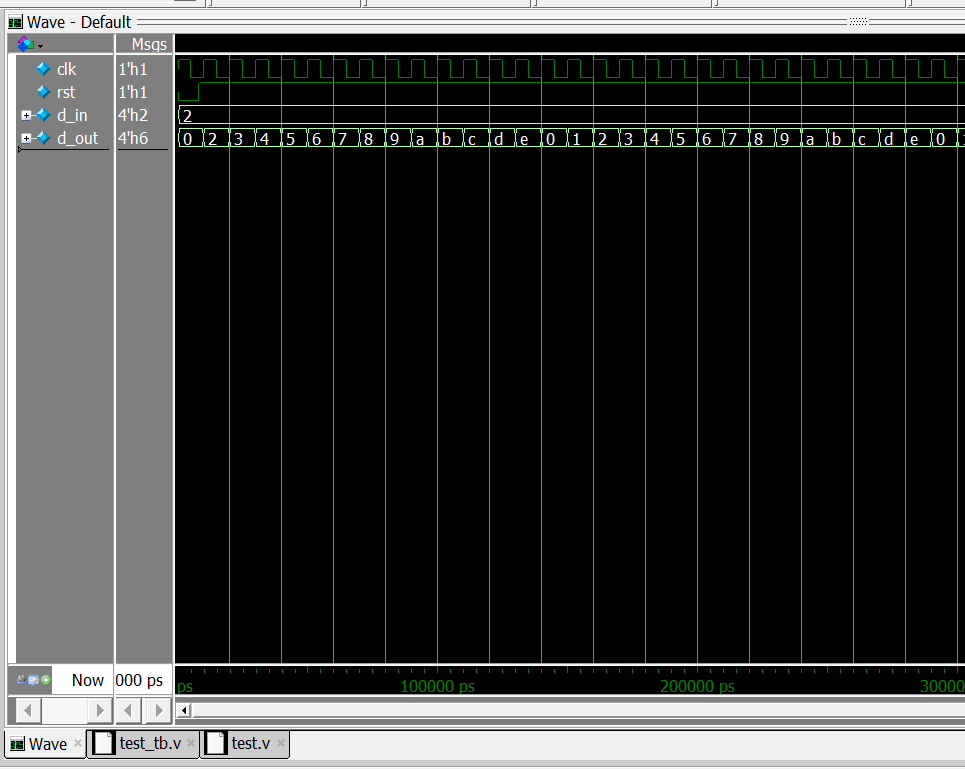

//实现可预置初值的15进制循环计数器 module test ( input clk, input rst, input [3:0]d_in, output reg [3:0]d_out ); reg [3:0]cnt; always @(posedge clk or negedge rst) begin if(!rst) begin cnt <= d_in; end else if (cnt == 'b1110) begin cnt <= 'b0; end else begin cnt <= cnt + 1'b1; end end always @(posedge clk or negedge rst) begin if(!rst) begin d_out <= 'b0; end else begin d_out <= cnt; end end endmodule

`timescale 1ns/10ps module test_tb; reg clk; reg rst; reg [3:0]d_in; wire [3:0]d_out; test u1( .clk(clk), .rst(rst), .d_in(d_in), .d_out(d_out) ); initial begin clk = 1'b1; rst = 1'b0; #8; rst = 1'b1; end always #5 clk = ~clk; initial begin d_in = 4'b0010; #10; end endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号