奇数分频--不使用负边沿触发verilog实现(占空比50%)

奇数分频电路的代码,有两种情况:①使用带负沿触发的DFF(要求占空比50%),②不使用带负沿触发的DFF;

使用带负边沿触发的:https://www.cnblogs.com/shadow-fish/p/13383903.html

不适用带负边沿触发:实质是向带负边沿触发的DFF靠拢。实验程序为3分频,占空比为50%。

module test ( input clk, input rst, output wire d_out ); reg [1:0]cnt; reg d_out_1; reg d_out_2; reg d_out_3; wire clk_1; always @(posedge clk or negedge rst) begin if(!rst) begin cnt <= 2'b0; end else if (cnt == 2'b10) begin cnt <= 2'b0; end else begin cnt <= cnt + 1'b1; end end always @(posedge clk or negedge rst) begin//占空比1/3 if(!rst) begin d_out_1 <= 'b0; end else if (cnt < 2'b10) begin d_out_1 <= 1'b0; end else begin d_out_1 <= 1'b1; end end assign clk_1 = ~clk; always @(posedge clk_1 or negedge rst) begin//占空比1/3, if(!rst) begin d_out_2 <= 'b0; d_out_3 <= 'b0; end else if (cnt < 2'b10) begin d_out_2 <= 'b0; d_out_3 <= d_out_2; end else begin d_out_2 <= 'b1; d_out_3 <= d_out_2; end end assign d_out = d_out_1 | d_out_3;//也可以使用相与,则占空比要求为2/3。 endmodule

测试文件:

`timescale 1ns/10ps module test_tb; reg clk; reg rst; wire d_out; test u1( .clk(clk), .rst(rst), .d_out(d_out) ); initial begin clk = 1'b1; rst = 1'b0; #8; rst = 1'b1; end always #5 clk = ~clk; endmodule

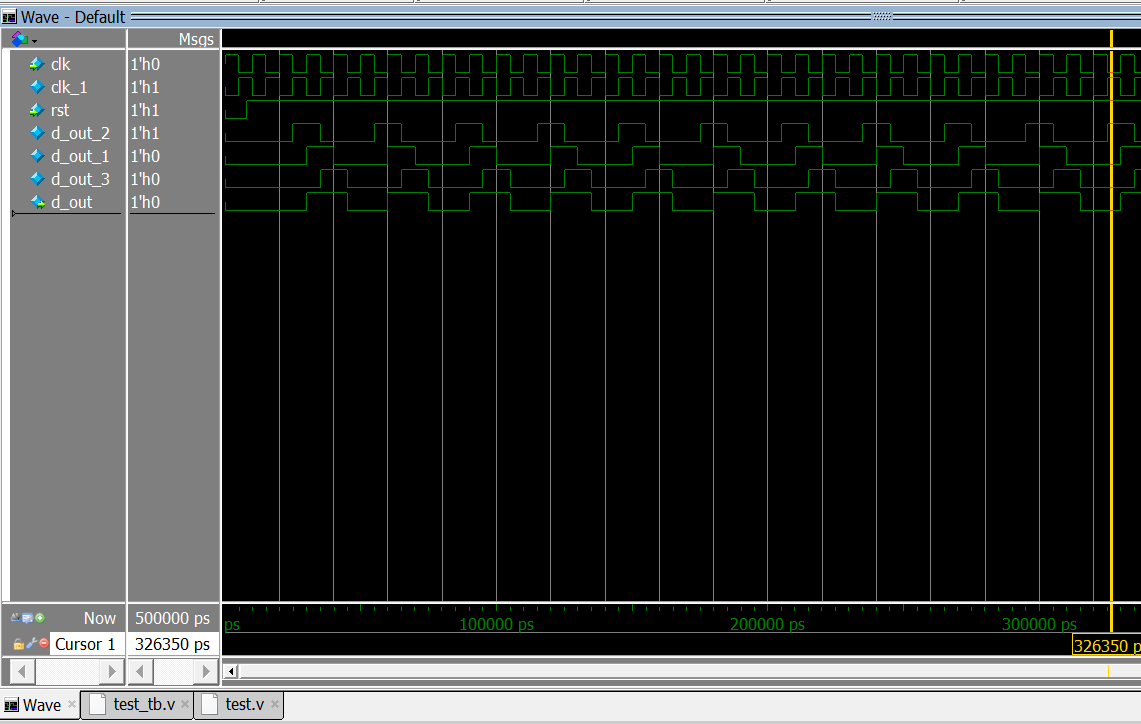

仿真结果:

浙公网安备 33010602011771号

浙公网安备 33010602011771号