异步电路中,快时钟域到慢时钟域的信号同步--脉宽拓展

前文分析请看:https://www.cnblogs.com/shadow-fish/p/13451214.html

单bit信号下的快时钟到慢时钟域的信号同步

module test ( input clka,//快时钟域100MHZ input clkb,//慢时钟域50MHZ input rst, input d_in, output wire d_out ); reg d_out_1; reg d_out_2; reg d_in_1; reg d_in_2; wire d_in_3; always @(posedge clka or negedge rst) begin//将原来的时序扩展一倍 if(!rst) begin d_in_1 <= 'b0; d_in_2 <= 'b0; //d_in_3 <= 'b0; end else begin d_in_1 <= d_in; d_in_2 <= d_in_1; //d_in_3 <= d_in_1 | d_in_2; end end

assign d_in_3 <= d_in_1 | d_in_2; always @(posedge clkb or negedge rst) begin if (!rst) begin d_out_1 <= 1'b0; d_out_2 <= 1'b0; end else begin d_out_1 <= d_in_3; d_out_2 <= d_out_1; end end assign d_out = d_out_2; endmodule

测试代码:

`timescale 1ns/10ps module test_tb; reg clka; reg clkb; reg d_in; reg rst; wire d_out; test u1( .clka(clka), .clkb(clkb), .rst(rst), .d_in(d_in), .d_out(d_out) ); initial begin clka = 1'b1; clkb = 1'b0; rst = 1'b0; #6; rst = 1'b1; end always #5 clka = ~clka; always #10 clkb = ~clkb; initial begin repeat(5) begin #10; d_in = 1'b0; #10 d_in = 1'b0; #10 d_in = 1'b1; #10 d_in = 1'b0; #10 d_in = 1'b0; #20; end end endmodule

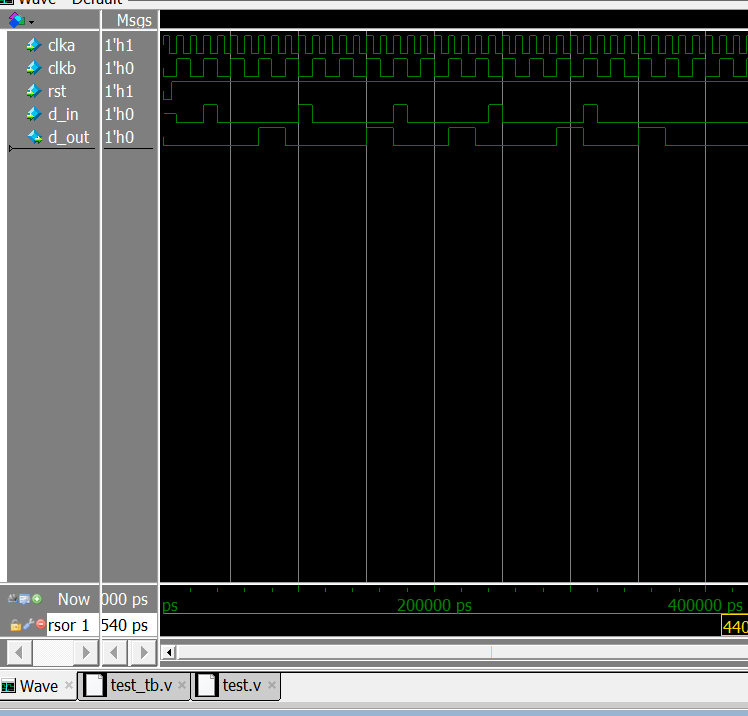

仿真结果:

浙公网安备 33010602011771号

浙公网安备 33010602011771号