建立时间(setup time)与保持时间(hold time)---相关内容

静态时序分析:通过穷举分析每一条路径的延时,用以确定最高工作频率,检查时序约束是否满足,分析时钟质量。

动态时序分析:通过给定输入信号,模拟设计在器件实际工作的功能和延时情况。

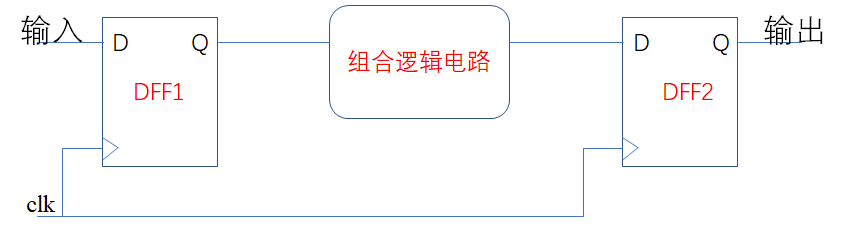

1.什么是建立时间、保持时间?

建立时间指在触发器的时钟采样沿到来之前,数据保持稳定不变的时间。

保持时间指在触发器的时钟采样沿到来之后,数据保持稳定不变的时间。

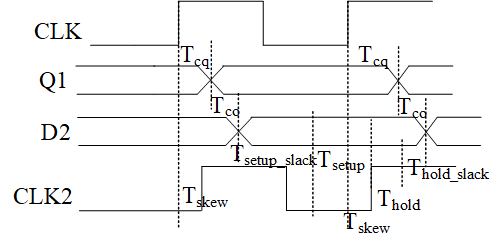

因为时钟偏斜,到达DFF2为CLK2

因为时钟偏斜,到达DFF2为CLK2

建立时间分析:取各组块最大延时计算

考虑时钟到达DFF2的时钟偏斜Tskew,则建立时间余量为Tset_slack=Tclk-Tcq-Tco-Tsetup+Tskew,使DFF2建立时间不违例,需保证Tset_slack>0。

其中Tcq为DFF1的时钟端到输出延迟,为器件固定属性;Tco是组合逻辑电路的延时,可以通过优化逻辑设计改变其值,使其满足建立保持时间不违例;Tsetup为触发器固有属性,定值。Thold为触发器固有属性,定值。

若不考虑DFF2的时钟偏斜,则建立时间裕量为Tset_slack=Tclk-Tcq-Tco-Tsetup。

保持时间分析:取各组块最小延时计算

考虑时钟到达DFF2的时钟偏斜Tskew,则保持时间余量:Tskew+Thold+Thold_slack=Tcq+Tco,因此可推出Thold_slack=Tcq+Tco-Tskew-Thold,使保持时间不违例,则需Thold_slack>0。若不考虑时钟偏斜,则Thold_slack=Tcq+Tco-Thold。

扩展:

时钟抖动:两个时钟周期之间存在的差值,这种误差发生在时钟发生器内部,和晶振和PLL内部有关,布线对其没有影响。主要表现在时钟频率上的不一定。

时钟偏斜:同样的时钟产生的多个子时钟信号之间的延时差异。主要表现在时钟相位上的不确定。

影响时钟偏斜的原因:布线长度及负载,时钟偏斜无法避免。

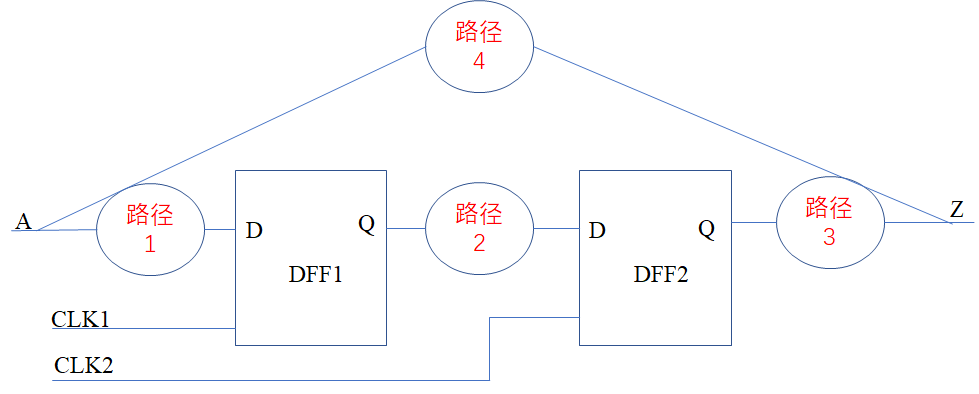

典型题:

(椭圆表示组合逻辑,DFF1,2表达触发器)

则有四条时序路径:

(1)从输入端到DFF1的D端,则需满足的时序要求是:Tclk1-Tin_delay-Tcom1-Tsetup>0(Tin_delay为输入延迟)

(2)从寄存器DFF1到寄存器DFF2,满足的时序要求是:Tclk-Tcq-Tcom2-Tsetup>0(clk1=clk2,且不考虑时钟偏斜)

(3)从寄存器DFF2到输出端口,满足的时序要求:Tclk-Tcq-Tcom3-Tsetup-Tto_delay>0(Tsetup为下一级寄存器的建立保持时间,Tto_delay为输出端延时)

(4)从输入端到输出端,满足的时序要求:Tclk-Tin_delay-Tcom4-Tto_delay-Tsetup>0(从输入到输出则前后各有寄存器接入)

浙公网安备 33010602011771号

浙公网安备 33010602011771号