边沿检测电路--上升沿、下降沿、双边沿

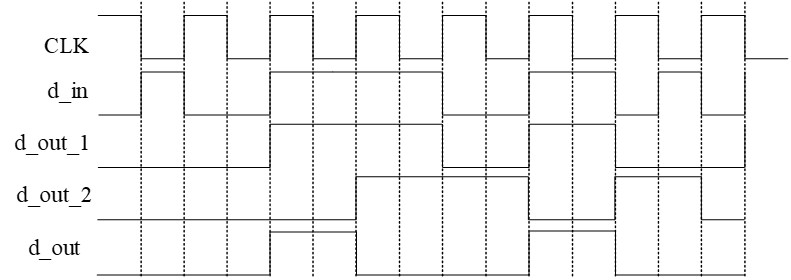

边沿检测--针对输入信号的跳变进而输出判断结果,上升沿、下降沿可以分别进行寄存器打拍,而后相与或者相或。当然针对与边沿检测,还有其他方法,例如通过移位寄存器,将输入信号打入移位寄存器中,然后对移位寄存器中的信号进行相与、相或和异或。这里进行打拍处理。

针对上升沿分析:--当时钟处于上升沿时,检测输入信号是否发生从0到1的跳变。正确理解其中的逻辑就很简单了。

上升沿检测:

module up_decetor(clk,rst,d_in,d_out);

input clk;

input rst;

input d_in;

output d_out;

reg d_out_1,d_out_2;

always@(posedge clk or negedge rst) begin

if(!rst) begin //通过寄存器保存前一个数据,使后一个数据与前一个数据进行比较

d_out_1 <= 1'b0;

d_out_2 <= 1'b0;

end

else begin

d_out_1 <= d_in;

d_out_2 <= d_out_1;

end

end

assign d_out = (~d_out_2)&d_out_1; //取反相与

endmodule

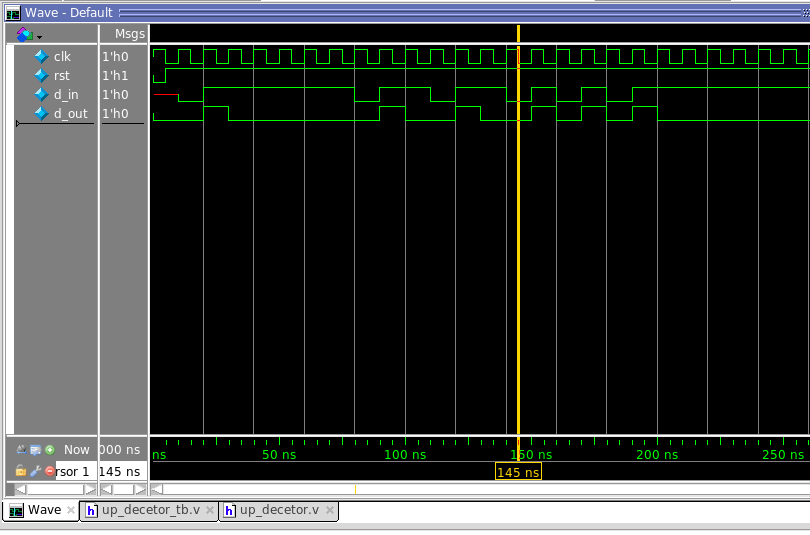

tb:

module up_decetor_tb;

reg clk;

reg rst;

reg d_in;

wire d_out;

up_decetor u1(

.clk(clk),

.rst(rst),

.d_in(d_in),

.d_out(d_out)

);

initial begin

clk=1'b1;

rst=1'b0;

#5;

rst=1'b1;

end

always #5 clk = ~clk;

/*initial begin

$vcdpluson;

end*/

initial begin

repeat(40) begin

#10;

d_in = {$random}%2;

end

end

endmodule

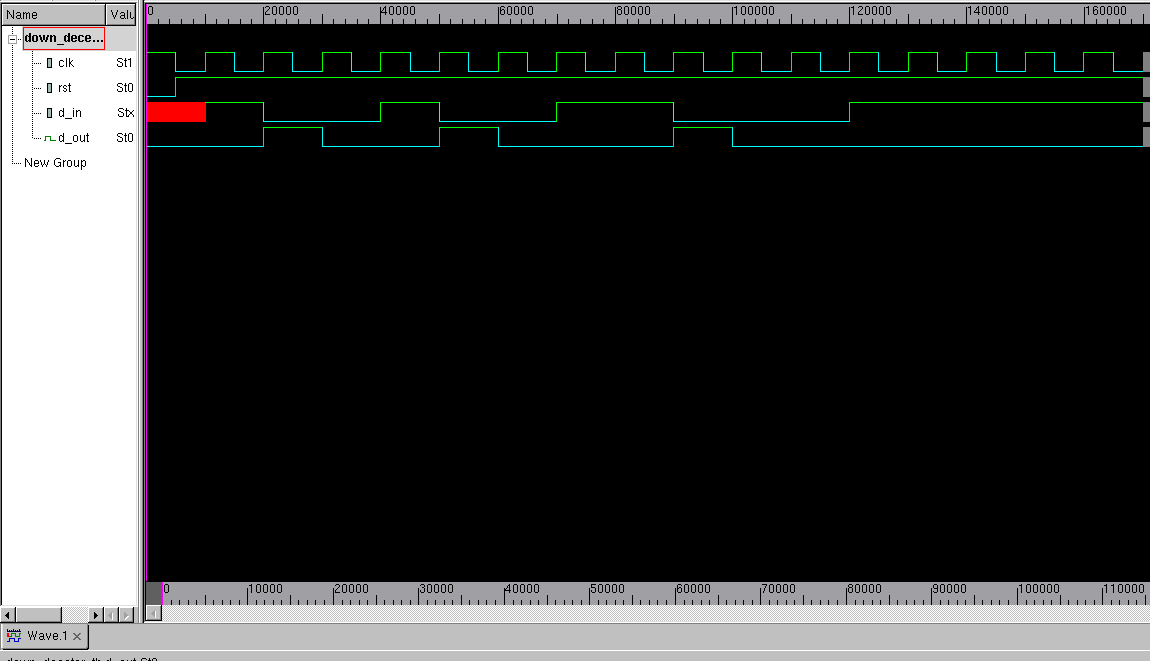

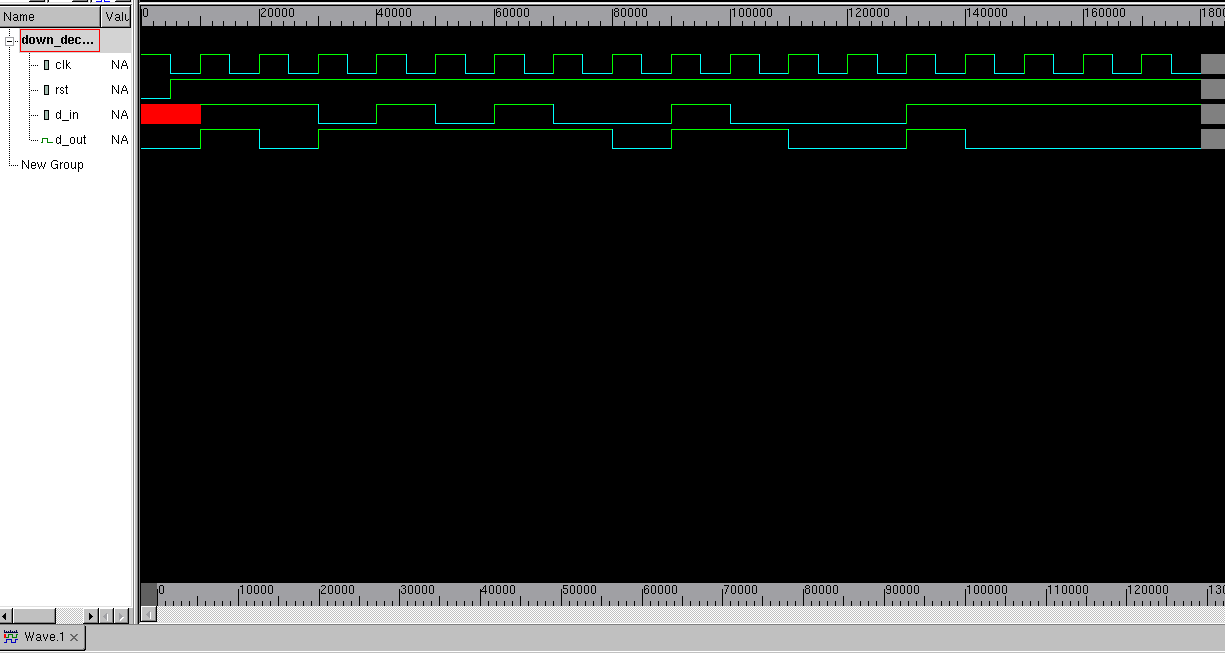

下降沿检测

module down_decetor(clk,rst,d_in,d_out);

input clk;

input rst;

input d_in;

output d_out;

reg d_out_1,d_out_2;

always@(posedge clk or negedge rst) begin

if(!rst) begin

d_out_1 <= 1'b0;

d_out_2 <= 1'b0;

end

else begin

d_out_1 <= d_in;

d_out_2 <= d_out_1;

end

end

assign d_out = (~d_out_1)&d_out_2; //

endmodule

tb:

双边沿检测:

浙公网安备 33010602011771号

浙公网安备 33010602011771号