ddr3调试经验分享(一)——modelsim实现对vivado中的MIG ddr3的仿真

Vivado中的MIG已经集成了modelsim仿真环境,是不是所有IP 都有这个福利呢,不知道哦,没空去验证。

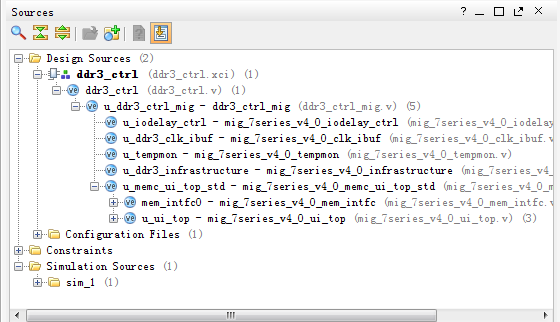

第一步:使用vivado中的MIG IP生成一堆东西 ,这个过程自己百度。或者是ug586有step by step 的,so easy。 生成之后是这样子的

第二步:在modelsim中增加xilinx库

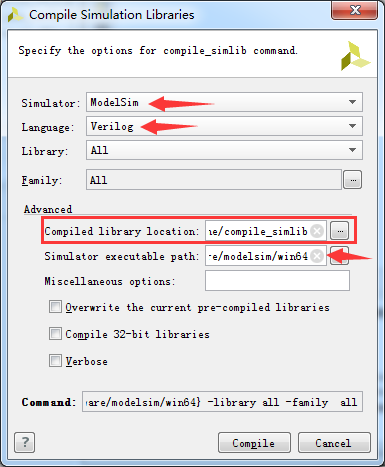

编译库 tool--> compile simulation libraries

选择modelsim,我只会verilog所以只选择了这个。 comiled library location 选择一个地方保存下来。simula executable path 自动找到了modelsim的地方 ,因为我是64bit系统,所以就win64. 点击compile。

增加库:在你选择的那个文件夹下有一个modelsim.ini文件,选择

这一段要放到modelsim安装文件夹下的modelsim.ini文件下(它默认只是可读文件哦)。不要放的太后面了。

第三步: 改变工作目录

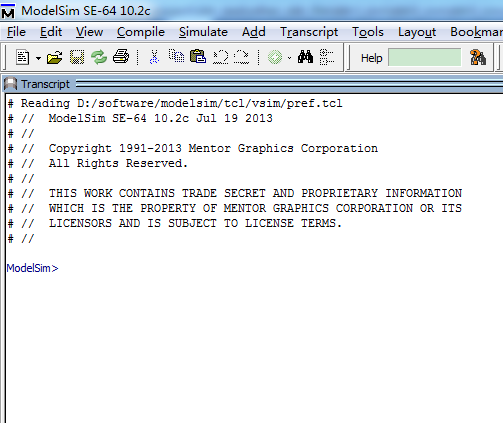

打开modelsim,你会发现因为你加的这一段,libaray是有变化的。

在modelsim中选择 file --> change directory。找到vivado建立的工程里面sim文件夹,是这个很深的文件夹 (我的工程文件夹是ddr3_sim)

好了,工作从原理上来说已经做完了。因为vivado的本意是让我们能能仿真一下这个example的,然后在modelsim中执行do sim.do 就可以了

实际上当然是不可以的,还差一点点。

记住你的工作目录是sim下,因为sim文件夹下才有这个sim.do文件。

第四步:修改sim.do的文件路径

其实从QuartusII 和modelsim联合仿真也可以看出,modelsim经常给我们纠结文件路径。原因很简单,modelsim的起始路径是QuartusII工程中的simulation子文件夹,和QuartusII的工程文件夹不同,所以出现差异。

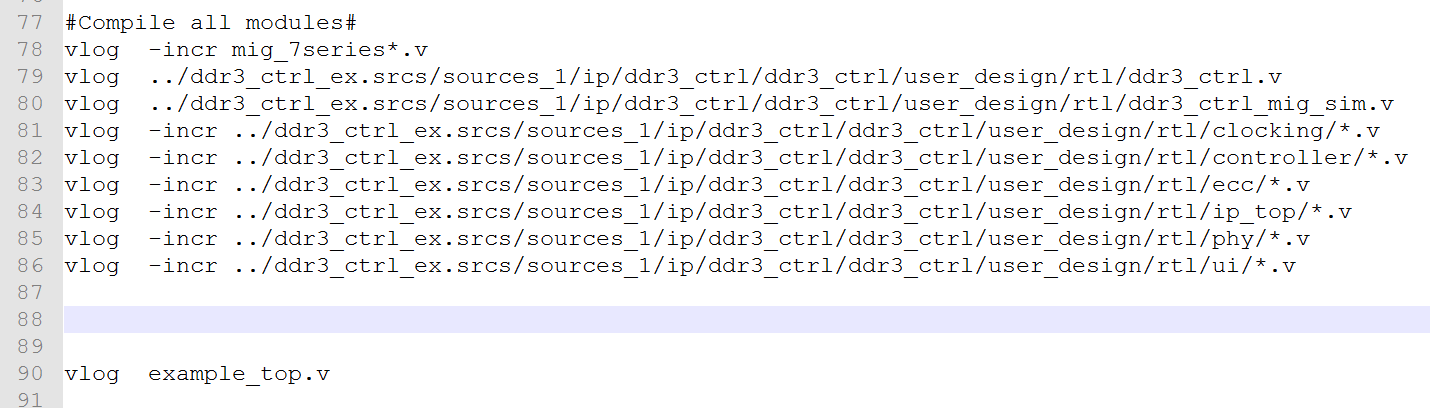

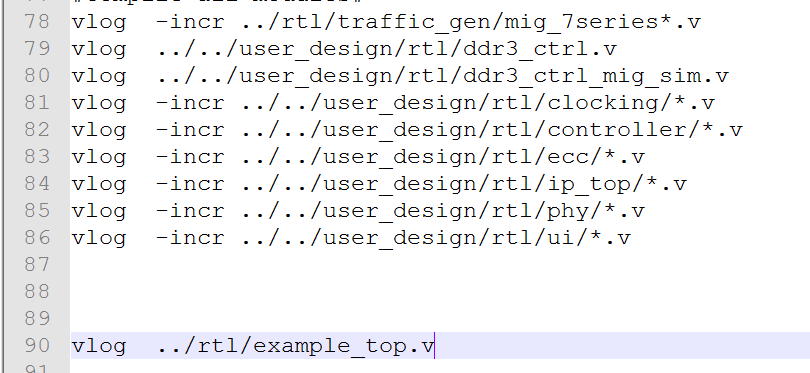

好了,回归本题。如何修改 ,先看看vivado给的原始路径

看到自动给的路径,两个字回应它:胡扯!

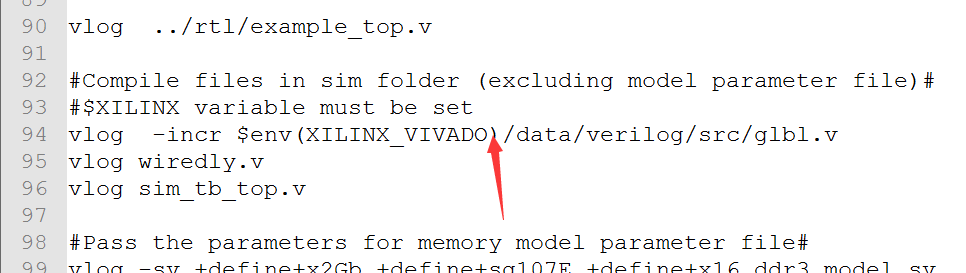

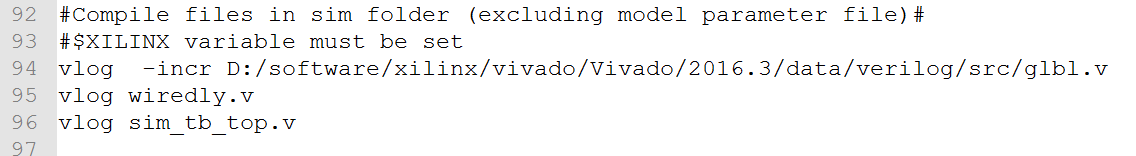

路径更改后是这样子的:

还有一行:第94行

修改成:

改成绝对路径吧,就是找到你的vivado安装目录下的这个glbl.v文件,然后指定。

OK ,一切完毕,现在就是就是最爽的一步

第五步:在modelsim的Transcript下执行 do sim.do 。 然后你就可以边喝茶边看着信息自己跳了

最后modelsim弹出一个框框,问finish不? 如果你选择 是, 那我只能给一个鄙视的眼神了。

欢迎加入: FPGA广东交流群:162664354

FPGA开发者联盟: 485678884

微信公众号:FPGA攻城狮之家

浙公网安备 33010602011771号

浙公网安备 33010602011771号