FPGA中改善时序性能的方法_advanced FPGA design

本文内容摘自《advanced FPGA design》对应中文版是 《高级FPGA设计,结构,实现,和优化》第一章中的内容

FPGA中改善时序,我相信也是大家最关心的话题之一,在这本书中列举了一些方法供给大家参考。

1,插入寄存器(Add Register Layers),在中文版中被翻译成:添加寄存器层次。即,在关键路径中插入寄存器。

这种方式会增加设计的时滞(clock latency)。插入了几个寄存器,结果输出就会延长几个周期,在不违反设计规格(对clock latency有要求)以及功能没有影响的时滞情况之下可以这么做。

2,并行结构。把串行改成并行。最典型的就是乘法器了。

作为一个16bit的乘法器,最省资源的就是等待16个clock出结果,也可以是设计成面积最大但是出来结果速度最快的,只需要一个周期就可以出来结果。

3,逻辑展开(Flatten Logic Structures)。中文版同样翻译的很保守:展平逻辑结构。

仔细看了看,觉得里面应该包含了连个知识点。第一是逻辑复制,特别是针对大扇出(详情在altera的官方视频资料中有提到),通常使用generate或者是在综合器中设定。第二个是消除代码中的优先级。这里需要多说一句:现在的工具很智能,就算你写成if else 有优先级的结构,有时候也能综合出并行结构。如果并行也符合你的设计要求,为了安全起见,最好还是写成case这种并行结构比较好。

4,寄存器平衡 (Register Balancing)。

寄存器平衡就是在你的关键路径中移动你的寄存器。第一就是你手动移动 —— 改代码。第二就是设定综合器让它自己移动 —— 不到万不得已不这么干,因为这么多导致代码移植性变差。

5,路径重组

这是最有意思的一个方法,也是体现你的设计水平的方式。结果书中给出的例子确实让我惊讶了一下。为啥呢,先贴出代码

第一版:

1 module randomlogic_1( 2 output reg [7:0] Out, 3 input [7:0] A, B, C, 4 input clk, 5 input Cond1, Cond2); 6 always @(posedge clk) 7 if(Cond1) 8 Out <= A; 9 else if(Cond2 && (C < 8)) 10 Out <= B; 11 else 12 Out <= C; 13 endmodule

第二版:

1 module randomlogic_2( 2 output reg [7:0] Out, 3 input [7:0] A, B, C, 4 input clk, 5 input Cond1, Cond2); 6 7 wire CondB = (Cond2 & !Cond1); 8 9 always @(posedge clk) 10 if(CondB && (C < 8)) 11 Out <= B; 12 else if(Cond1) 13 Out <= A; 14 else 15 Out <= C; 16 endmodule

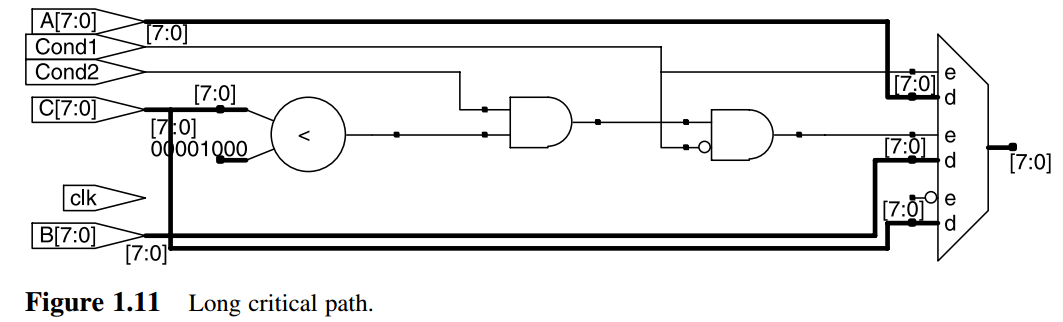

从代码上来看2版好像还比第一版路径更长,因为 out <= B,的路径从 Cond2 && (C < 8) 变成了 (Cond2 & !Cond1) && (C < 8)。似乎还变长了,怎么叫优化了呢?实际上,如果我们不看下面的图,自己模仿RTL Viewer,发现2版的关键路径真的比1短。书中给出的图示也是如此,这是第一版的视图,关键路径经历了4个器件

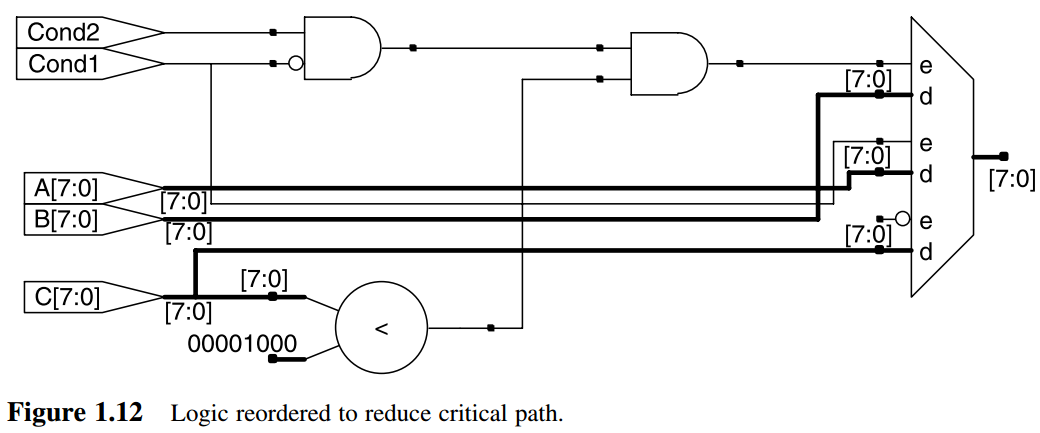

这是第二版的视图,关键路径居然少了一个器件。

这就是我惊讶的地方,因为这种做法从代码上看不出来。所以需要更高的硬件知识才能驾驭啊。

欢迎加入: FPGA广东交流群:162664354

FPGA开发者联盟: 485678884

浙公网安备 33010602011771号

浙公网安备 33010602011771号