openrisc 之 Wishbone总线学习笔记——接口信号定义

这部分内容就是copy下来的,网上到处都有。先看看接口啥样子,在详细说明

接口定义copy http://blog.csdn.net/ce123/article/details/6929897。百度文库里面很多文章中也是一样的说明

信号分类

SYSCON模块信号

CLK_O:输出信号,系统时钟,作为MASTER和SLAVE的时钟输入:

RST_O: 输出复位信号,作为MASTER和SLAVE的复位输入,使得WISHBONE接口内部的状态机全部恢复到起始态。

MASTER和SLAVE的共有信号

CLK_I:输入信号,MASTER和SLAVE的时钟输入端,所有WISHBONE输出信号都在CLK-I的上升沿有效;

DAT_O():数据输出信号,最大位宽为64位;

RST_I:输入信号,使得WISHBONE接口内部的状态机全部恢复到起始态;

TGD_I():输入信号,数据标签类型;

TGD_O():输出信号,数据标签类型;

MASTER端信号

ACK_I:输入信号,确认信号,当该信号有效时,表明一个总线周期结束;

ADR_O():输出信号,地址输出;

CYC_O:周期输出信号,当该信号有效,表明进程中的总线是有效的,即它确定了总线周期的持续时间。CYC_O从数据传输的第一个比特开始有效,到数据传输结束为止。

ERR_l:输入信号,当该信号有效,表明总线周期非正常结束,表示有错误发生:

LOCK_O:输出信号,当该信号有效,表明当前总线周期锁定,不能被其他进程中断;

RTY_I:输入信号,当该信号有效,表明MASTER还没有准备好接收或发送数据,重新请求总线;

SEL_O():输出信号,用于选择数据信号线的输出;

STB_O:输出信号,表明一个有效数据传送周期;

WE_O():读使能信号,决定信号的读和写功能。

SLAVE端信号

ACK_O:输出确认信号,表明总线周期结束;

ADR_I():地址输入信号:

CYC_I:输入信号,当该信号有效,表明进程中的总线是有效的,即它确定了总线周期的持续时间。CYC一0从数据传输的第一个比特开始有效,到数据传输结束为止。

ERR_O:错误输入信号,表明由于发生错误,周期终止;

LOCK_I:输入信号,当该信号有效,表明当前总线周期锁定,不能被其他进程中断;

RTY_O:输出信号,当该信号有效,表明SLAVE还没有准备好接收或发送数据,重新请求总线;

STB_I:输入信号,表明SLAVE被选中和主端通信;

WE_I:读写使能输入信号;

CLK_O/CLK_I:时钟信号。时钟信号由SYSCON模块产生,并送入各个主设备和从设备。SYSCON通常内部存在一个锁相环,将来源于芯片外的晶体振荡器或者时钟输入信号整形、分频或者倍频为芯片内所需要的时钟信号。所有Wishbone信号都同步到时钟信号上,包括复位信号。

RST_O/RST_I:同步复位信号,高电平有效。复位信号由SYSCON模块产生,并送入各主设备及从设备。

DAT_O()/DAT_I():主设备和从设备的之间的数据信号,数据可以由主设备传送给从设备,也可以由从设备传送给主设备。一对主设备和从设备之间最多存在两条数据总线,一条用于主设备向从设备传输数据,另外一条用于从设备向主设备传输数据。Wishbone规定数据总线的最大宽度为64位,这一规定实际上是考虑到目前商用处理器的最大位数为64,实际上数据总线的宽度可以是任意值。就笔者看来,在64位处理器以后,处理器将向多核方向发展,总线将向高速串行方向发展。

ADR_O(n…m)/ADR_I(n…m):地址信号,主设备输出地址到从设备。n取决于IP核的地址宽度,m取决于数据总线DAT_O()/DAT_I()的宽度和粒度。数据总线的粒度指的是数据总线能够一次传送的最小比特数,很多处理器如ARM的数据总线的粒度为1个字节,但是也有一些处理器如CEVA TeakLite DSP的数据总线粒度为2个字节。一个位宽为32比特、粒度为1个字节的数据总线的地址信号应定义为ADR_O(n…2)/ADR_I(n…2)。在传送数据时,具体哪些字节有效通过SEL_O()/SEL_I()信号(见下文)控制。

TGD_O/TGD_I()、TGA_O()/TGA_I():TGD_O/TGD_I()为数据标签,具体讲是附加于在数据总线DAT_O()/DAT_I()的标签,该标签可以用于传送关于数据总线的额外信息如奇偶校验信息、时间戳信息等。TGA_O/TGA_I()为地址标签,具体讲是附加于在地址总线ADR_O()/ADR_I()的标签,该标签可以用于传送关于地址总线的额外信息如地址总线奇偶校验信息、存储器保护信息等。Wishbone只规定了TGD_O/TGD_I和TGA_O()/TGA_I()的接口时序,用户可以定义TGD_O/TGD_I的具体含义。

TGC_O/TGC_I():TGC_O/TGC_I()为总线周期标签,该标签可以用于传送关于当前总线周期所进行操作的描述如操作类型(包括单次操作、块操作、RMW操作)、中断应答类型、缓存操作类型等。类似的,Wishbone只规定了TGC_O/TGC_I()的接口时序,用户可以定义TGD_O/TGD_I的具体含义。

ACK_O/ACK_I、ERR_O/ERR_I、RTY_O/RTY_I:主从设备间的操作结束方式信号。ACK表示成功,ERR表示错误,RTY表示重试(Retry)。操作总是在某一总线周期内完成的,因此操作结束方式也称为总线周期结束方式。成功是操作的正常结束方式,错误表示操作失败,造成失败的原因可能是地址或者数据校验错误,写操作或者读操作不支持等。重试表示从设备当前忙,不能及时处理该操作,该操作可以稍后重新发起。接收到操作失败或者重试后,主设备如何响应取决于主设备的设计者。

SEL_O()/SEL_I():有效数据总线选择信号,标识当前操作中数据总线上哪些比特是有效的,以总线粒度为单位。SEL_O()/SEL_I()的宽度为数据总线宽度除以数据总线粒度。比如一个具有32位宽、粒度为1个字节的数据总线的选择信号应定义为SEL_O(3:0)/ SEL_I(3:0),SEL(4’b1001)代表当前操作中数据总线的最高和最低字节有效。

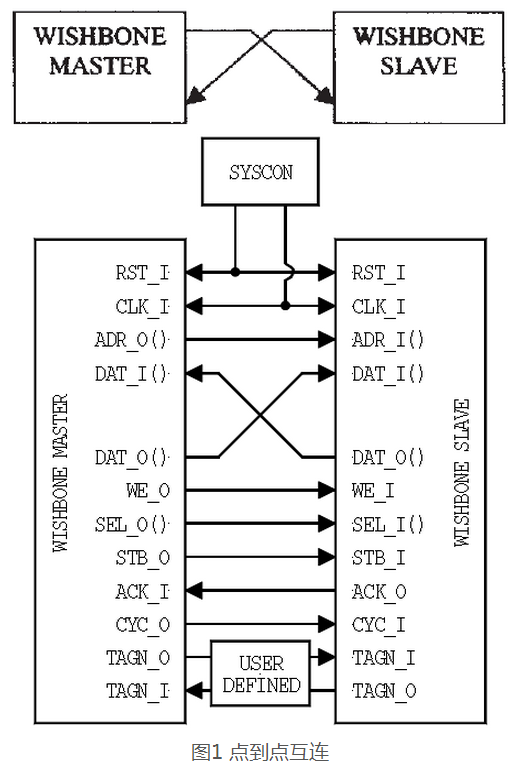

CYC_O/CYC_I、LOCK_O/LOCK_I、GNT_O()/GNT_I:总线周期信号CYC_O/CYC_I有效代表一个主设备请求总线使用权或者正在占有总线,但是不一定正在进行总线操作(是否正在进行总线操作取决于选通信号STB_O/STB_I是否有效)。只有该信号有效,Wishbone主设备和从设备接口的其它信号才有意义。CYC_O/CYC_I信号在一次总线操作过程中必须持续有效,比如一次块读操作可能需要多个时钟周期,CYC_O/CYC_I信号必须保持持续有效。实际上,该信号的实际作用等同于其他总线标准中的仲裁申请信号。当存在多个主设备时,它们可能希望同时进行总线操作,主设备通过仲裁申请信号向仲裁器申请总线占有权,仲裁器通过一定的仲裁优先级逻辑向其中一个选定的主设备发送总线允许信号GNT_O()/GNT_I,表示该主设备可以占用总线。GNT_O()是仲裁器输出的允许信号,一般有多个;而对于一个主设备,其允许信号输入GNT_I却只有一个。一次总线操作可能需要多个时钟周期,比如一次块操作。在操作过程中,仲裁器可能会提前将总线占用权收回并分配给其他主设备从而打断当前主设备的操作,LOCK_O/LOCK_I有效代表本次总线操作是不可打断的。仲裁器收到LOCK_I信号,就不会提前收回总线使用权。图1中只有一个主设备和一个从设备,因此没画出仲裁器模块,该模块可以视为是INTERCON的一部分,见本章最后给出的例子。

STB_O/STB_I:选通信号。选通有效代表主设备发起一次总线操作。只有选通信号有效(此时CYC_O/CYC_I也必须为高),ADR_O/ADR_I()、DAT_O()/DAT_I()、SEL_O()/SEL_I()才有意义。在Wishbone总线规范中,CYC_O/CYC_I是最高层的控制信号,只有该信号有效,STB_O/STB_I信号才有意义。一个信号有意义是指该信号的当前值是需要主设备或者从设备解释的,0为无效,1为有效,而一个信号没有意义是指该信号的当前值主设备和从设备不必关心,是0还是1都无效。

WE_O/WE_I:写使能信号,代表当前周期中进行的操作是写操作还是读操作。1代表写,0代表读。

浙公网安备 33010602011771号

浙公网安备 33010602011771号