DSP 6678 多核EDMA的使用

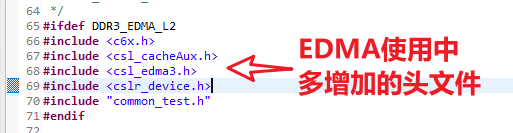

使用EDMA多增加使用的头文件

以core1举例说明

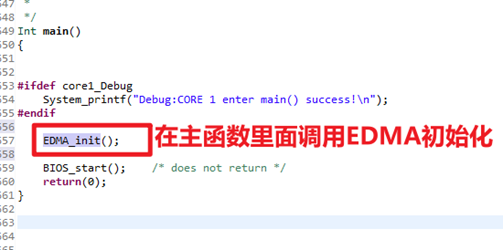

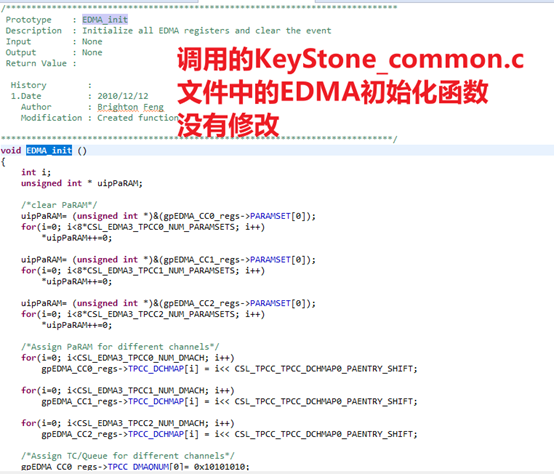

首先在主函数里面对EDMA进行初始化,初始化函数用的是KeyStone_common.c中的初始化函数,并且没有修改他。

问题

这里有疑问查阅资料有的地方说要初始化EDMA中断,还有什么事件,我这里使用的时候好像都没用到中断事件?

问题

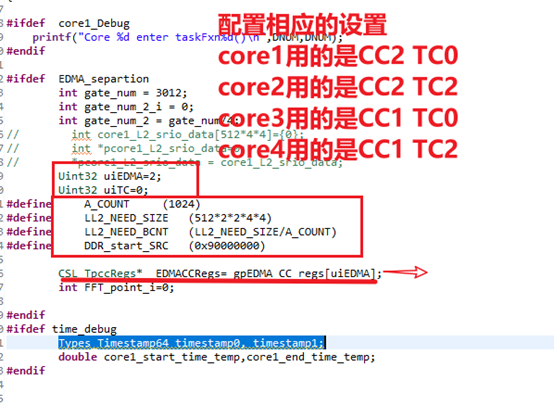

core1~4这样选择CC和 TC是否正确?应该如何配置?

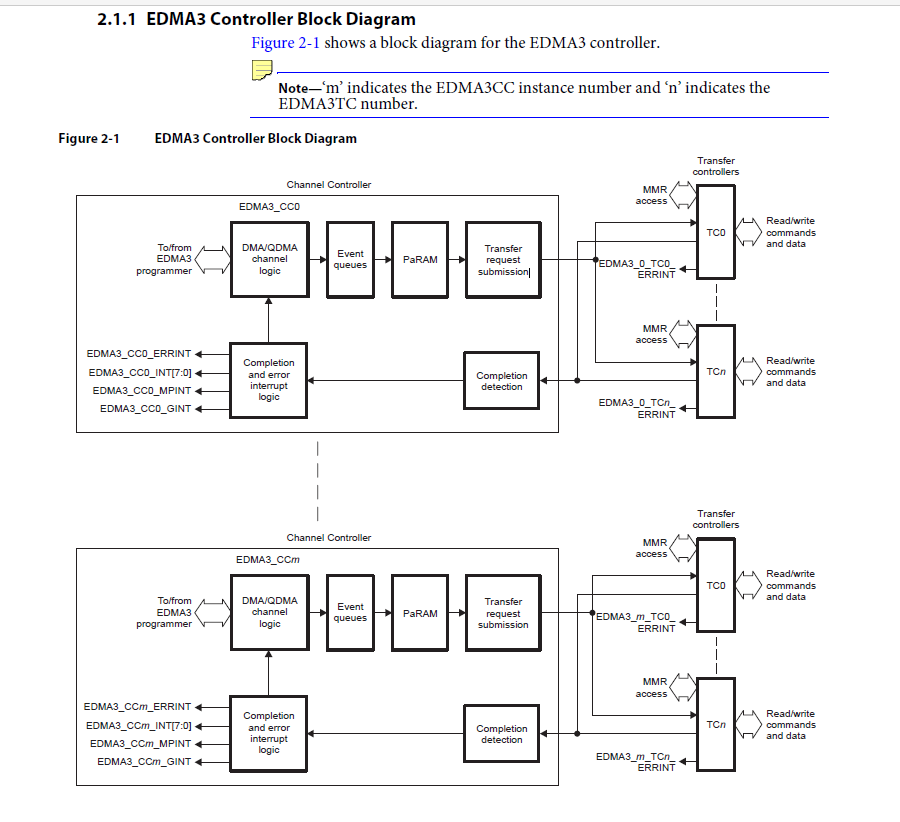

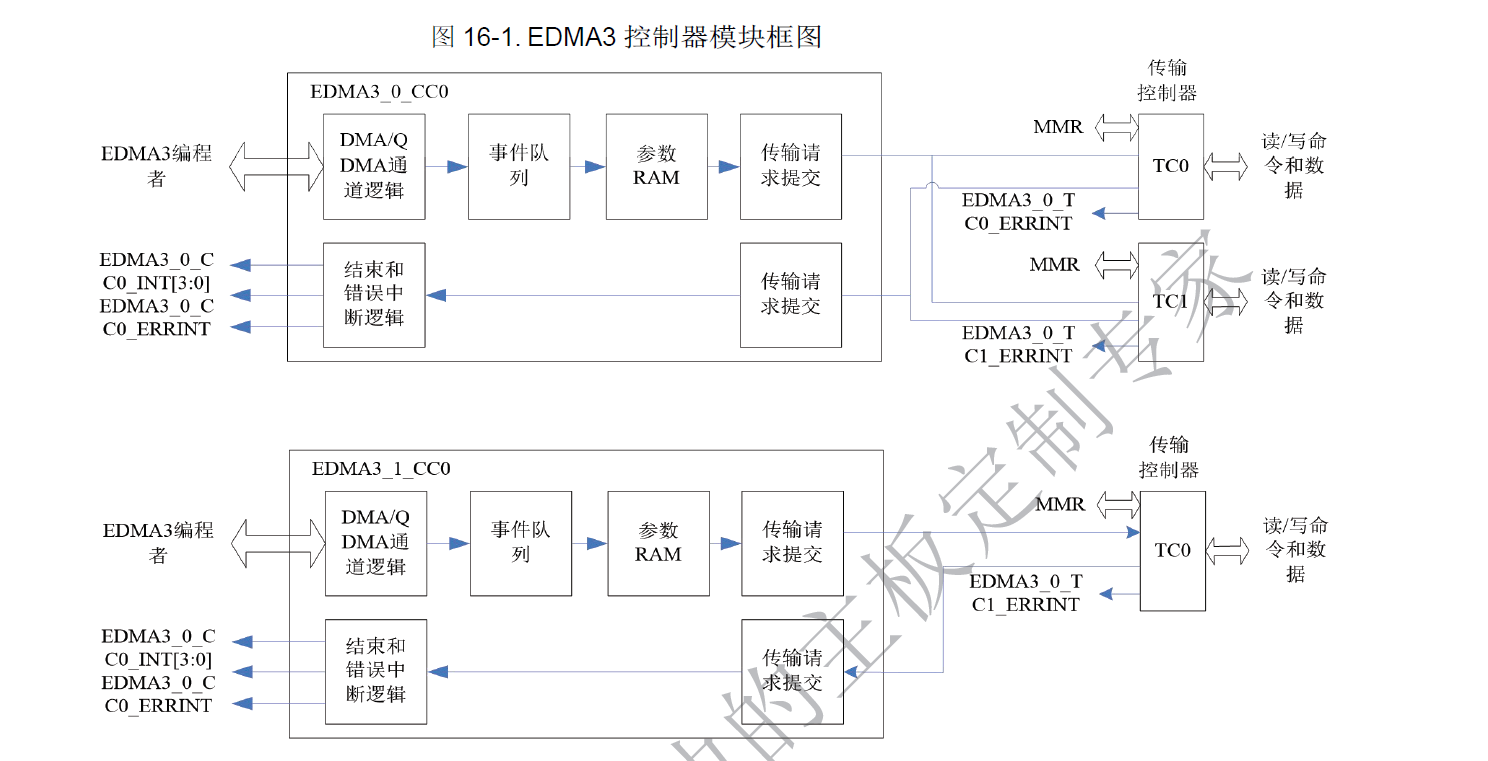

我目前了解到的是CC0是用于MSMC和DDR3的数据读写,CC1,CC2用于外部存储设备和各个core片内存储设备的数据读写。

EDMA传输函数

其中一共要循环读取793次,每次读取数据量为4*512*2*2*4B,因为我们需要实现的功能要求一批数据为512*2*2*4B,但是经过实际测量,EDMA这个函数,数据量读取的越大,吞吐量越接近TI官方手册说的理论值。所以我们一次选择读取4批数据到L2内,进行分离。

具体参数为:

DDR_start_SRC+gate_num_2_i*4*512*2*2*4 :为从DDR3读取数据的SRC地址。每次读取都要变化增量偏移一次。

问题

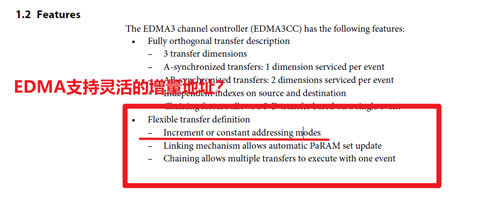

查阅TI官方给的EDMA手册知道,

那么想知道我们这种写SRC地址的方法是否就是手册说的 增量地址。还是应该有其他写法更合理?

还有,每个核我都是这么写的,没有涉及手册说的什么优先级,中断,不知道实际用起来安全性和稳定性怎么样?想知道怎么测试安全性稳定性

最后一个问题问题就是,我想要用EDMA从L2写数据到MSMC可行吗?因为我目前查到的资料都是说明都是DDR3~MSMC或者外部寄存器到L2。(四个核同时并行调用EDMA)

浙公网安备 33010602011771号

浙公网安备 33010602011771号