set_multicycle_path的使用

在设计中有时会碰到部分难以优化的大块组合逻辑,例如我们这次的设计中调用了DW的浮点sqrt的IP,尽管在综合时,工具已经最大effort去简化逻辑,路径上的cell已经基本上全都ulvt了,timing仍然无法在一个周期内满足。

如果是自己设计的电路模块,这种情况下或许可以拆分流水线来处理,但DW IP我们也无法修改。幸运的是,这次的协处理器接口刚好是一个2 cycle的timing,即实际上只要在2 cycle前搞定数据并满足setup,就能正常写入数据。因此像这种情况就完全可以使用set_multicycle_path。

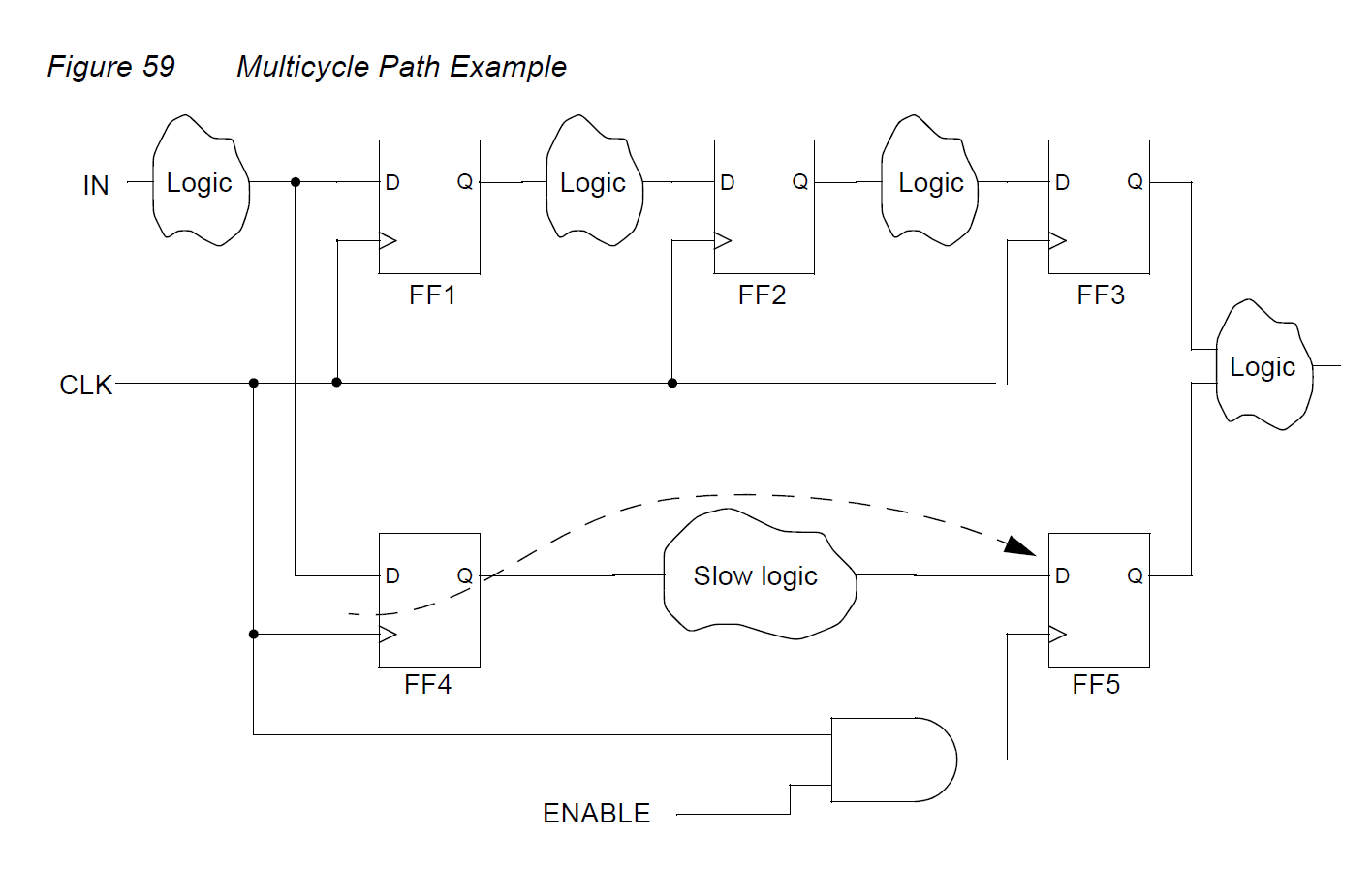

set_multicycle_path的原理如下图所示,针对电路中的一些慢速组合逻辑块,可以告诉工具,不按照默认情况检查其下一个cycle的setup和hold,转而检查第n个cycle后的setup和hold。

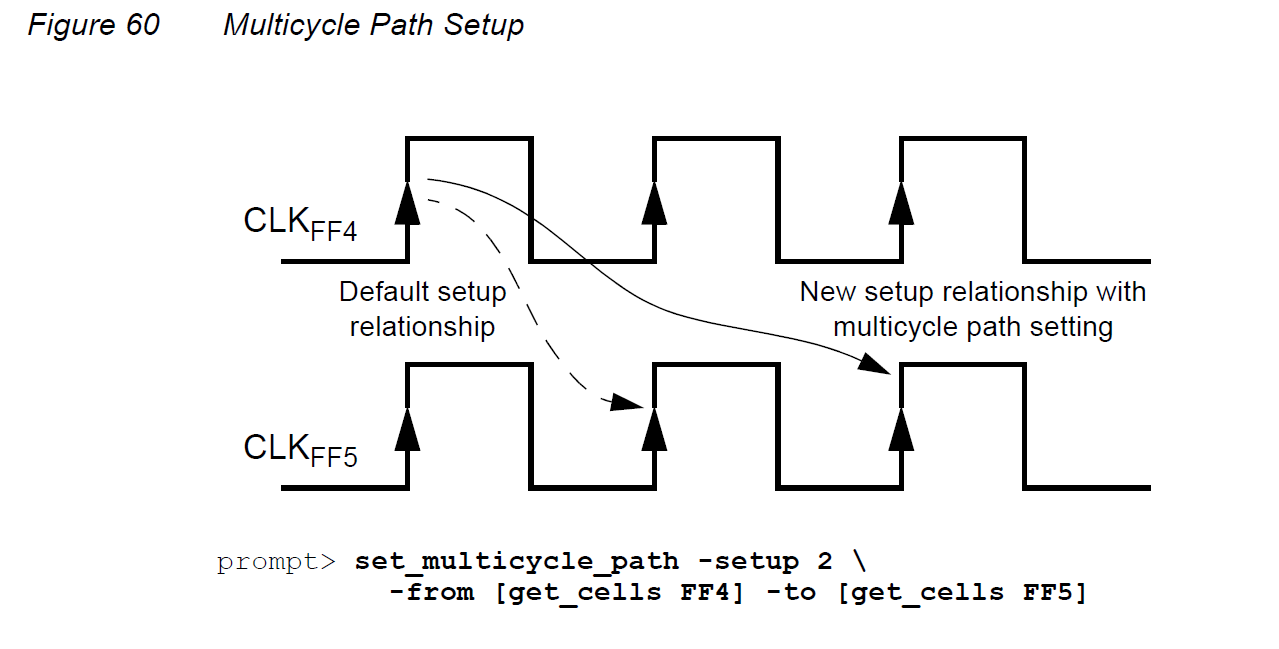

以此处为例,默认情况下,FF4到FF5的timing path会检查当前上升沿的FF4/Q->slow logic->FF5/D这段路径上的传播是否能够满足FF5的下一个上升沿的setup。但假设设计允许FF5在下一个时钟沿采不到正确数据,要再过一个cycle才采到,那么就可以通过set_multicycle_path -setup 2 -from [get_cells FF4] -to [get_cells FF5]来进行指定,这里的-setup代表设置的是setup,2代表着检查往后第2个cycle的上升沿,-from和-to参数指定了起始的寄存器和终点的寄存器,在这个例子里就是FF4和FF5:

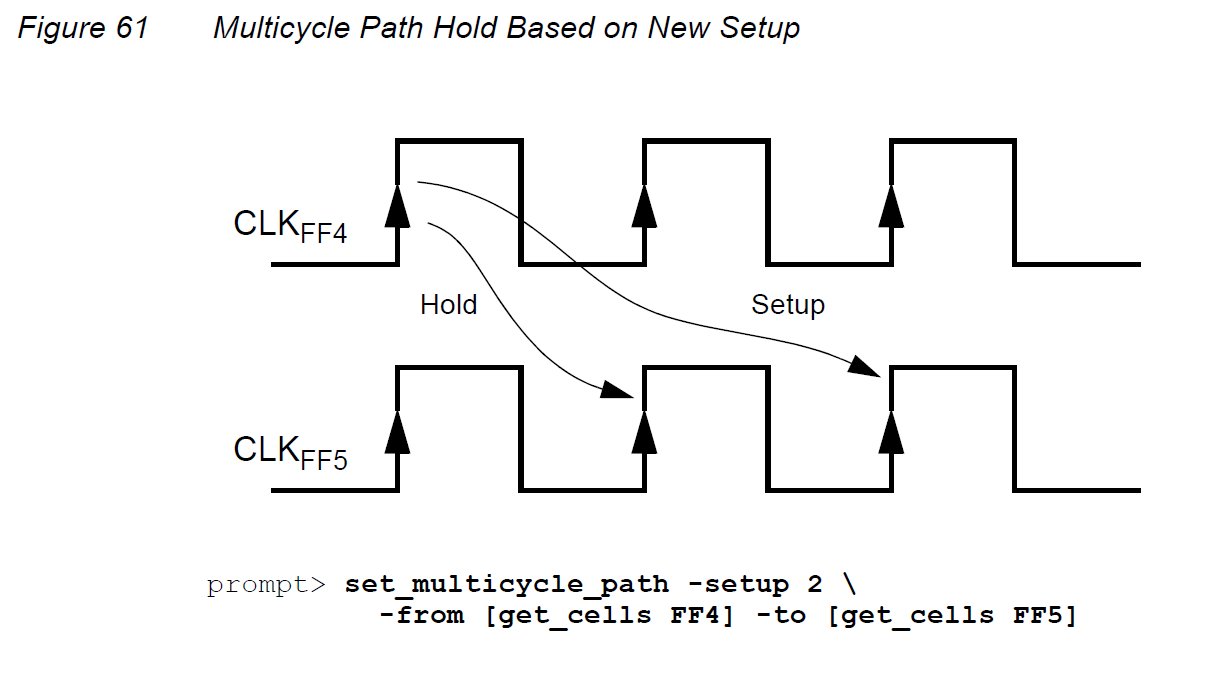

在设置了新的setup关系后,实际上hold关系也需要重新检查。工具默认情况下检查hold的起点会跟着一起跑到第二个cycle去,这样实际上放松了hold的检查,也与实际上数据开始产生的时间点不符,如下图所示,当setup被设置到第2个cycle检查时,hold的起点也会被设置到下一个cycle开始。

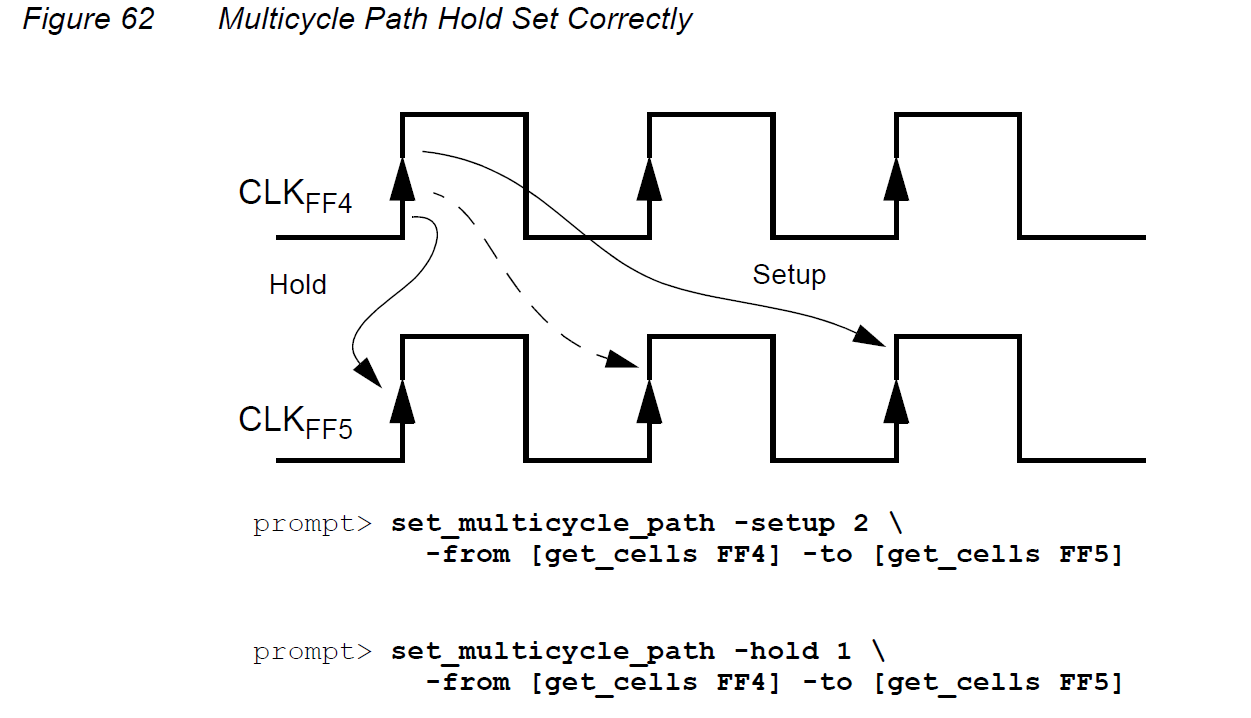

因此,除了setup之外,也需要额外对hold进行约束,可以通过set_multicycle_path -hold 1 -from [get_cells FF4] -to [get_cells FF5],这里的-hold代表设置的是hold,1代表着将hold的起点向前移动一个cycle。

具体的hold计算起点可以按照setup设置set_multicycle_path时的值,减去1,再减去hold设置set_multicycle_path时的值。

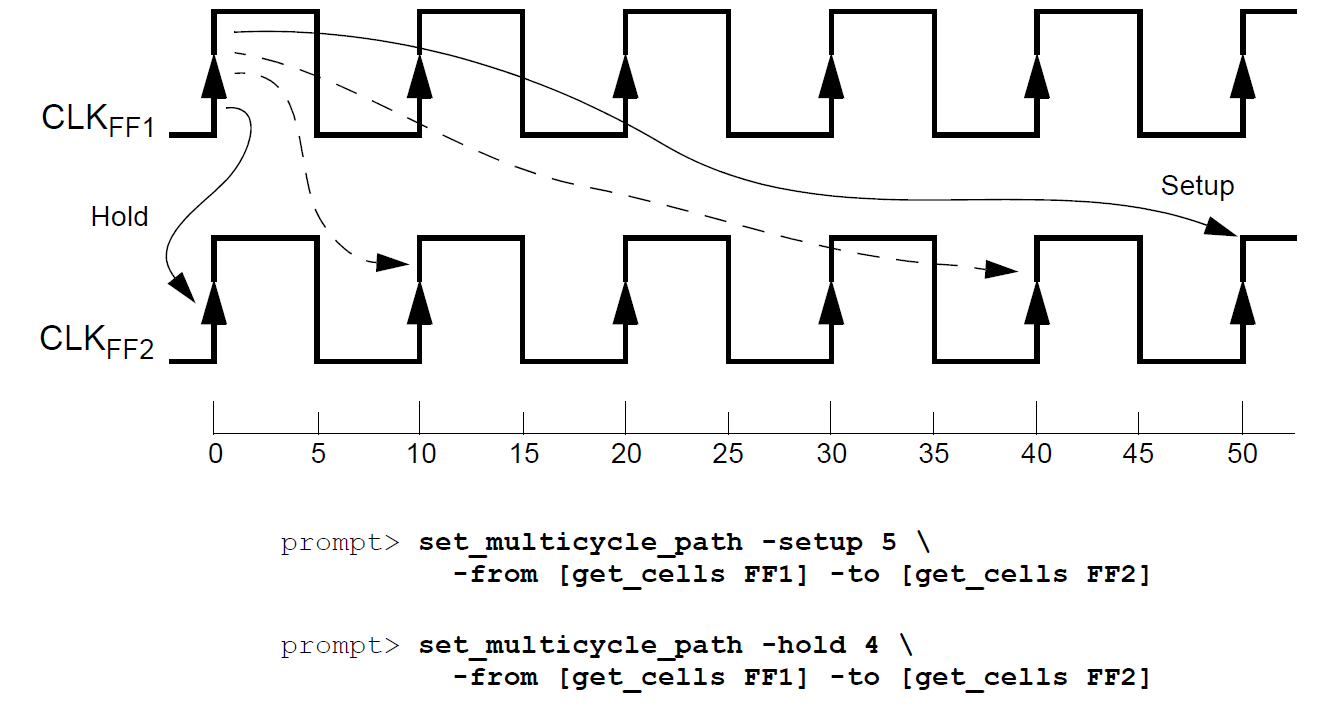

如果是更久的检查,那么设置也要相应调整,例如一个向后5 cycle的情况如下图:

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具