RRAM流片调试心得

RRAM流片调试心得

去年进行了一次RRAM的流片工作,也是人生第一次流片,一些工作细节不便涉及,但是可以谈谈这次流片以及后续测试中碰到的问题,以便后续查阅。

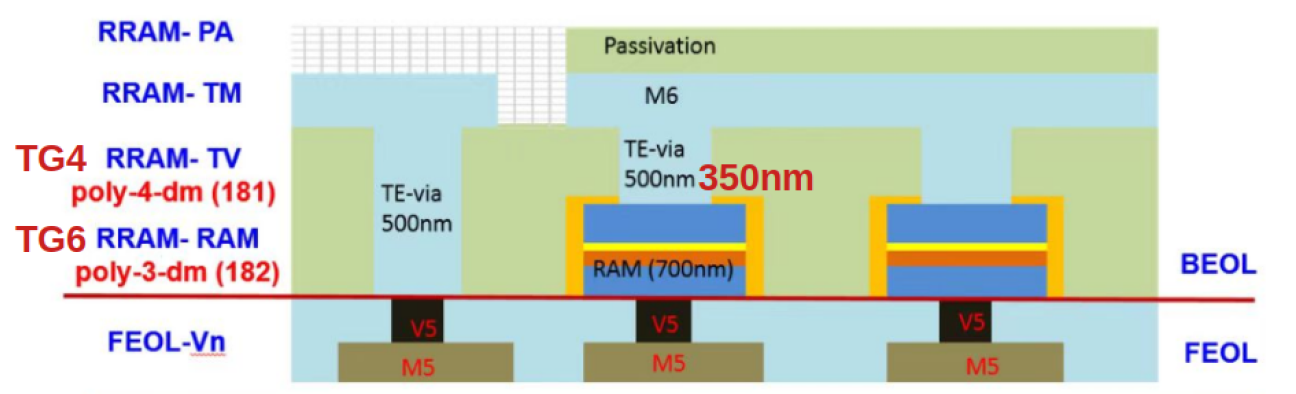

芯片于UMC完成180nm的CMOS前道工艺,共生长5层金属(到V5),随后出Fab,送到所里生长RRAM和M6完成后道工艺,版图需要遵守工艺需求,另外需要添加光学标记方便所里设备做对准。工艺图如下所示:

需要长RRAM的部分:先在V5上长一层RRAM(版名称为RRAM-RAM),即RRAM的下电极连接在V5上,然后在RRAM上再长一层金属通孔(版名称为RRAM-TV,这边也叫做V5')连接RRAM上电极与M6。

不需要长RRAM的部分:直接在V5上再长一层金属通孔V5'(对应版名称RRAM-TV)。

此处的要点在于需要按照与工艺约定的层次和尺寸来绘制图形(因为工艺那边并没有给一个DRC Rule,这些都要自己去人工检查完成),并且按照要求在版图里绘制好RRAM和V5'的图形,对于非RRAM的电路,必须在每个V5的通孔图案上再盖一个V5'的图案,否则会直接导致V5到M6之间断路,芯片废掉(尤其注意IO上的这个问题)。

随后谈到设计上,这次的RRAM Macro参考了一个以前流片过的设计,根据需求做了少量设计迭代,提供了一个做片内操作用的操作电压和参考电压产生电路,同时也提供了用Mux把RRAM Cell直接连到外部的测试模式,因为Form电压较高,片内不做Charge Pump的话到不了,所以选择了用片外Form,片内做Set/Reset/Read。

流片时碰到的第一个坑就是工艺那边并没有给一个很肯定的操作电压范围,也没有给RRAM的行为模型,只能自己根据过往资料猜测操作电压,当然最后回片时发现猜得还是准的。但这里干得不太聪明的事情是,这种情况其实应该给片内操作电压做成可调,但是当初偷懒没有,甚至干了个直接用3.3V和1.8V电源来供操作电压的操作,真是想给自己两耳光,偷懒偷出花来了,只有读出的比较参考电压做了可调。其实操作电压做成可调的话一点也不难,内部操作电压用LDO出,运放的输入端电压设计成可以片外给就行,片外接个变阻器或者电源之类的,扭一扭就能调电压,也不麻烦。

踩得第二个坑是测试引脚设计的不够全,进入SA的电压其实可以引出来,但是当时还是偷懒没引,所以调SA的时候一开始发现读不到东西的时候很诧异,但是里面的情况一点都不知道。整个大芯片也是犯了一样的错误,有个重要的引脚也没引出,引以为戒。做设计时不能预想到测试时的问题归根结底是个经验问题,只能说该交的学费还是得交。(好在最后还是测出来了,bug在哪愣是被我一通分析给分析出来了)

然后聊聊测试的问题。第一次自己做RRAM和CMOS的异质集成,多少有点纸上谈兵,做的时候就有点想当然。幸运的是所里的RRAM做的还挺好,刚上手测就观察到了明显的阻变现象,On/Off Ratio在10左右,很明显的阻变现象,Form之前电流非常微小,Form后开始出电流,Reset后电流变小,Set后电流变大。

但是一个难绷的问题是比预期阻值小了10倍,哈哈。

读出电流比预期大了10倍,SA读个der,怎么读都是1。

之后个把月的时间都在努力解决这个问题,尝试过的方法包括调WL电压,控脉冲宽度,结果效果都不好。最后终于试出来的方法是直接在电源上限流,Form和Set时做一个100uA左右的限流,就好了,阻值一下子爬到预期了,Reset限500uA,防止把Cell给弄坏。

原理上很好理解,Form和Set都是生长导电细丝通道,没限流那就长猛了,一旦太粗的话阻值肯定掉的小了,而且救不回来。Reset的话不怎么会影响导电细丝形状问题,所以限流给大点就行。之前不限流我们能跑到几百mA去,直接给Cell干的挺挺的 😦

电路上可以给片内操作电压源就弄个限流电路,不过更多是出于保护目的,我觉得最关键的是写入电路应该在Driver上对BL和SL整限流。

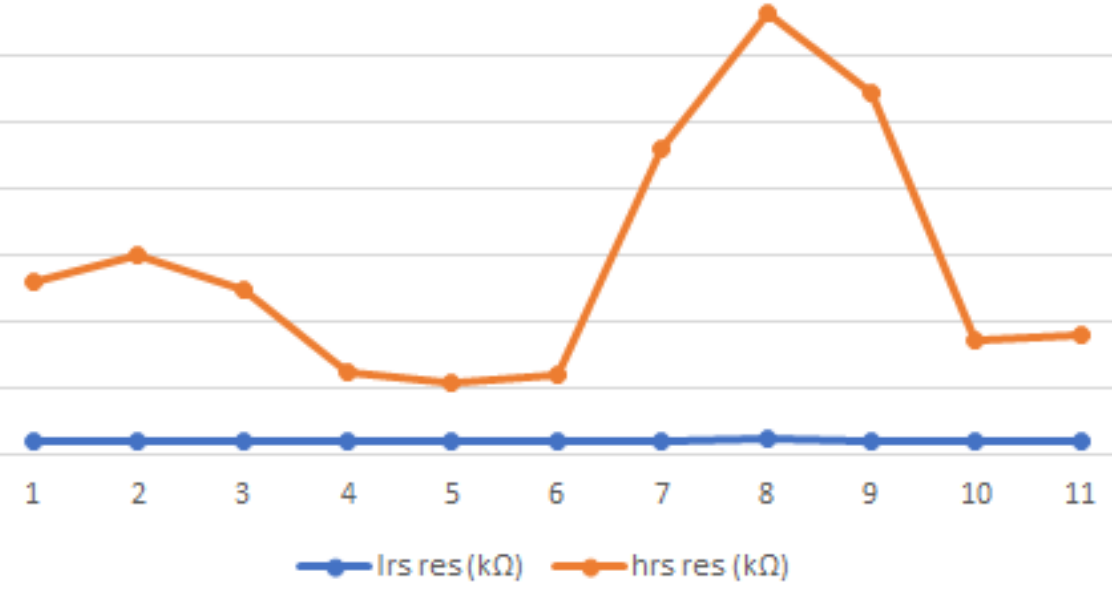

关于器件Variation,评价是建立了一下新的认识,LRS基本上稳如老狗,HRS容易飘到🐎都认不出来(这里就是开环做Set/Reset,没搞Write-Verify,搞一下的话肯定不会这么难看)。只读0/1的话其实够用,On/Off Ratio最小也有5,读电压给的大一点,SA很容易分辨出来,但是做多值的话,我不敢想,哈哈。编程上做做优化的话或许会更好。

关于RRAM实用化的问题,我觉得这事没啥好疑虑了吧,这次实测后我对这器件更看好了(之前就挺看好)。我们所里草台班子工艺线做的RRAM,测下来也是能用的,良率不错,Variation也能接受(就做二值的话),尤其在我这电路一点没考虑可靠性,做的各种毛糙的情况下,居然还能用,挺开心的。TSMC之类的Foundry再发发力,这玩意我觉得前景不小(就看多层能做到啥样,能不能成本上把Flash给赢了)。

可靠性上的问题值得研究的东西还是挺多的,编程上的限流,怎么高效的闭环编程(开环编程还是有点极端了)之类的,这次做完后就有了不少思考,现在做的这个也就是个学术产物,真要想用的话得考虑的东西不少。

最后感谢流片时帮忙的师弟师妹,感谢合作单位做测试的学弟,这事上我就负责出点子,出力的大头在其他人,幸而结果不错,希望后面Paper也顺利。

最后吐槽一句,这玩意下次再做的话,流程上真的得先找人去把器件扫完,建个Verilog-A模型再拿来仿真(拿开源的模型改参数拟合一下都行),我们这次拿理想电阻在那折腾,得亏做出来的东西能使。

浙公网安备 33010602011771号

浙公网安备 33010602011771号