模拟集成电路设计系列博客——9.4 ESD保护单元

模拟集成电路设计 9.4 ESD保护单元

ESD,即electrostatic discharge(静电放电)是集成电路设计中的一个经典问题。通常在电路的生产和使用过程中,很容易由于各种原因积累大量的静电电荷,一旦产生静电放电,极高的静电电压(可能\(>1000V\))会对电路产生不可逆的破坏。因此需要通过ESD保护单元的设计来避免这种情况,即通过ESD避免电荷累积,及时将静电电荷进行释放。

随着工艺制程的发展,器件尺寸越来越小,结深越来越浅,栅极越来越薄,所以静电击穿越来越容易,所有的芯片设计都要解决ESD问题。

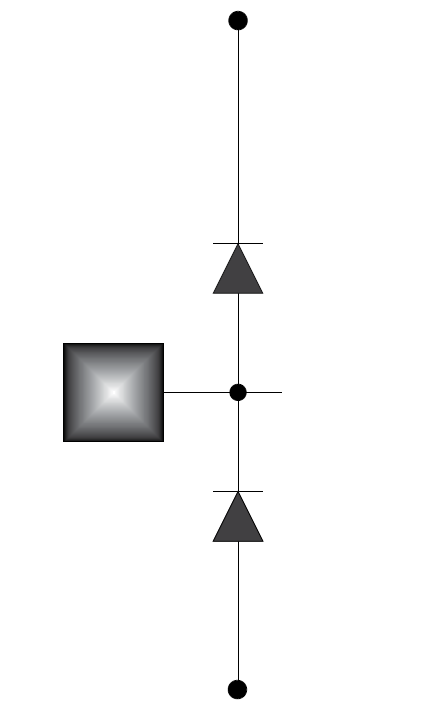

一种最简单的CMOS工艺的片上ESD保护单元是所谓的双二极管电路,随着n沟道晶体管和p沟道晶体管均可以在一个晶圆上实现,我们可以利用p扩散区和n扩散区实现二极管作为保护网络。如下图所示,这个电路可以称为DD(dual-diode) ESD,可以解决电气过应力(EOS,electrical overstress)和ESD问题,这个组件双向且对称开启。

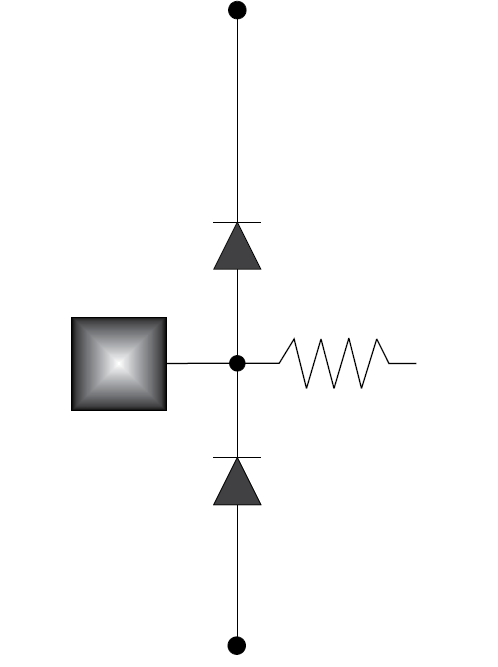

另一种常用的CMOS片上ESD保护单元是带有串联电阻的DD结构。而高速数字和射频应用需要将接收器上的串联电阻降至最低,而模拟应用可以使用具有阻值较大的电阻。

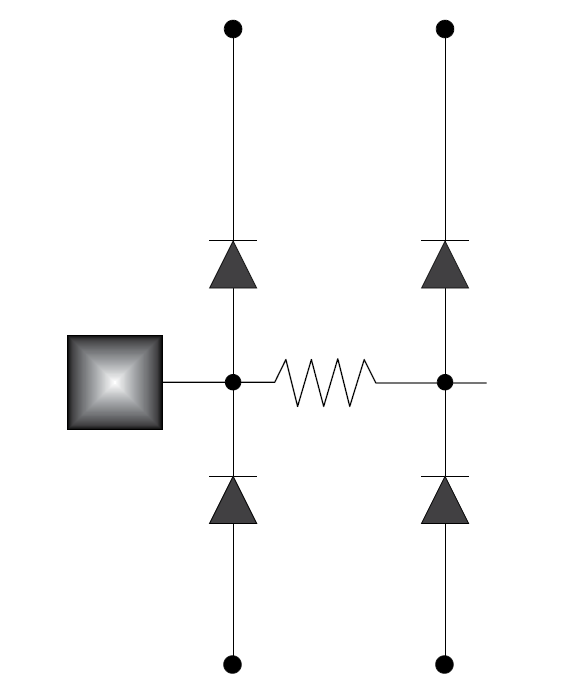

在CMOS工艺中,有一些电路需要定制以应对特定的ESD问题,有些这类电路也可以解决EOS问题,但有些不行。下图所示的电路可用于解决带电器件模型(charged device model, CDM)问题,电路可以建立备用电流路径,因此CDM电流不会流过小型结构和门控结构。CDM 电路将电流从存储在\(V_{DD}\)电源轨或\(V_{SS}\)衬底上的电荷中转移出来。这些CDM电路通常是放置在靠近故障电路元件的第二级元件。这些电路电容低且体积小,可能不会引发EOS问题。

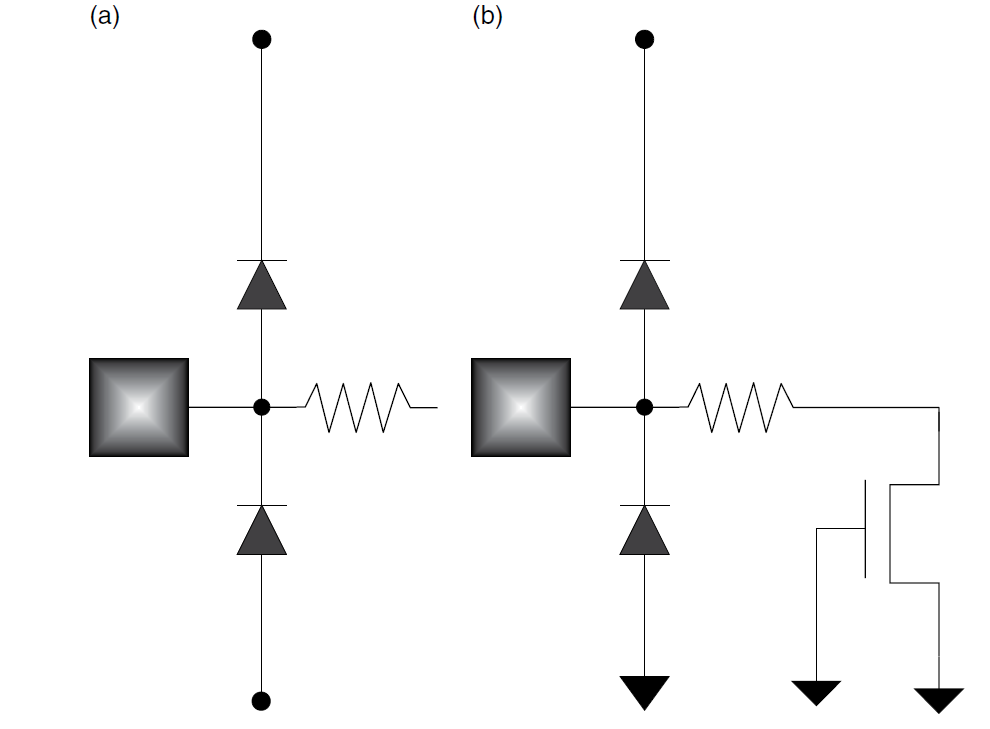

还有一种解决CDM问题的电路,如下图所示,下图(a)中是简单的DD电阻ESD保护电路,(b)则是在此基础是增加了栅极接地n沟道MOS管(grounded-gate n-channel MOS GGNMOS)。

在模拟和数字的集成中,一种常见的做法是通过隔离来自核心功能区的模拟功能,减少来自数字电路的同步开关噪声。然而,完全隔离导致不存在电流路径时,可能会引入模拟区域的ESD问题。我们一般不希望在数字\(V_{DD}\)与模拟\(V_{DD}\)之间直接建立电气连接以及使用ESD电源钳位的电源轨。更好的选择是在各自的电源域内利用ESD电源钳位,并通过衬底提供双向的连接。

在数字电路应用中,二极管元件的数量的选择是为了允许接地轨之间的电压差。ESD电路放置在地之间会影响ESD和噪声。

模拟和数字集成中的ESD设计实践如下:

-

在模拟和数字的地之间使用双向ESD保护

-

根据必要的电压差以及电容耦合要求选择串联的二极管数量。

典型的ESD保护有以下两种方案:

- 对称背靠背二极管串

- 非对称背靠背二极管串

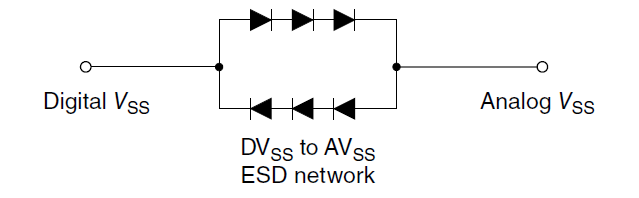

下图所示的是对称背靠背二极管串,连接在数字域的地和模拟域的地之间,在需要对称的电压裕度或差分电路的设计中,需要对称的背靠背二极管串。

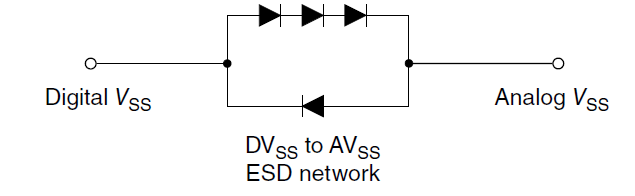

而如果电路并不需要对称的电压裕度,那么就可以使用如下图所示的非对称背靠背二极管串。

我们之前简单介绍过栅极接地n沟道MOS管(GGNMOS),这也是一种常用的ESD保护电路。在这种保护网络中,MOSFET栅极接地,在正偏压期间将会关闭。如下图所示,该电路可以解决EOS和ESD问题。当正偏压超过MOSFET栅极击穿电压时,电路对正偏压导通。对于负偏压,MOSFET n沟道扩散向衬底正偏。这种保护从根本上说是双向和不对称的。MOS器件在大电流下会受到电流收缩(electrocurrent constriction)的影响。电流收缩会导致MOS器件的高电流鲁棒性降低。在MOS器件中引入压载(Ballasting techniques)技术,可以在多指MOS结构的单个MOS“指”中,以及“指”到“指”之间提供均匀的电流分布,这属于版图技术的范畴。

对于模拟应用来说,大型MOS管被用于信号引脚和电源轨之间。对于低压CMOS(LVCMOS)应用,常用电源轨和地轨之间的ESD电路是RC触发的MOS电路。在模拟电源应用中,这可用于电压转换器的输出节点和其他模拟电路应用。

使用响应人体模型(human body model, HBM)脉冲的频率触发器,可以在HBM情况下导通ESD电路,但在正常芯片操作期间不导通。如下图所示:

此外还有一些基于可控硅整流电路的ESD保护单元结构,这里不作太多介绍。

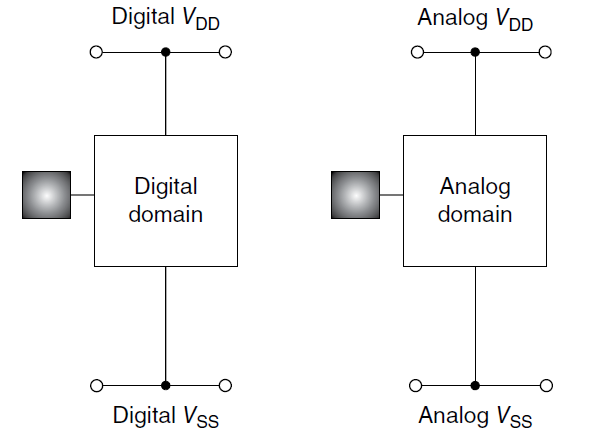

接下来我们再进一步详细讨论一下数模混合芯片中两个域之间的ESD隔离的问题。下图展示了模拟域和数字域隔离的芯片架构。但这种简单的数字域和模拟域的完全分离会导致信号引脚ESD故障和信号引脚到信号引脚故障。

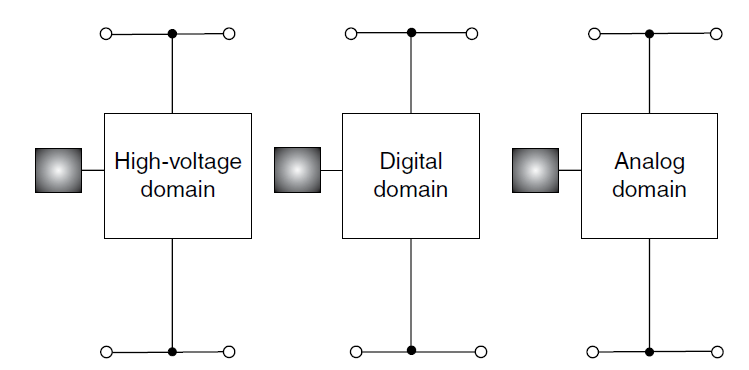

下图则展示了同时具有高压、数字和模拟域的架构。而电源轨在混合信号芯片中是分离的,但是各个域通过衬底耦合。

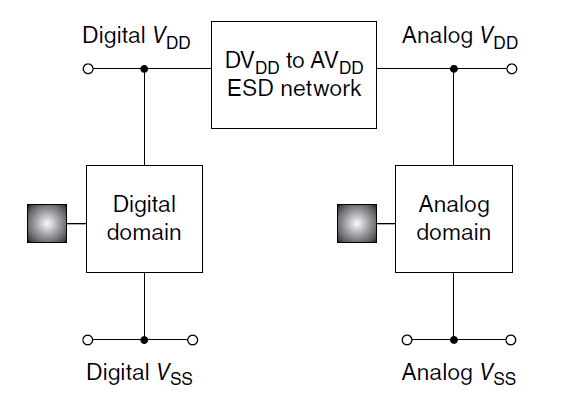

一种解决模拟域ESD问题的方案是将\(AV_{DD}\)耦合到数字\(V_{DD}\) (\(DV_{DD}\)) ,如下图所示。这个ESD网络可以是

单向或双向。例如,轨间ESD网络可以是单个二极管元件,其阳极连接到\(AV_{DD}\)电源轨,阴极连接到\(V_{DD}\) 电源轨。以这种方式,电流可以从\(AV_{DD}\)电源轨流出,但向相反方向整流。

这个ESD方案在早期芯片开发中使用,但是现在已经不再常用,包括以下原因:

- 电源供电电压不同

- 电源电压需要排序

- 电源噪声耦合

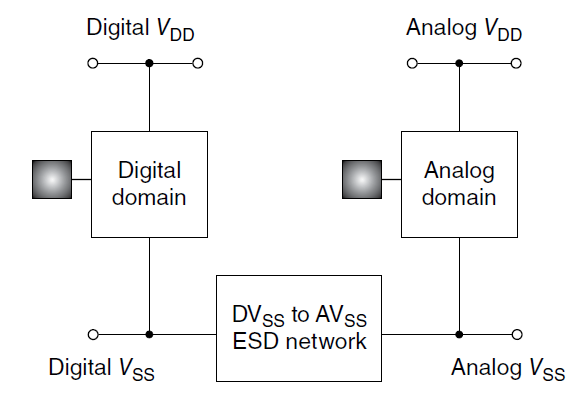

另一个解决模拟域ESD问题的方案是将\(AV_{SS}\)耦合到数字地(\(DV_{SS}\))电源轨,如下图所示。该网络可以是单向的,也可以是双向的。轨间ESD网络可以是电阻器、单个二极管元件、串联二极管、二极管配置的MOSFET或其他器件。这种ESD解决方案更常用,因为不存在接地电位差或电源排序的问题。

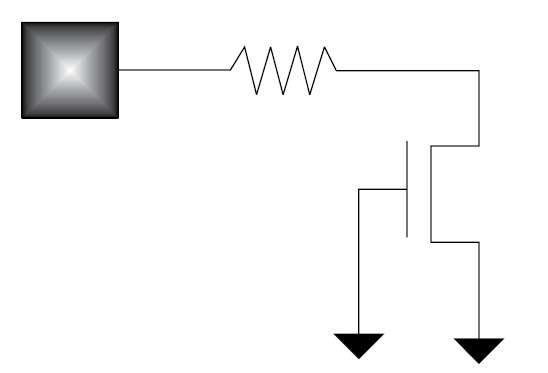

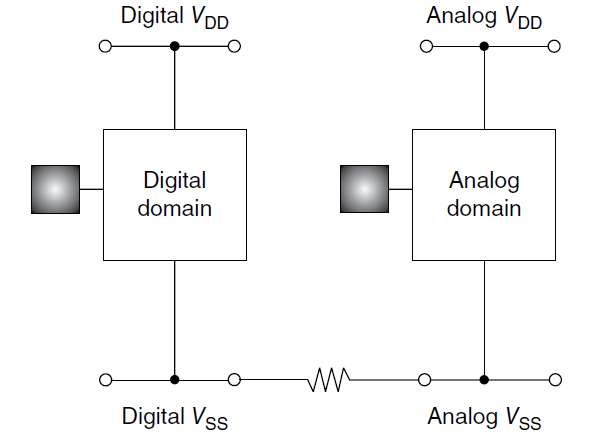

下图展示了一个使用电阻作为轨间耦合的例子。

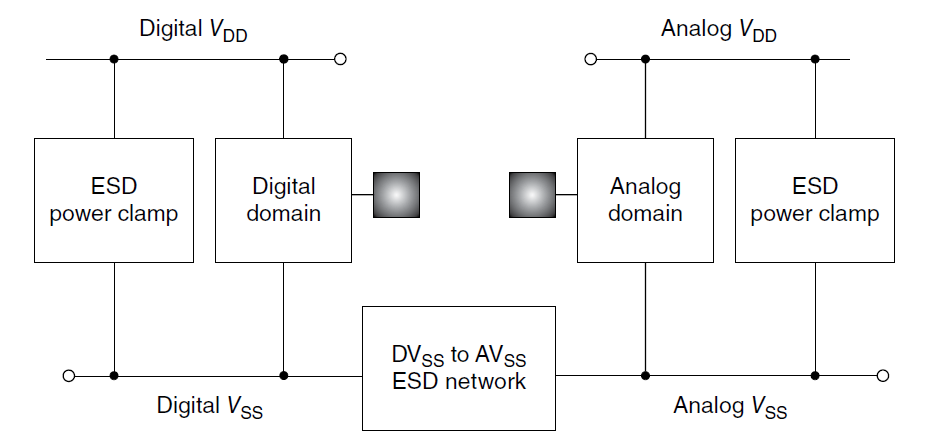

如今,混合信号芯片架构每个域都包含ESD电源钳位。下图展示了包括\(AV_{SS}\)至\(DV_{SS}\)电源轨之间的ESD网络,以及每个域的\(V_{DD}\)和\(V_{SS}\)之间的ESD电源钳位。

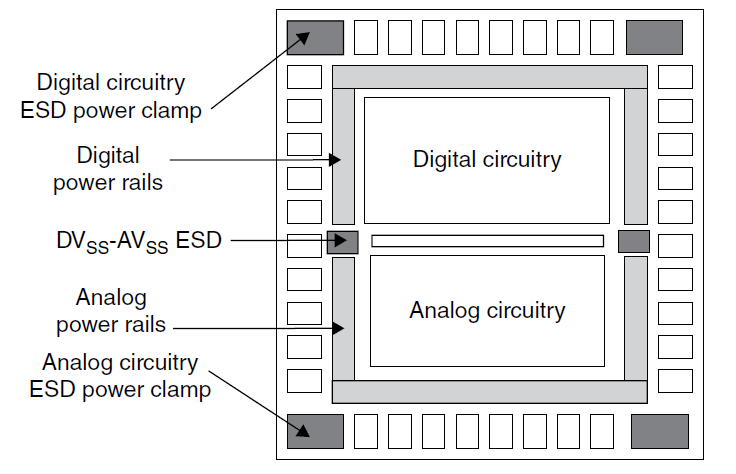

下图则展示了上图架构的混合信号芯片Floorplan。

在ESD设计综合中,ESD电源钳位被放置在带有信号绑线焊盘,电源绑线焊盘和电源总线的“pad ring”中。在许多芯片设计中,芯片的角落没有被使用,不使用这些角洛的原因是:

- 设计规则限制在拐角处放置信号引脚

- 芯片角上的机械应力会影响电路

- 芯片角上的光刻控制

- 需要放置识别标记

- 角落是半导体芯片中存在的“空白”区域。

但在ESD设计综合中的常见做法是利用该角区域进行放置电源和接地电路之间的ESD电源钳位。对于混合信号设计,其中两个角可用于数字域ESD电源钳位(例如,\(DV_{DD}\)和\(DV_{SS}\)),另外两个角可用于模拟电源域ESD电源钳位(例如\(AV_{DD}\)和\(AV_{SS}\))。 在这种架构中,两个电源域之间的“断路器单元”可以使用地到地单元(\(AV_{SS}\)到\(DV_{SS}\))。这些断路器单元可以放置在外围架构设计中。在这些设计中,数字电路是典型的与模拟域分离,以避免数字噪声影响模拟电路。

在超大型半导体芯片或需要高ESD鲁棒性的小型半导体芯片的外围I/O设计中,ESD电源钳位以更高的空间频率放置。ESD电源钳位的自然位置位于外围设备中需要\(V_{DD}\)或\(V_{SS}\)电源引脚的“标准单元”区域。在某些 ASIC 中,例如微处理器,或工厂的标准单元中,给定数量的 I/O 单元,需要放置给定频率的\(V_{DD}\)和\(V_{SS}\)电源引脚。例如,在某些情况下,需要在每五个I/O标准单元的相邻处放置一个电源引脚。在“电源单元”中放置 ESD 电源箝位,允许在每个I/O信号引脚的给定周期内本地放置 ESD 网络。此外,作为电源引脚频率要求的一部分,ESD电源钳位的放置可以自然地集成到设计方法中。在该系统中,完整的ESD功率钳位网络以给定的周期包含在半导体芯片设计的整个外围。

参考资料:

"ESD Analog Circuits and Design", Steven H. Voldman

浙公网安备 33010602011771号

浙公网安备 33010602011771号