模拟集成电路设计系列博客——9.3 采样保持电路

模拟集成电路设计 9.3 采样保持电路

采样保持电路是集成电路中的一个重要组件,尤其是在数据转换器中。在许多情况下,使用采样保持(在数据转换器的前端)可以大大减少由于转换器内部操作中的延迟时间略有不同而导致的误差。

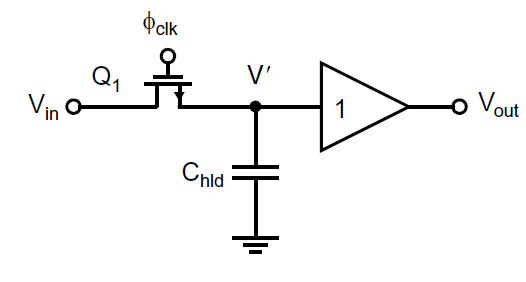

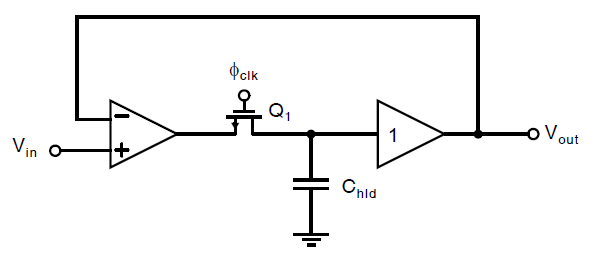

采样保持电路的一种最简单的实现方式如下图所示,当\(\phi_{clk}\)为高时,\(V^{'}\)跟随\(V_{in}\)。当\(\phi_{clk}\)为低时,\(V^{'}\)将会保持恒定,保持当\(\phi_{clk}\)降低时\(V_{in}\)的值。不幸的是,此时\(V^{'}\)将有一个由沟道电荷引起负的误差(指采样保持电路从采样模式切换到保持模式时出现的误差,即保持的信号与采样时的信号会略有误差)。\(Q_1\)关闭时,其沟道电荷必须从其栅极下方流出到其结处。因为电荷为负,它会导致结电压有负的毛刺。如果假设\(V_{in}\)节点的源阻抗非常低,那么这个节点上的毛刺会很小,并且持续时间很短。然而,负电荷通过\(C_{hld}\)连接到它的结(即节点\(V^{'}\)),这将导致持久的负电压变化(直到\(Q_1\)再次打开)。

如果时钟\(\phi_{clk}\)关闭得很快,那么沟道电荷将均匀地流入两个结 [Shieh, 1987]。在电荷流出到两个结点时,流进\(V^{'}\)处的结的电荷由下式给出:

其中\(V_{eff}\)为:

此处\(V_{in}\)是\(Q_1\)关断时的输入电压,这里应该注意的是,这个结果假设时钟信号\(\phi_{clk}\) 的摆幅为\(V_{DD}\)到电路中最低电压。

\(V^{'}\)的改变可以通过\(Q=CV\)求得:

注意\(\Delta V^{'}\)与\(V_{in}\)线性相关,这会导致整个采样保持电路的增益误差。然而,更重要的是\(\Delta V^{'}\)与\(V_{tn}\)线性相关,而\(V_{tn}\)与\(V_{in}\)之间则是非线性的,由于源极到基极的电压的变化触发了体效应(假设基极连接到其中一个电压轨)。与\(V_{in}\)的非线性关系导致了整个采样保持电路的失真。

由于栅极重叠电容,\(V^{'}\)还有一个额外的变化。使用之前类似的推导,我们有:

其中\(V_{SS}\)是电路中最低的电压。这个分量一般远远小于由于沟道电荷带来的误差,并且由于它与信号无关,因此仅表现为偏移。因此,这个错误分量通常不重要,因为在大多数系统中通常可以消除与信号无关的偏移。但是,如果不注意确保时钟信号\(\phi_{clk}\)相对无噪声,则会导致噪声问题。例如时钟信号简单的通过反相器连接到数字电源而具有电源噪声时,该电路的电源抑制比可能较差。

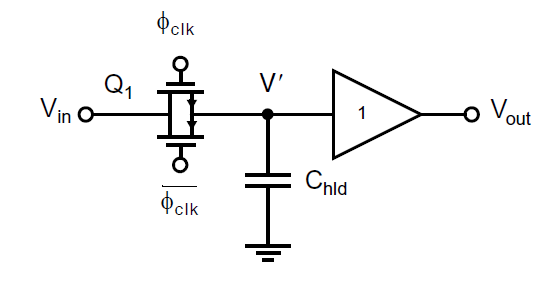

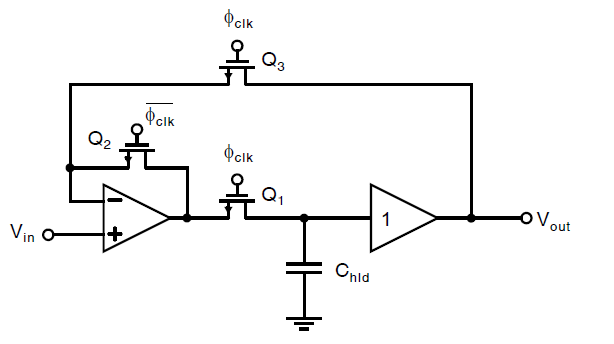

许多更改方案被提出,以最小化与信号相关的保持误差。一种方法是用CMOS传输门代替n沟道开关,如下图所示。这背后的想法是,如果p沟道晶体管的尺寸与n沟道晶体管的尺寸相同,则当传输门关闭时,每个晶体管引起的电荷注入将被抵消。这个结论当\(V_{in}\)位于电源的中间区域时是成立的,但需要假设时钟波形很快且完全互补。不幸的是,这些条件在实践中很少能够实现。当考虑时钟波形的有限斜率时,可以看出关断晶体管的时间与信号有关,这种信号依赖性导致n沟道晶体管与P沟道晶体管在不同的时间关断。即使我们忽略了由不完美的时钟引起的错误,但\(V_{in}\)更接近\(V_{DD}\)时,来自p沟道晶体管的电荷大于n沟道晶体管,因为它的有效栅源电压较大,导致正的保持误差。当输入信号更接近负电源时,情况正好相反。总而言之,在实践中这两种效应很少会具有相同的量级。

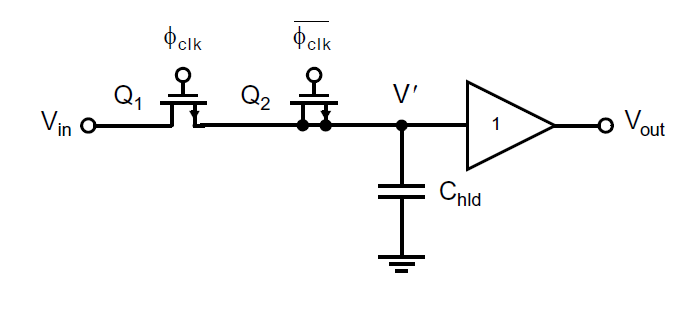

另一种最小化时钟馈通错误的修改是添加一个虚拟开关,如下图所示[McCreary, 1975]。这种技术背后的理论是如果\(Q_2\)的宽度正好是\(Q_1\)的一半,并且如果时钟波形很快,那么电荷就可以被抵消。在在实践中,很少可能有时钟波形变化速度足够快,使理想的宽度比正好是二分之一。

当理想的比例不是二分之一时,很难使宽度比例等于完美取消所需的最佳比例。但是,当时钟波形较快时,这种技术通常可以将保持错误缩小到无虚拟开关的约五分之一。然而,要做到这一点,\(Q_2\)的时钟必须略微落后于\(Q_1\),这种时钟布置保证了\(Q_2\)的抵消电荷无法在\(Q_1\)仍然打开时逃脱。

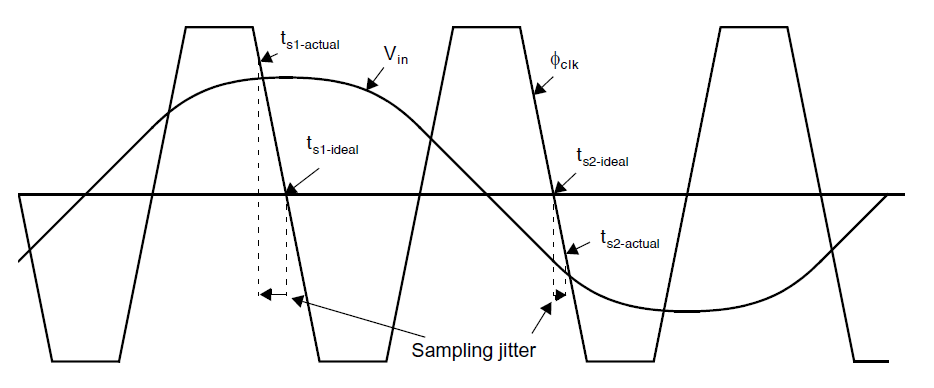

最开始介绍的简单采样保持电路的另一个误差源是由有限斜率的时钟波形引起的。要了解这一误差源,考虑波形\(V_{in}\)和\(\phi_{clk}\)。假设理想采样时间定义为\(\phi_{clk}\)的负向过零点,真正的采样时间是当采样时钟电压高于输入电压一个晶体管阈值电压降时。换而言之,晶体管\(Q_1\)在\(\phi_{clk}\)比\(V_{in}\)高一个\(V_{tn}\)时关断,如下图所示。因此,当\(V_{in}\)为高时,真实采样时间早于理想采样时间,而当\(V_{in}\)低于\(0 V\)时,则真正的采样时间晚于理想采样时间。

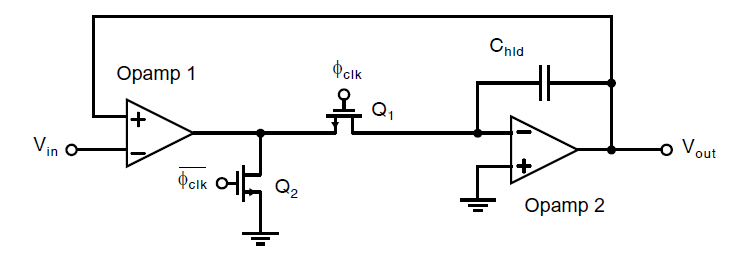

一个更精细的采样保持电路是在反馈环路中包含运算放大器,如下图所示。当时钟\(\phi_{clk}\)为高时,整个电路的响应类似于单位增益反馈配置中的运算放大器。当\(\phi_{clk}\)变为低电平时,此时的输入电压存储在\(C_{hld}\)上,类似于简单的采样和保持。通过在反馈环路中包含运算放大器,采样保持的输入阻抗大大增加。这种结构的另一个优势是,即使输出端的单位增益缓冲器具有失调电压,该缓冲器引起的直流误差将除以输入运算放大器的增益(尽管输入运算放大器的输入失调将保持不变)。因此,可用非常简单的源极跟随器作为输出缓冲。

这个结构的一个缺点是,由于必要保证闭环时的环路稳定性,工作速度会显著下降。速度下降的另一个来源是,当处于保持模式时,运算放大器处于开环状态,因此其输出几乎可以肯定饱和在其中一个电源电压。当采样保持电路返回下一个跟踪模式时,运算放大器需要一些时间才能使输出电压回到正确的闭环值。通过添加另外两个晶体管,如下图所示,可以显著减少所需的摆动时间。在保持模式下,开关\(Q_2\)保持第一个运算放大器的输出接近电路进入跟踪模式时需要达到的电压。还应该注意的是,这个跟踪保持电路由于开关\(Q_1\)的电荷注入,仍然存在会错误,类似于之前的电路,同样也有由于有限的时钟上升和下降斜率导致的误差。

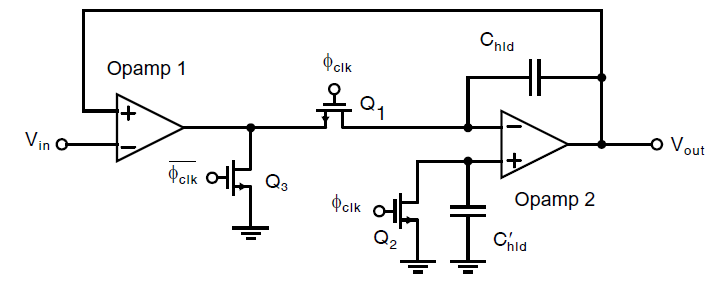

一个类似,但是改进版本的电路如下图所示[Stafford, 1974;Lim, 1991]。在这个电路中,保持电容不会接地,而是放置在第二个放大器的反馈路径中。此结构具有许多理想的功能。也许其中最重要的,假设第二个运算放大器具有较大的增益,则开关\(Q_1\)两侧的电压非常接近信号独立。因此,当\(Q_1\)关闭时,\(C_{hld}\)左侧仍然会有仍将有电荷注入,这将使运算放大器2的输出电压具有正保持误差,但此保持误差将只是一个直流偏移,并且会与信号无关。换言之,由于\(Q_1\)的电荷注入会导致一些直流偏移,但不会失真。此外,采样时间不会因为采样时钟波形的有限斜率而改变。

另一个优点是由于引入了\(Q_2\),该开关在保持模式将第一个放大器的输出接地(如果电源电压为单极性,则\(Q_2\)的源极应连接到中轨直流电压,运算放大器2的正极也应如此)。这种接地使第一个运算放大器的输出接近当 采样保持电路回到跟踪模式时,它必须变成的电压。这种方法大大加快了采样保持电路返回跟踪模式的时间。该开关也通过将信号路径接地,大大减小了采样保持电路在保持模式下的信号馈通。

这种电路的一个主要限制是,由于需要保证跟踪模式的稳定性,速度会降低。这种限制更加严重,因为现在在闭环阶段下,环路中有两个运算放大器以及采样开关\(Q_1\)的电阻。

下图展示了对上图电路的有趣修改,包括了一些额外的电路以最小化直流偏移 [Martin,1987;Nayebi, 1989]。其基本理念是将电荷注入\(C_{hld}\)与类似的电荷注入\(C_{hld}^{'}\)相匹配。由于这些电容在选择时具有相同尺寸,它们的电压变化将匹配,并且运算放大器的共模抑制将消除这些电压变化对输出电压的影响。

这个方式的主要局限性是由\(Q_1\)的左侧和\(Q_2\)底部的阻抗不匹配引起的二阶效应。通过在每个节点和接地之间加入小电容(\(0.5 pF\)至\(1 pF\)),可以最大限度地减少由于这种不匹配引起的误差。这些额外的电容有助于在时钟关断时使这些节点保持恒定电压,假设时钟波形很快。值得一提的是[Nayebi,1989] 的结构是全差分设计,对于许多采样保持应用来说是合理的选择。

浙公网安备 33010602011771号

浙公网安备 33010602011771号