模拟集成电路设计系列博客——9.2 电平转换器

模拟集成电路设计 9.2 电平转换器

电平转换器是集成电路设计中的一个重要部分,常用于芯片多电压域低功耗设计和I/O中。我们知道在集成电路中,I/O电压与Core电压常常处于两个不同的电压域,因此我们需要使用电平转换器(level shifter)来将I/O电压降低到Core电压,或者将Core电压抬升到I/O电压。多电压域是低功耗设计中的常见手段,对于一些工作速度与性能相对较低的电路,可以将其放置在相对较低的工作电压下,而对速度与性能要求高的电路则放置在较高的工作电压下。当涉及跨电压域的信号传输时,电平转换器是重要的功能电路。

当在具有完全不同电源轨的电源域之间驱动信号时,对电平转换器的需求是显而易见的。将信号从\(1V\)域驱动到 \(5V\)域是一个问题,\(1V\)的摆幅甚至可能达不到\(5V\)域中的阈值(这种情况下我们需要特殊的DC-DC电路,例如开关电源电路,如Buck-Boost型电路)。但是当今芯片中的内部电压紧密聚集在\(1V\)附近。我们为什么需要信号从0.9V域到1.2V域的电平转换器?

一个基本原因是,驱动\(1.2V\)栅极的\(0.9V\)信号将同时打开NMOS和PMOS网络,可能会使得电源对地导通,导致很大的电流。

此外,标准单元库的特点是输入需要干净、快速,轨到轨,这样运行效果最佳。不满足此要求可能会导致信号在一个域的驱动单元到另一个电压域中的接收器之间表现出显著的上升或下降时间衰减。这反过来又会导致时序不收敛。

最好的解决方案是确保每个域都获得所期望的完整的电压摆幅。为此,我们通过在域之间提供电平转换器来实现这一点。这种方法将任何电压摆幅和时序特性问题限制在电压域的边界,使得域内电路不受影响。这种清晰的接口使时序收敛和电路重用变得容易得多。

设计可在不同的电压之间提供有效的电压摆幅的电平转换器是一个模拟设计问题。出于模拟设计的原因,这些电路通常只设计为向一个方向转换:从更高的电压到较低的电压,或从较低的电压到较高的电压。对于静态电压调节,电平转换器的这种限制不是问题。但是对于其他形式的多电压,其中电源电压在运行过程中会发生变化,它确实带来了挑战。设计人员必须对设计进行架构和分区,以便电压域与相邻域具有明确的关系,例如“总是更高“、”总是更低“或”总是一样“。有了这个限制,就可以简单明了的使用适当的电平转换组件实现接口。

设计可以在两个方向上运行的接口可能从系统视角看起来很有吸引力,但需要非标准的实现组件和工具。

从表面上看,简单地从更高电压轨上的输出缓冲器过驱动CMOS输入似乎不是问题——不存在闩锁或击穿问题,与普通CMOS逻辑高电平或低电平开关电平相比,仅仅是“更好”、更快的边沿。

然而,为了安全的时序收敛,确实需要一些专门为此目的而专门涉及的单元。如果库中没有提供专门的高电平到低电平转换单元,则必须重新表征整个库,以便进行准确的静态时序分析。每个栅极都必须针对任意输入电压摆幅进行表征。

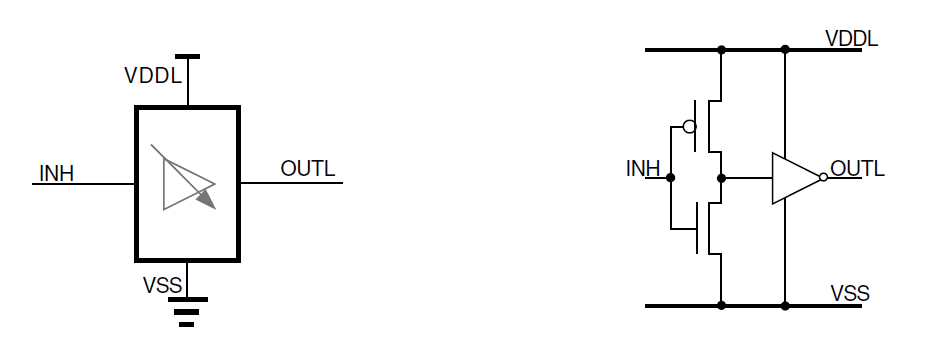

如下图所示,从高电平到低电平的电平转换器非常简单,基本上是两个串联反相器。我们观察到只需要一个电源轨,即一个更低的目标电压轨。从高到低电平转换器仅引入一个缓冲器的延迟,所以它对时序的影响很小。

将逻辑信号从低电源轨驱动到高电压轨上的单元是一个更关键的问题。欠驱动信号会降低接收输入端的上升和下降时间。这反过来又会导致更高的开关电流和更低的噪声容限。较慢的转换时间意味着信号在\(V_T\)附近花费的时间更长,导致短路电流的持续时间超过必要的时间。

对于时钟树缓冲器来说,这一点尤为重要。时钟树缓冲始终是一个挑战,电压区域边界上上升和下降时间的任何下降都会增加时钟偏移。使用专门设计的电平转换器单元可以解决这个问题。它们为更高电压域提供快速的全轨信号。可以使用设计工具对它们进行正确建模,以实现准确的计时。

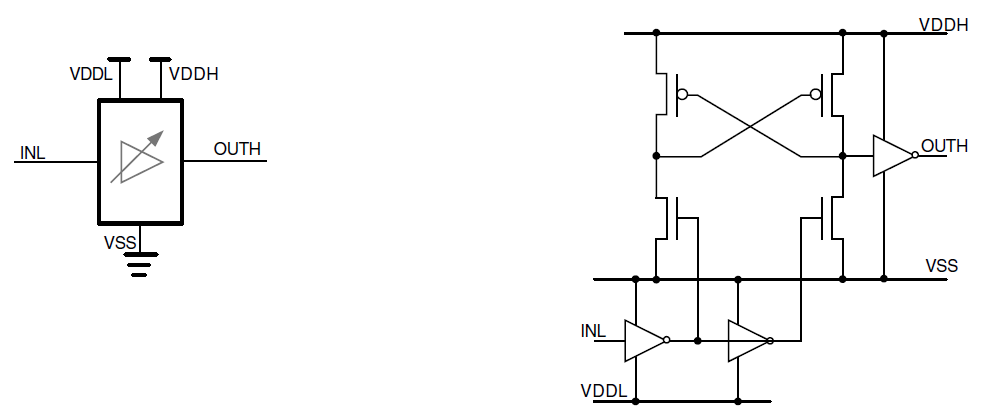

低到高转换器有许多设计方案,下图展示了一种简单直接的设计。此设计采用低电压信号的缓冲和反相形式,并利用它来驱动在较高电压下运行的交叉耦合晶体管结构。

这种“升档”电平转换器需要两个电源轨,并且通常共用一个地。但阱结构不能连接在一起,但必须独立地与电源相关联。

这些专用的低电平到高电平电平转换单元在扩展的电压范围上进行特征参数提取,从而与高压侧和低压侧的工作点匹配。这样可以精确地分析不同电压和操作条件。与从高电平到低电平转换器的简单的缓冲器相比,低电平到高电平转换器引入了显著的延迟。在时序关键模块之间接口很宽的情况下,例如,在不同电压的 CPU 和缓存之间,设计人员必须考虑接口延迟和任何跨电压边界的物理布线约束。

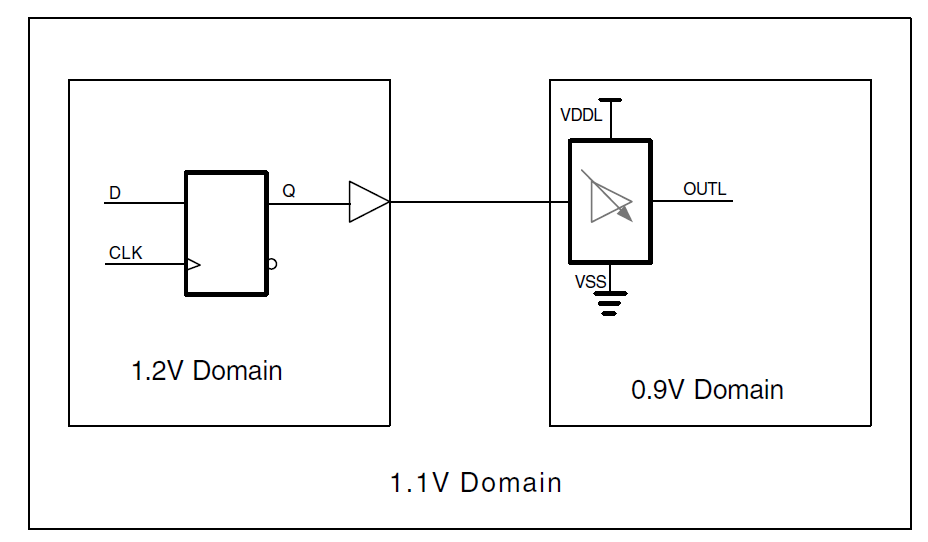

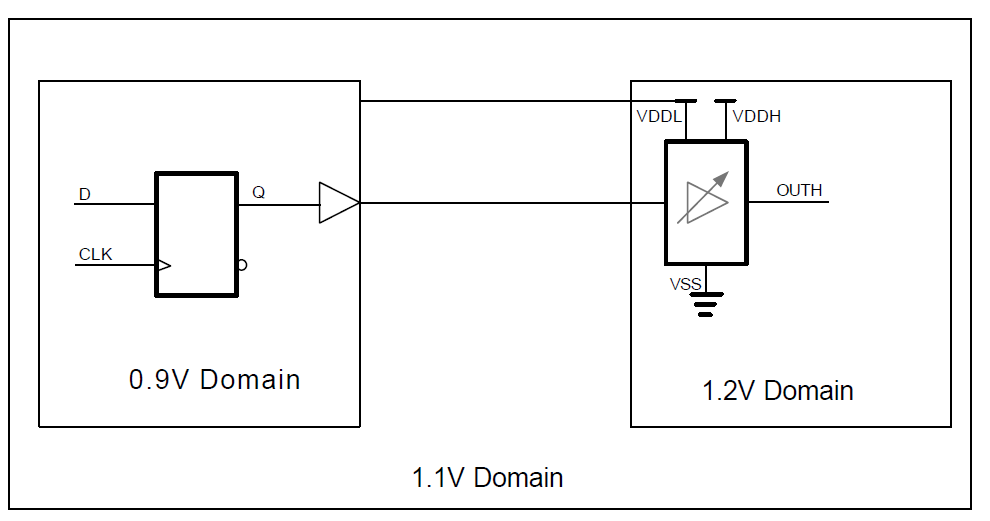

多电压域设计对单元布局提出了重大挑战。下图展示了嵌入在第三个电压域中的两个电压域的示例。

由于它使用来自较低电压域的电压轨,因此高低电平转换器通常放置在较低电压域中。如果\(1.2V\)域和\(0.9V\)域之间的距离足够小,并且库具有足够强的缓冲器,则驱动缓冲器可以放置在\(1.2V\)域中。不需要额外的缓冲。在\(1.1V\)域中添加额外的缓冲器显然存在问题:缓冲器使用什么电源?

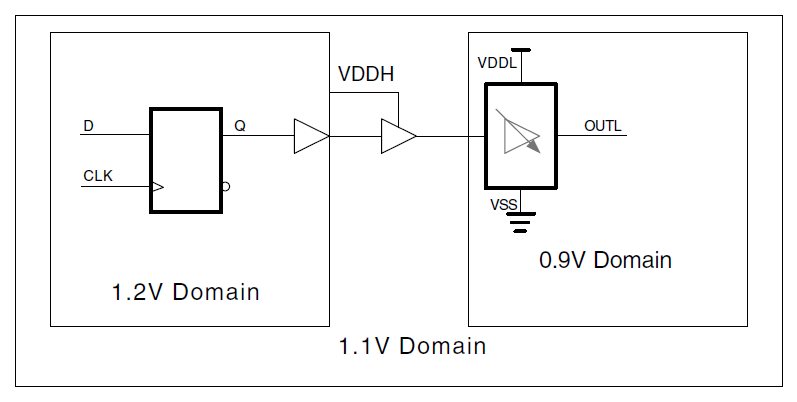

下图显示了一种可能的解决方案。此处,缓冲器使用\(1.2V\)域的电源轨。但这意味着\(1.2V\)电源轨必须在\(1.1V\)域中布线(可能作为信号线)。这种复杂的电源布线是实现多电压设计自动化的关键挑战之一。

下图显示了信号从\(0.9V\)域进入\(1.2V\)域的情况。在这种情况下,无论电平转换器放置在何处,电源布线都将是一个挑战。由于转换器需要两个电压轨,因此必须一个电压轨走线到另一个电压轨。由于输出驱动器需要比输入级更大的电流,因此我们将电平转换器置于\(1.2V\)域中。

与高到低电平转换器一样,如果\(1.2V\)域和 0.9V 域之间的距离足够小,并且库具有足够强的缓冲器,那么驱动缓冲器可以放置在\(0.9V\)域中,不需要额外的缓冲器。否则,需要在\(1.1V\)域中放置额外的缓冲器,从而导致上面提到的电源布线问题。

我们讨论完了多电压域设计中的电平转换器使用问题,接下来我们看看在I/O设计中的电平转换器结构。显然相比Core内的多电压域,I/O电压与Core电压之间的压差更大,以\(40nm\)工艺的典型值为例,Core电压只有\(1.2V\),而I/O电压达到了\(3.3V\)。

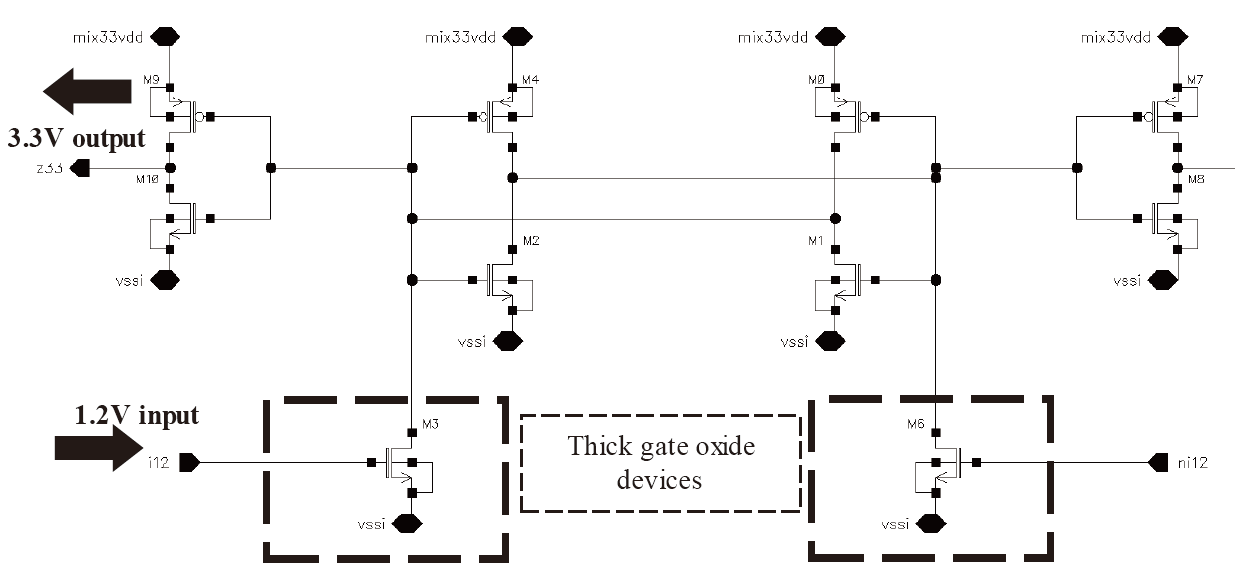

我们仍然可以使用之前介绍的交叉耦合晶体管的低到高电平转换器结构,但是其中的交叉耦合晶体管需要使用厚栅管来提高耐压能力,这种架构的主要缺点是切换期间下拉和上拉网络之间的激烈竞争,不可避免的导致电源到地通路的长时间存在。

我们需要分析如何进一步提升低到高电平转换器的性能,包括更低的输入电压/Core电压,更高的工作频率,更紧凑的面积等,以集成在I/O单元内。

如下图所示,一种新型的电平转换器被提出,以取代上面介绍的交叉耦合型结构[Radu-Valentin Petrica et.al, 2018]。

电路的工作原理非常简单,\(M_0\),\(M_1\),\(M_2\),\(M_4\)构成了两个首位相连的反相器,形成一个锁存器结构,并工作在\(3.3V\)的高电压域中,而厚栅低压管\(M_3\)和\(M_6\)漏极接地,栅极作为低压域的输入,当输入信号为高时,\(M_3\)接地,锁存器结构会使得内部节点电压被抬升或拉低,随后通过\(3.3V\)域中的反相器再进行输出。这种结构消除了原来交叉耦合结构中上下拉网络的竞争问题,利用锁存器结构的正反馈特性实现更快速的电平转换。

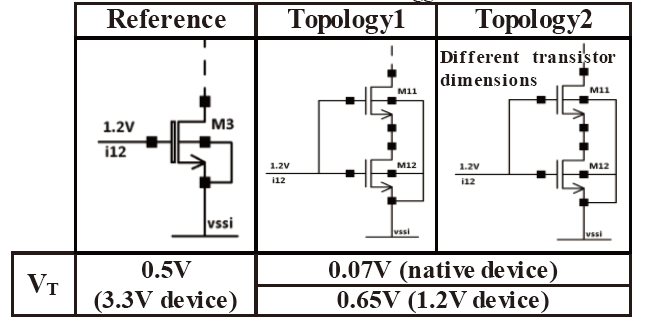

论文中还对低压输入管的拓扑进行了研究,如下表所示,相对于的\(3.3V\)器件的单管结构,拓扑1和拓扑2均使用\(1.2V\)器件和耗尽型器件(native MOS)堆叠而成,拓扑1和拓扑2的主要区别是晶体管几何尺寸不同。使用低阈值电压耗尽器件的目的是为了在\(1.2V\)输入的情况下仍然能够满足管子的饱和条件。

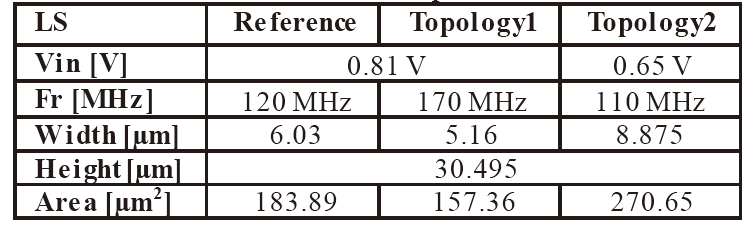

拓扑1的目标是为了在相同输入电压下减少总体的面积,拓扑2的目标是在相同工艺下通过改变器件尺寸实现允许更低的输入电压。下表总结了三种拓扑各自的面积,工作频率与输入电压:

参考资料:

"Low Power Methodology Manual For System-on-Chip Design", Michael Keating et. al.

浙公网安备 33010602011771号

浙公网安备 33010602011771号