模拟集成电路设计系列博客——9.1 比较器

模拟集成电路设计 9.1 比较器

比较器可能是继放大器之后第二常用的电路元件,比较器用于判断一个信号是否大于或小于零,或者比较一个信号是否大于另一个。如我们之前的章节所见,比较器在ADC中非常常用。在其他的应用中也经常出现比较器,例如数据传输,开关电源稳压器等等。

一种最简单的比较器实现方式是使用开环放大器,如下图所示:

这种方法的主要缺点是响应时间慢,因为运算放大器输出必须压摆大量输出电压并且建立速度太慢。但是,暂时忽略这种缓慢的响应时间,我们将首先研究其输入失调电压。

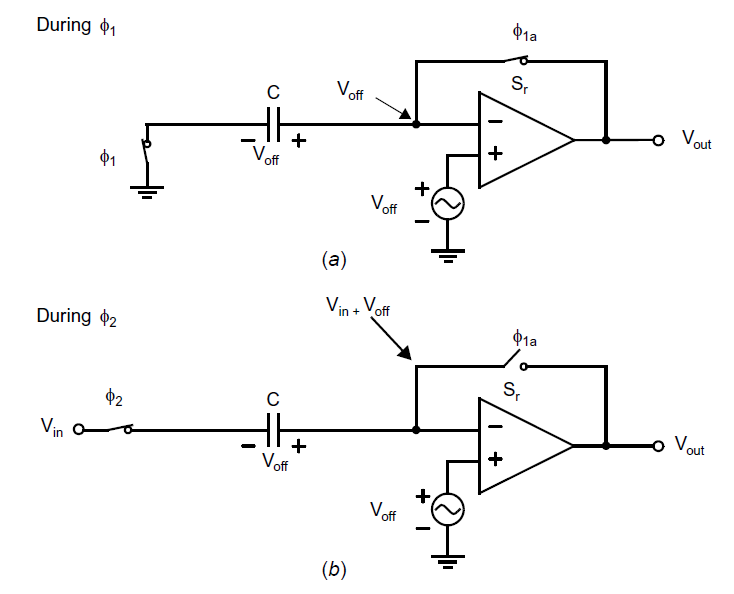

上图所示的简单运算放大器方法的分辨率受限于运算放大器的输入失调电压。对于典型的MOS工艺,该失调可能在\(2 mV\)至\(5 mV\)之间,这不足以满足许多应用的要求。一种替代架构,可以以远低于运算放大器输入偏移电压的精度分辨信号的电路如下图所示[McCreary,1975; Yee, 1978]:

虽然这个电路早年在模数转换器中很常用,但放到今天来说,已经并不可取。但是,它是一个简单的例子,可以用来说明许多重要的设计原则。上图中的电路工作过程如下:复位阶段\(\phi_1\)期间,电容\(C\)的底板(即电容\(C\)的左侧)接地,顶板接运算放大器的反相输入。同时,运算放大器的输出也通过闭合开关\(S_r\)连接到运算放大器的反相输入。假设运算放大器是理想的,这种连接使电容充电至零伏。接下来,在比较过程中,复位开关断开,电容器底板接入输入电压。运算放大器现在处于开环配置。如果输入信号大于零,则运算放大器的输出摆幅至较大的负电压。如果输入信号小于零,则运算放大器的输出摆幅至较大的正电压。这两种情况很容易分辨,并且可以使用简单的数字锁存器存储比较结果。且失调电压也可以得到抵消。

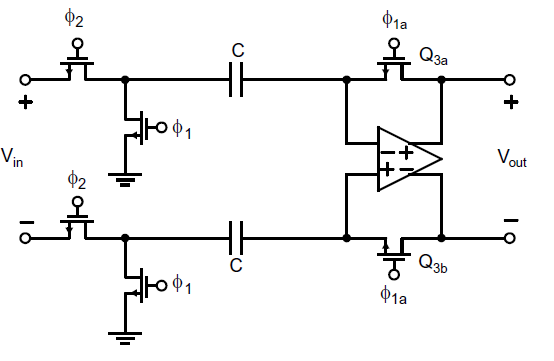

此外为了减小开关时钟馈通和电荷注入带来的影响,在现代电路中一般会采用全差分设计方式,上图中电路的全差分形式如下图所示:

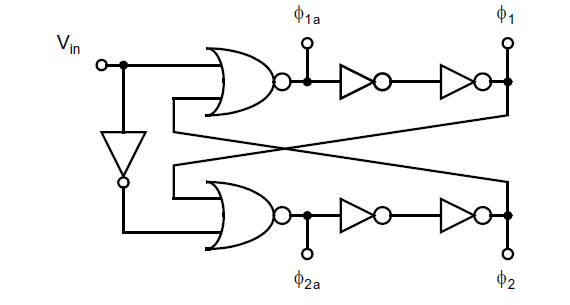

通过设计产生的时钟,使电荷注入信号独立也是一种手段,在上述电路中,通过使\(\phi_{1a}\)超前于\(\phi_1\)可以消除一定的电荷注入带来的影响,可以通过下图所示的时钟产生电路实现功能。

当人们考虑非理想运算放大器时,上述方法的局限性就变得明显了,这些运算放大器具有有限的增益,并要求补偿在复位阶段保持稳定。

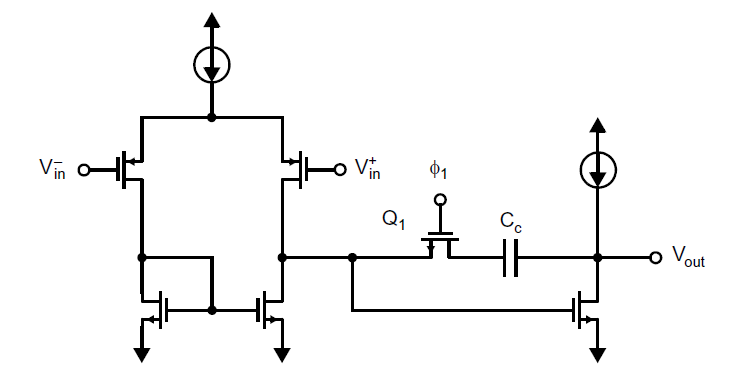

加快比较速度的一种可能性是断开比较阶段的补偿电容。例如,一个简化的运算放大器原理图如下图所示。在此运算放大器中,晶体管\(Q_1\)用于在复位阶段时导通以实现超前补偿,在比较阶段,\(Q_1\)关断,断开补偿电容\(C_c\),从而大大加快了该阶段的运算放大器速度。用这种技术,可以比使用之前的例子快十到五十倍的时钟频率,速度可能高达 \(25\) 或 \(50 kHz\)。如果这个速度足够,那么可以采用这个方法。但不幸的是,这个速度通常仍然是不够的,因此有必要采用后续介绍的其他方法。

为了获得好的分辨率,可能会需要将多级放大器进行级联,这会进一步放慢整体的速度。

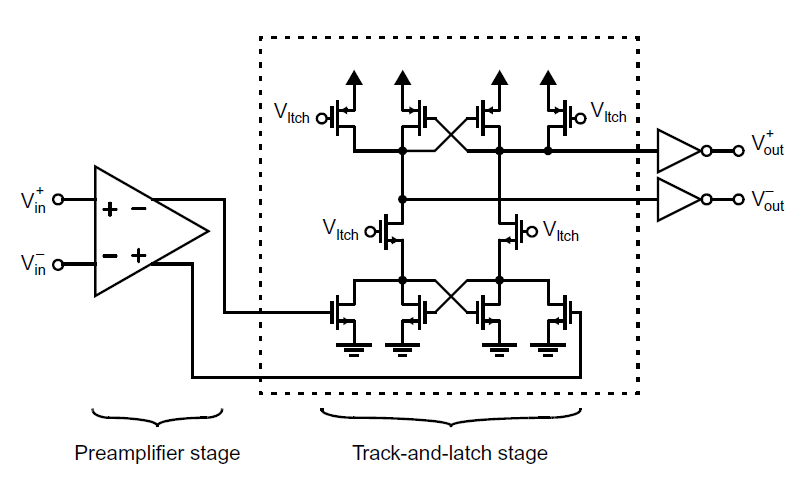

现代高速比较器通常具有一到两级预放大,然后是跟踪锁存级,如下图 [Yukawa, 1985]所示,这是一个CMOS实现的简化形式。这种架构背后的基本原理如下:预放大器用于获得更高的分辨率。预放大器的输出,虽然大于比较器输入,仍远小于驱动数字电路所需的电压电平。这之后,跟踪锁存级在跟踪阶段进一步放大该信号,然后在锁存阶段,当正反馈开启时。正反馈将模拟信号重新生成为全量程数字信号。跟踪锁存级最大限度地减少了所需的增益级总数,即使需要良好的分辨率时,因此比刚才描述的多级放大器方法更快。

预放大器通常有一些增益,可能是2倍到10倍。预放大器增益通常不会大于 10,否则它的时间常数太大,速度有限,一般一个或两个简单的电阻负载的差分级通常就可以了。请注意,观察比较器输入时,跟踪锁存级的输入失调和噪声会因预放大器的增益而衰减。因此,假设预放大器增益适中,预放大器的噪声和失调,通常会限制比较器的噪声和失调,如果需要非常高的速度,但只需要中等分辨率,预放大器有时可能只是一个单位增益缓冲器。

完全消除预放大器不是好的做法,因为到驱动电路中的回冲效益将严重影响准确性。回冲表示当跟踪锁存级从跟踪模式变为锁存模式时,电荷转入或转出输入的现象。这种电荷转移是由打开正反馈电路中的晶体管所需的电荷引起的,以及必须去除的电荷才能关闭跟踪电路中的晶体管。没有预放大器或缓冲器,这种回冲将进入驱动电路并导致非常大的毛刺,尤其是在两个输入点看入时的阻抗并不完全匹配的情况下。

在高分辨率应用中,通常还包括电容耦合和复位开关,以消除输入失调电压和时钟馈通错误,类似于我们之前讨论过的放大器比较器中的方法。

对于比较器来说,一个非常重要的考虑因素是确保不会有记忆的内容从一个判决周期转移到下一个。回想一下,当比较器在一个方向上切换时,它可能会倾向于停留在这个方向,称为滞后。为了消除滞后,可以在进入跟踪之前重置不同的阶段。这可以进入跟踪模式之前,通过开关将内部节点连接到其中一个电源或内部节点相互连接来实现。例如,上图所示的比较器当\(V_{ltch}\)信号为低电平时,锁存器内部节点复位到\(V_{DD}\)和地。这不仅消除了记忆问题,也将比较器设置为跳变点,从而加快了比较器解析小输入信号的运行速度。

跟踪锁存级电路有许多变种。上图所示的电路仅考虑简单的因素,尽管它在许多应用已经足够了。

浙公网安备 33010602011771号

浙公网安备 33010602011771号