模拟集成电路设计系列博客——8.4.3 数控振荡器

8.4.3 数控振荡器

在之前的章节中,我们介绍了一种简单得基于LC振荡器得数控振荡器方式,通过开关控制谐振电路中的电容值实现数控频率方式。

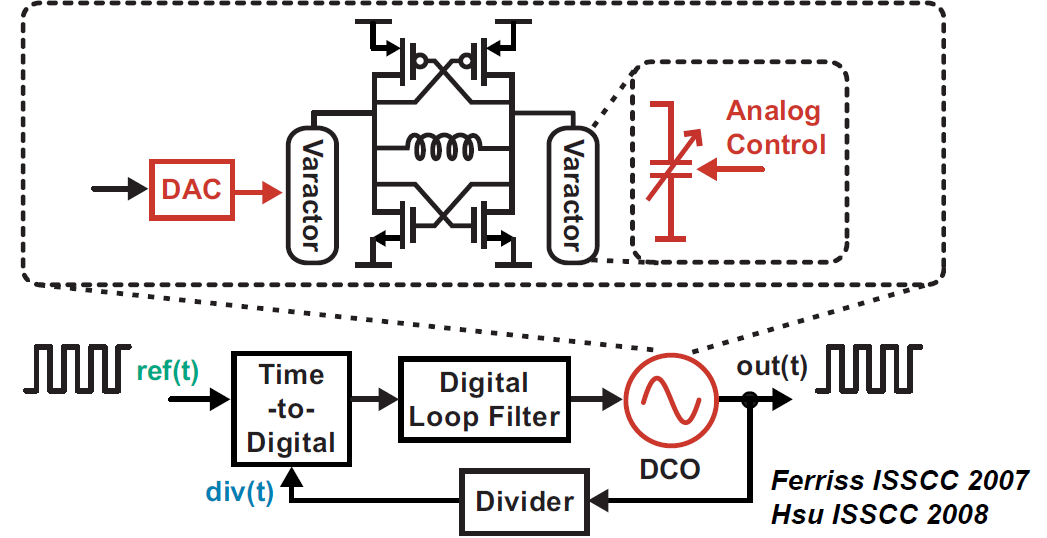

另一种更直接的利用模拟PLL中的LC振荡器VCO的方式是直接通过DAC的方式将数字码转换成模拟量,然后对电容施加控制。值得一提的是这种压控电容一般通过MOS Varactor来实现[P. Andreani et. al. JSSC, 2000]。这样做的好处是DCO可以完全复用模拟PLL中设计好的VCO结构。

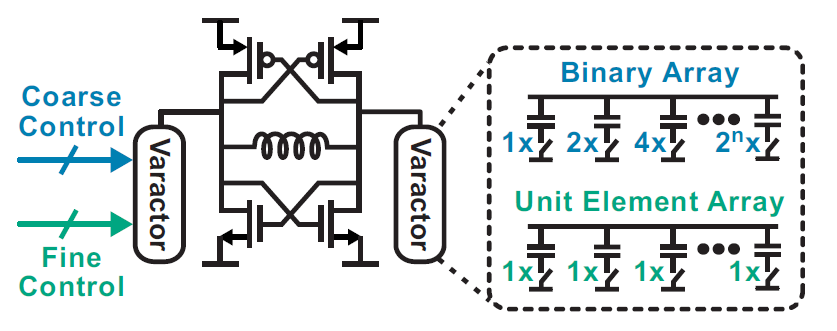

另一种相对开关直接控制接入电容的DCO的改进方式是采用类似DAC中的分段式架构,如下图所示,具体来说,通过粗控制码控制二进制权重的电容的接入,再通过细控制码控制单位电容的接入。二进制权重阵列在控制上简单,但缺少单调性,而单位电容阵列在控制上复杂,但具备单调性。在实际使用中,粗控制可以用于初始频率修调阶段,而后续的PLL反馈控制只调整细控制的部分。这样实现的DCO在频带范围和频率精度上可以实现一个好的权衡。

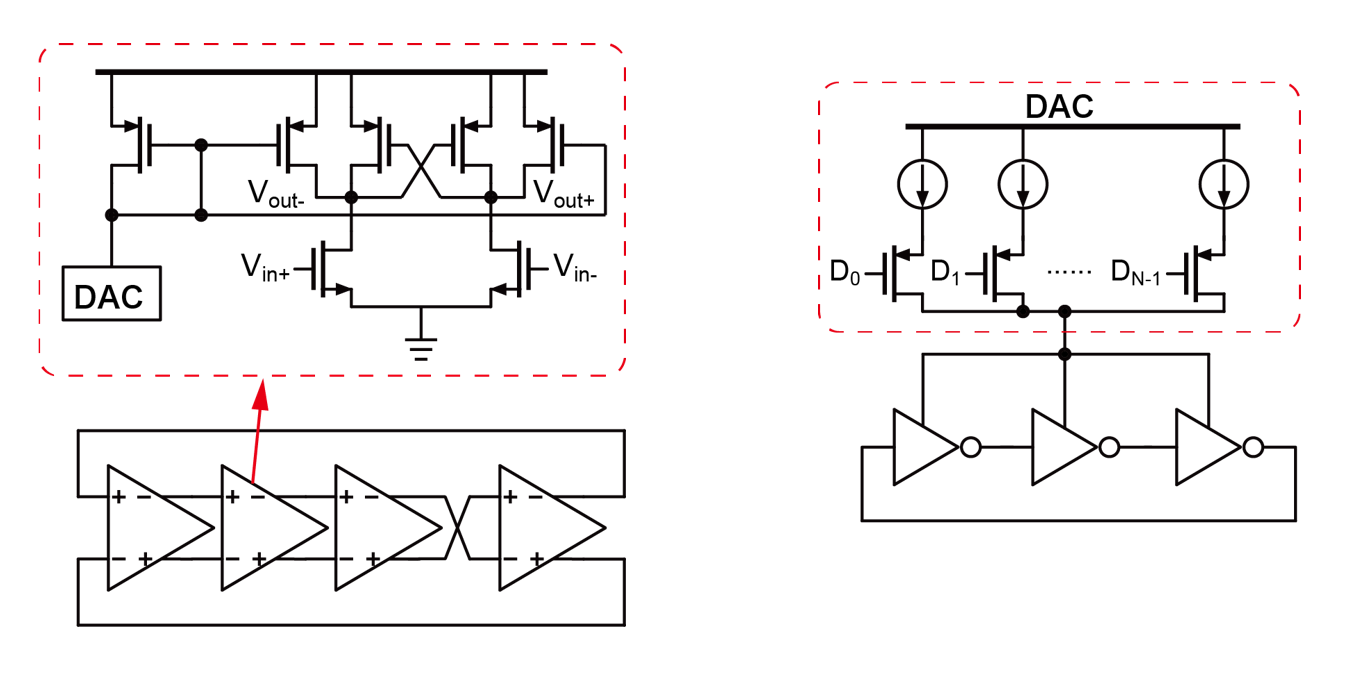

除了基于LC振荡器的DCO之外,基于环形振荡器的DCO也是一种重要的实现形式。一种直接的实现方式如下图所示,通过使用模拟PLL中环形振荡器VCO的基本结构,利用DAC产生控制电压从而调节单个延时单元的时间常数,进而控制总体的振荡频率;或者通过数字码控制电流源的接入数量,从而控制延时单元电流源大小,进而控制器时间常数和总体振荡频率。这样的好处是可以直接复用模拟PLL中较为成熟的环形振荡器VCO结构。但在先进工艺下,这种方式可能受到供电电压降低,以及PVT等因素的限制。

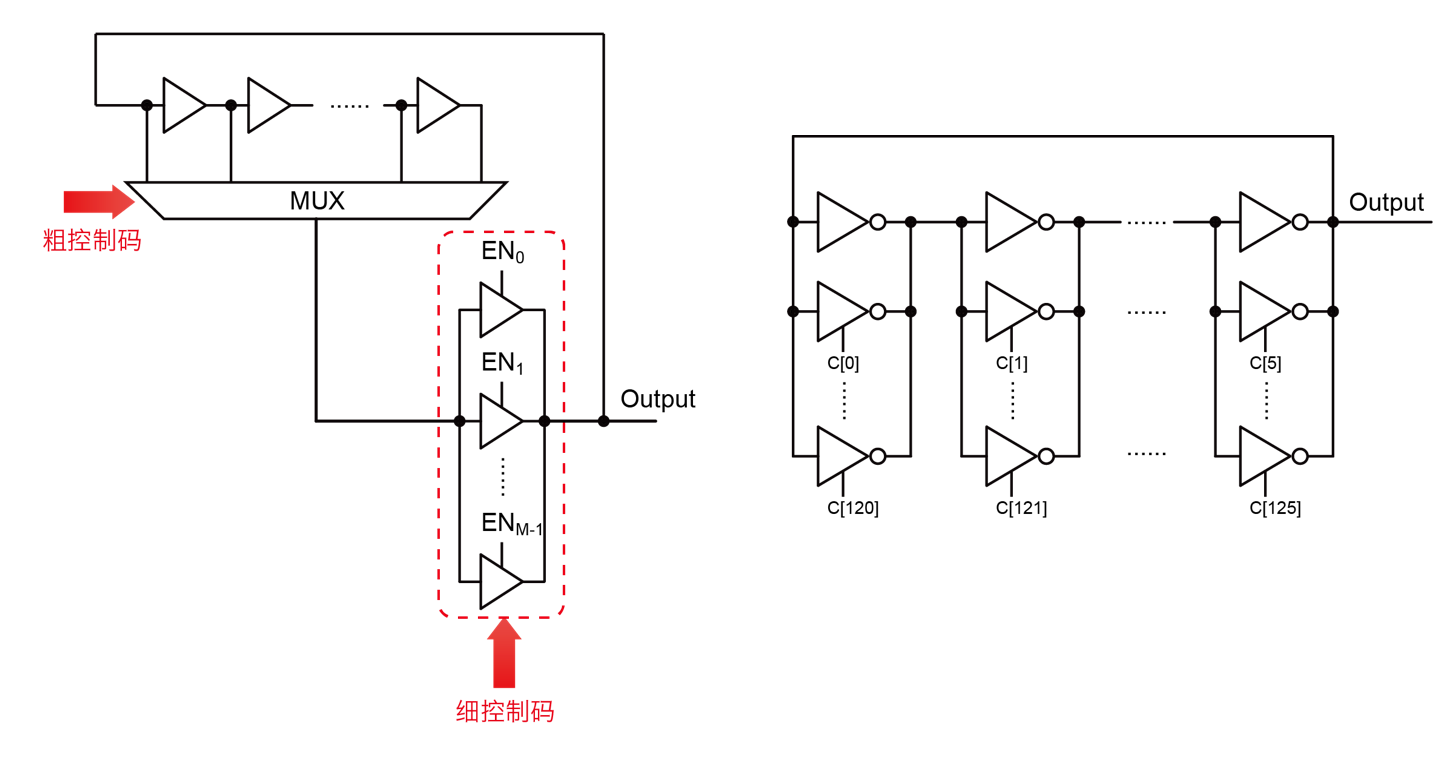

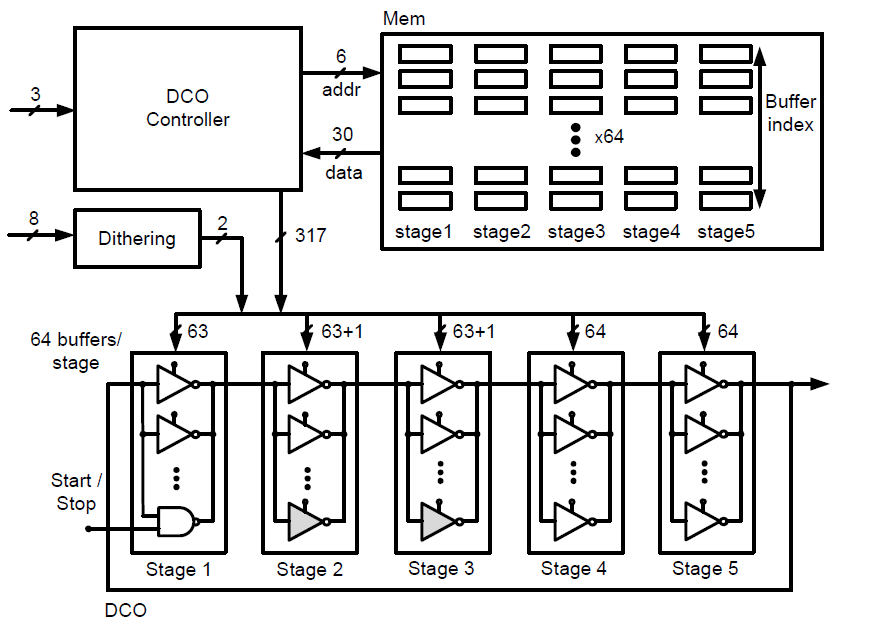

另一种方式是,直接控制接入延时单元的总数来调控总体的延时,进而调整振荡频率。如下图所示,由于\((8.2.1)\),我们知道振荡周期与延时单元数量成正比例。因此可以通过粗控制码直接选择串联的延时单元的数量。而通过并联多个延时单元,利用8.2.1章节中例题的小信号分析模型,负载电容并联\(C_{total}\)变为\(nC\),负载电阻\(R_{total}\)并联变为\(R/n\),但跨导变为\(nG_m\),其中\(n\)为并联延时单元的数量,因此在\(R_{total}C_{total}=RC\),并联后与单个延时单元相同的情况下,驱动能力增强了\(n\)倍,使得并联数量越大,驱动能力越强,延时越小。通过细粒控制码调节并联的接入数量,可以实现细粒度的延时调节。注意此处使用的延时单元均为三态缓冲器。另一种更直接的方式是直接将多个并联的延时单元结构进行串联,这样的好处是对于任一级的延时都可以进行调控,从而满足振荡器匹配时所需要的修调功能,但其所需要的控制码数量庞大,因此需要配合相对复杂的控制逻辑。

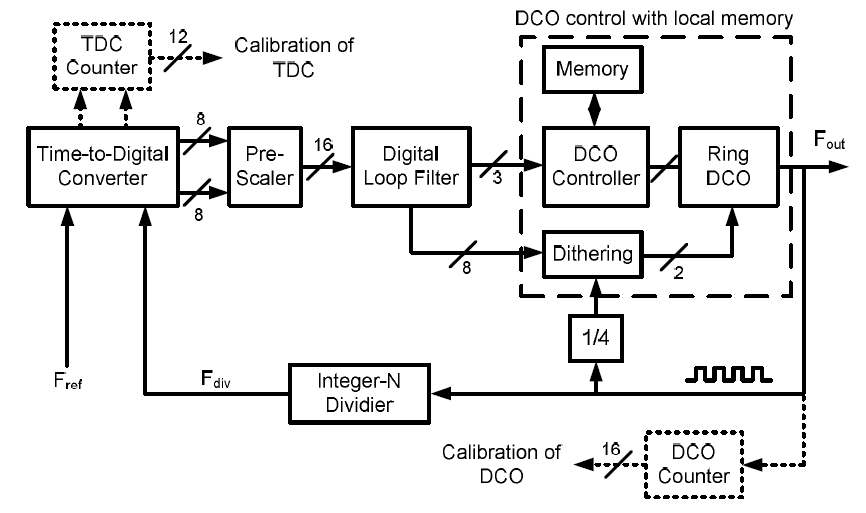

[Youngmin Park et. al., CICC, 2021]发表了一个65nm下完全使用数字单元综合的ADPLL。这个ADPLL是一个整数N PLL结构,在架构上与我们之前介绍的一样,主要是TDC,DLF,DCO,分频器等部件。但也存在一些额外的TDC和DCO校准电路。

在DCO的实现上,论文中的DCO主要使用了将并联延时单元进行串联组合的方案,共设计了五级,每级提供了64个三态缓冲器作为延时单元。由于论文采用的是全数字流程,因此版图上缓冲器被工具自动摆放,导致每级延时之间有较大的失配。为了能够细粒度的调控每级的延时,通过DCO控制器访问一个本地存储器,存储器中的存储单元数量与缓冲器数量一一对应。根据DLF的输出,并结合存储器中访存得到的结果,以及抖动电路产生的伪随机数(用于减小DCO的抖动噪声),来控制振荡器中每级缓冲器的开或关。如下图所示:

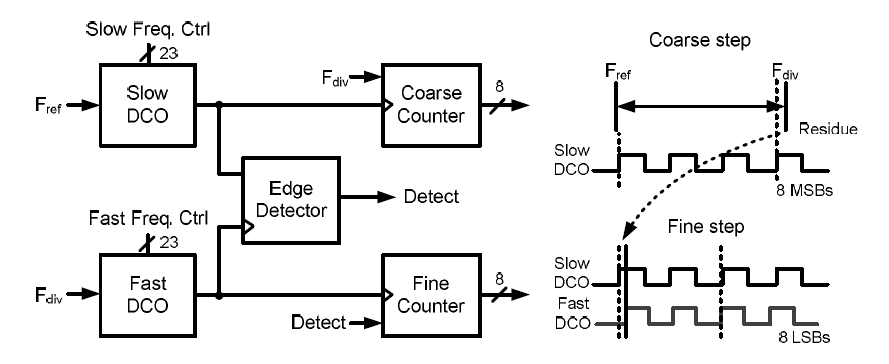

在TDC的实现上,论文中的架构采用了游标型TDC与基于振荡器型TDC的结合,实现一个基于DCO的游标型TDC。具体来说,论文使用了一个慢速DCO和一个快速DCO,通过慢速DCO以及粗计数器实现对相位差的低分辨率粗测量,而高分辨率的细粒度测量则利用了快速DCO与慢速DCO之间的频率差,如下图所示:

论文最终得到的ADPLL在65nm工艺下,可做到\(1.5-2.7GHz\)的输出频率范围,抖动的均方根控制在\(3.2ps\)。

参考资料:

"All-Digital Frequency Synthesizer In Deep-Submicron CMOS", Staszewski et. al.

浙公网安备 33010602011771号

浙公网安备 33010602011771号