模拟集成电路设计系列博客——8.4.2 时间-数字转换器

8.4.2 时间-数字转换器

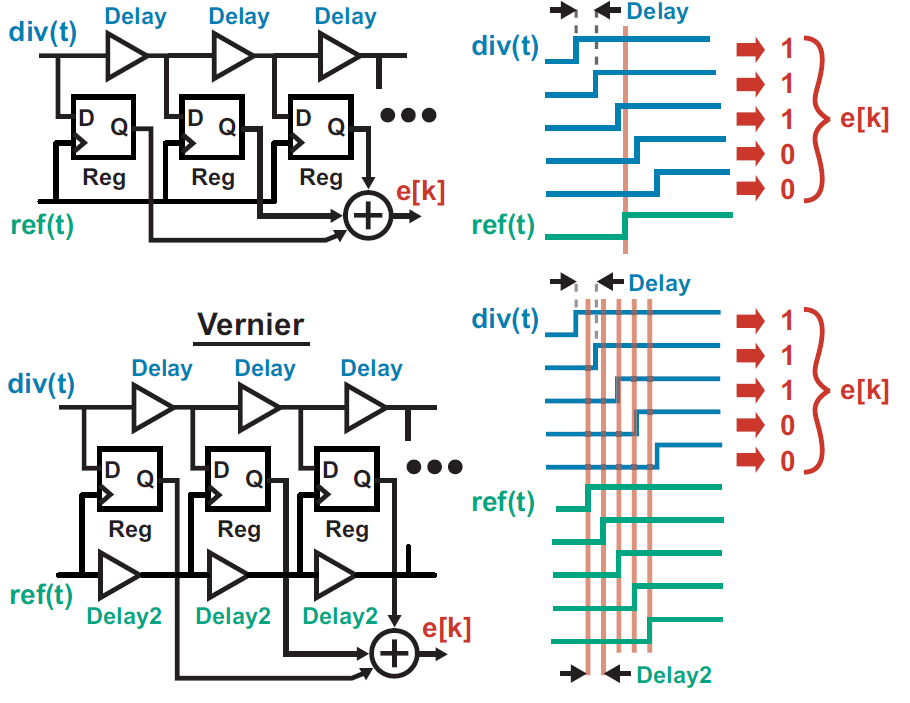

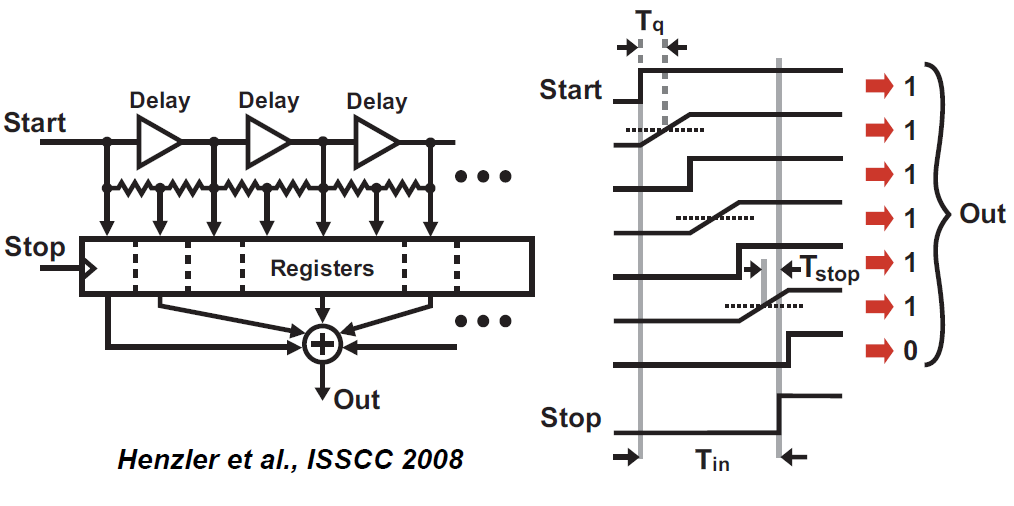

在上一节我们介绍了TDC的一种典型实现,即单延时链TDC,通过\(2^N\)的延迟单元和D触发器可以实现N bit的时间数字转换功能,但这种结构的分辨率受到延迟单元的最小延迟时间限制,即:

其中\(T\)为TDC的最大量程,\(\tau_{delay}\)为延时单元的时间常数。由于延时单元所能够实现的最小时间常数是有限的,因此这会使得这种最基础架构的TDC的分辨率受到限制。

游标型TDC在上述架构的基础上做出了改进以解决分辨率问题。具体来说,通过在参考信号\(ref(t)\)上也引入延时链,此时TDC的分辨率变为:

其中\(\tau_{delay1}\)为\(div(t)\)信号延时链的延时单元的时间常数,\(\tau_{delay2}\)为\(ref(t)\)信号延时链的延时单元的时间常数。通过调控上下两个延时链的延时单元的时间常数之差,可以在更大的范围内调控TDC的分辨率。这种方式类似于游标卡尺原理中通过更小的分度来实现高精度的测量,因此称为游标型TDC。如下图所示:

但相比单延时链的TDC架构,游标型TDC受到器件失配的影响会更大,且需要很大的面积来实现大的测量范围。

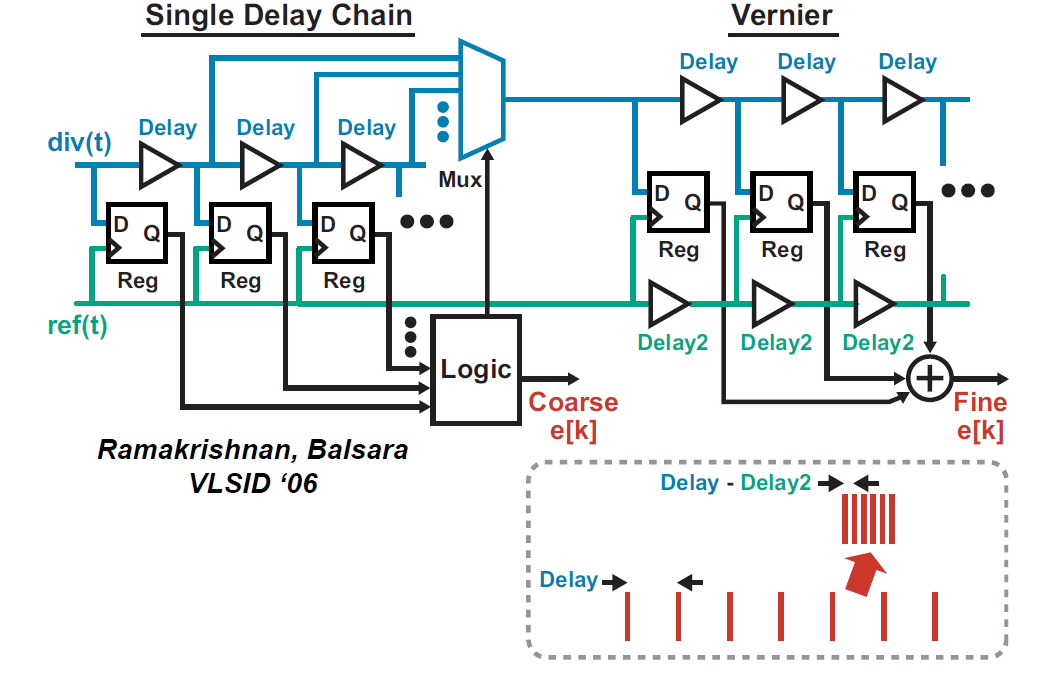

两步型TDC吸收了ADC设计中两步型ADC的设计思想,对于粗粒度的分辨率通过单延迟链TDC实现,而细粒度的分辨率通过游标型TDC来实现。如下图所示:

这样的架构降低了大测量范围时游标型TDC的面积消耗,通过更少的器件总数即可实现同等测量范围下与游标型TDC架构相同的分辨率。但需要对单延时链做出一定的改动,引入控制逻辑与多路选择器Mux来选择将哪一段信号送入游标型TDC中进行分辨。

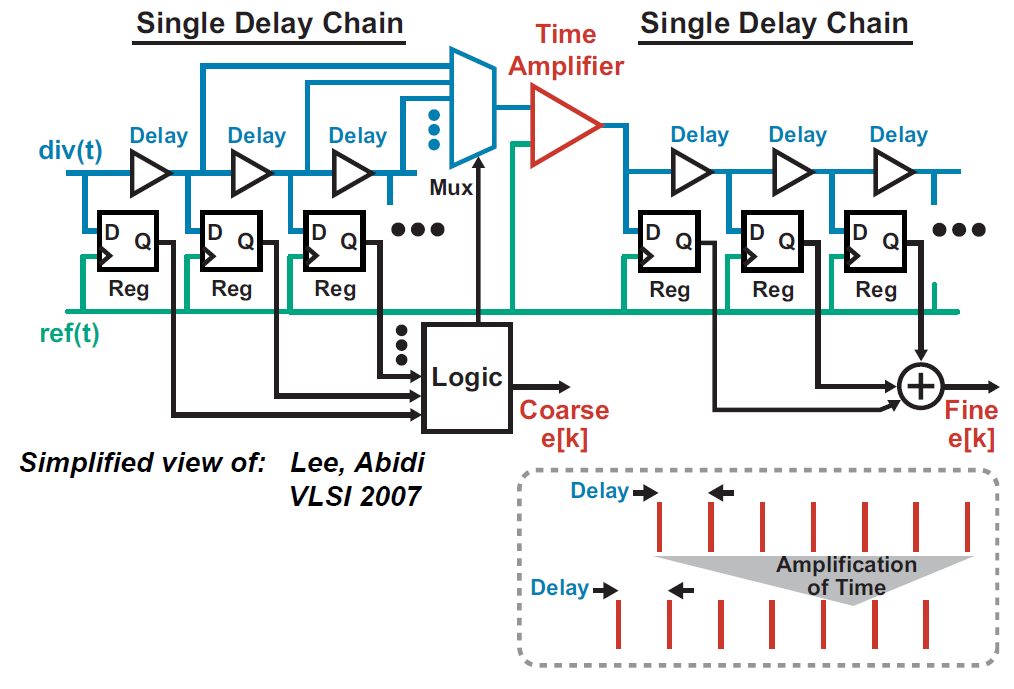

另一种方式是全部使用单延时链TDC,为了进一步提升分辨率,可以在两步型TDC中引入时间放大器,从而放大Mux输出的时间信号的范围。当两步型TDC的粗粒度和细粒度部分都只处理\(N/2\)bit时,总的延时单元数量被降低至\(2\times2^{N/2}\)。

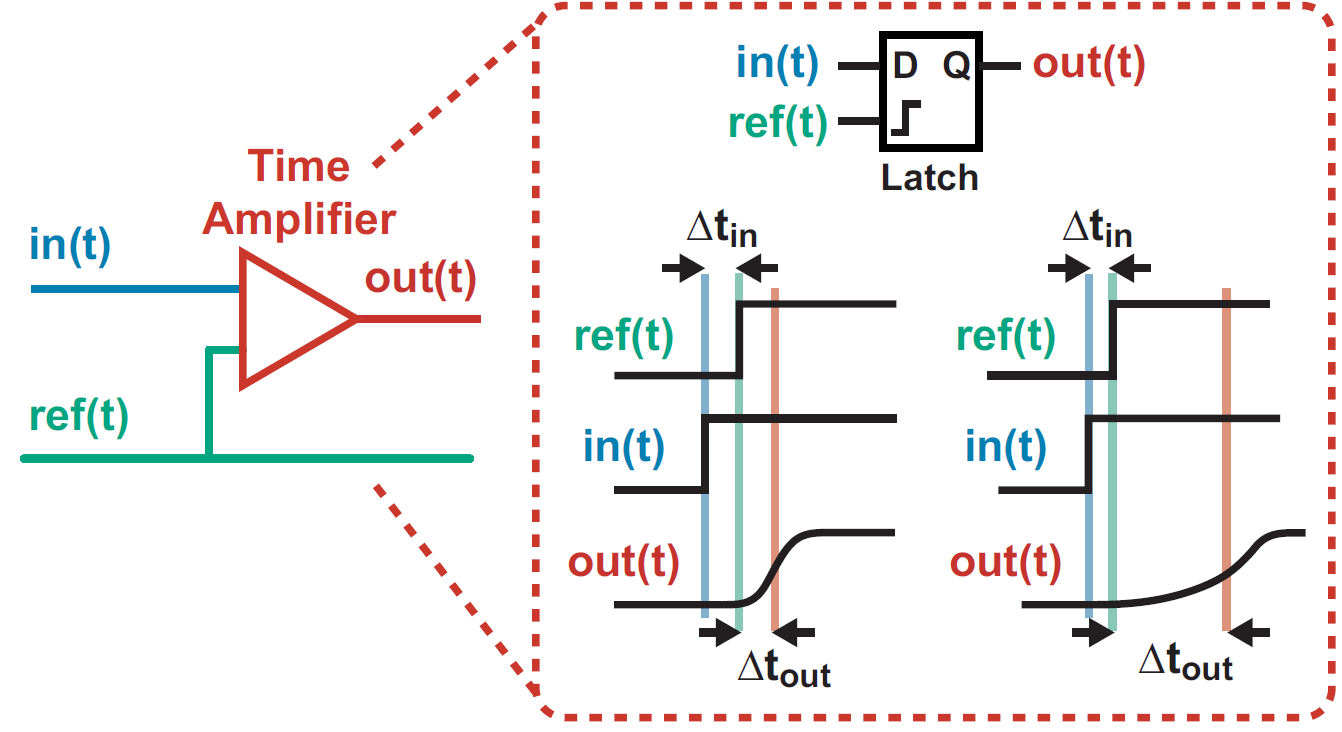

时间放大器的功能主要是放大Mux输出信号与\(ref(t)\)边沿的时间差,可以通过一个简单的锁存器结构来实现,如下图所示[Abas, et al., Electronic Letters, Nov 2002]:

但上述结构对时间放大器的线性度提出了挑战,如果锁存器的建立时间与输入信号的时间差之间不满足线性关系,则会影响TDC整体的线性度。

插值型TDC也是一种可以减少延时单元数量的同时提升分辨率的架构,类似于ADC中的插值型ADC架构,通过电阻/晶体管/二极管对延时单元进行二次插值。具体来说,如下图所示,在两个延时单元之间通过匹配的两个电阻,可以实现对基础分辨率的二插值,从而将分辨率提升一倍。寄存器对延时信号的边沿以及插值信号进行捕捉,从而实现时间数字转换功能。通过引入周期技术,这个架构可以实现更大的测量范围。

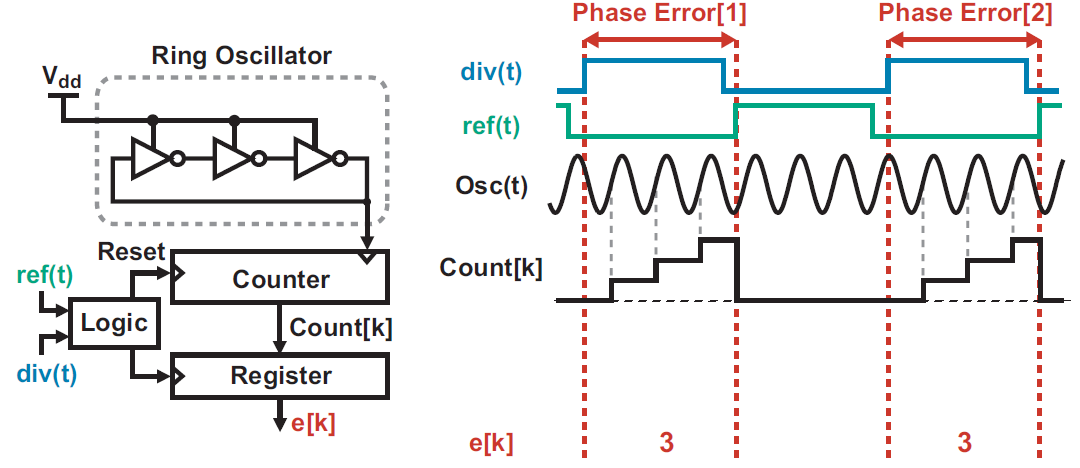

基于振荡器的TDC架构可以在紧凑的面积下实现非常大的测量范围。具体来说,环形振荡器为计数器提供周期信号,振荡器的周期决定了TDC的分辨率。在工作时,\(div(t)\)与\(ref(t)\)输入控制逻辑,\(div(t)\)的上升沿作为计数器的启动,\(ref(t)\)的上升沿控制计数器的复位。在此期间计数器根据振荡器的输入的周期信号进行计数,以计数结果作为信号相位差的数字表示。如下图所示:

由于这个结构不依赖延时链,仅仅需要一个环形振荡器和计数器就可以实现延时链的功能,因此在测量范围大,分辨率要求时可以大大减小面积需求。

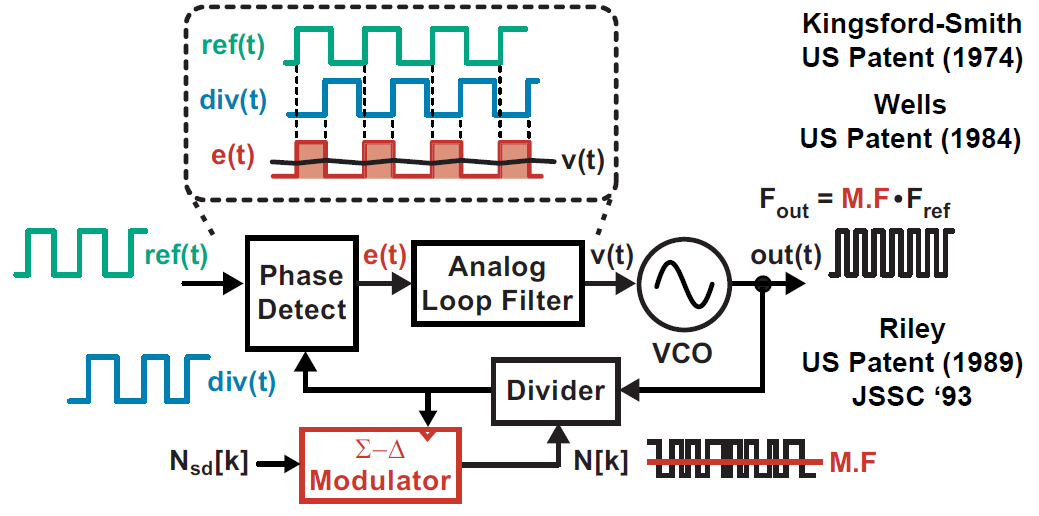

另外,值得一提的是,尽管之前我们介绍的PLL结构都是整数分频的结构(即所谓的整数N PLL,Integer-N PLL),但在现代电路需求中,有时需要更细粒度的倍频倍数,即所谓的小数倍频,此时可以使用\(\Delta \Sigma\)分数N PLL架构,其具体对整数N PLL的架构上主要的变动是通过在分频器处引入\(\Sigma \Delta\)调制器以实现更细粒度的分频功能,如下图所示。

参考资料:

"All-Digital Frequency Synthesizer In Deep-Submicron CMOS", Staszewski et. al.

浙公网安备 33010602011771号

浙公网安备 33010602011771号