模拟集成电路设计系列博客——8.4.1 全数字锁相环介绍

8.4.1 全数字锁相环介绍

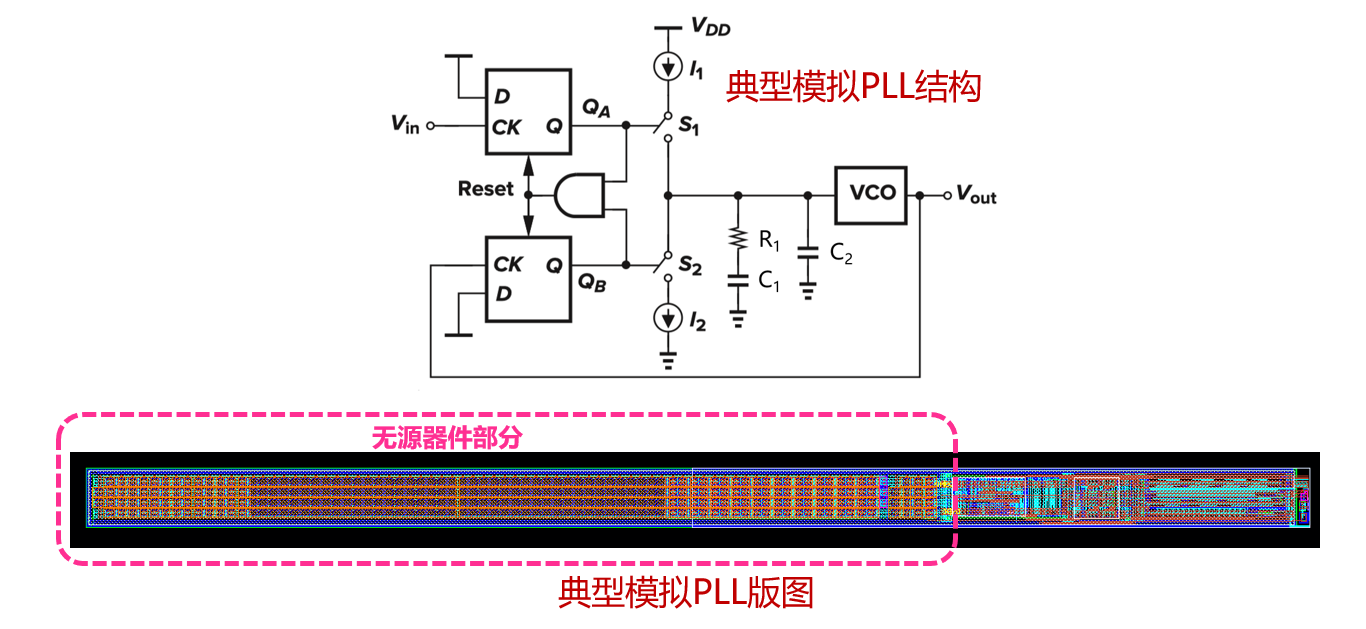

随着CMOS工艺的演进,数字电路的尺寸得到不断的微缩,工作电压不断的降低,这使得模拟PLL受到了许多挑战,如环路滤波器中无源器件尺寸庞大,即使在更先进的CMOS工艺下也无法缩小,如果改为片外器件又会引入额外噪声,并增加pad需求和PCB面积,如下图所示,一个典型的模拟PLL结构中(基于电荷泵的PLL可以被称为CPPLL),无源器件部分可以占到大约版图总面积的60%;当工艺特征尺寸降低,电源电压和晶体管阈值电压降低后,电荷泵的漏电和电流失配将导致抖动变大。

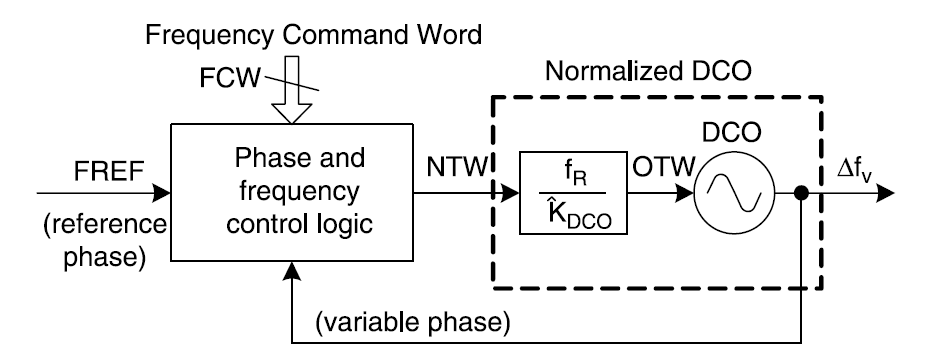

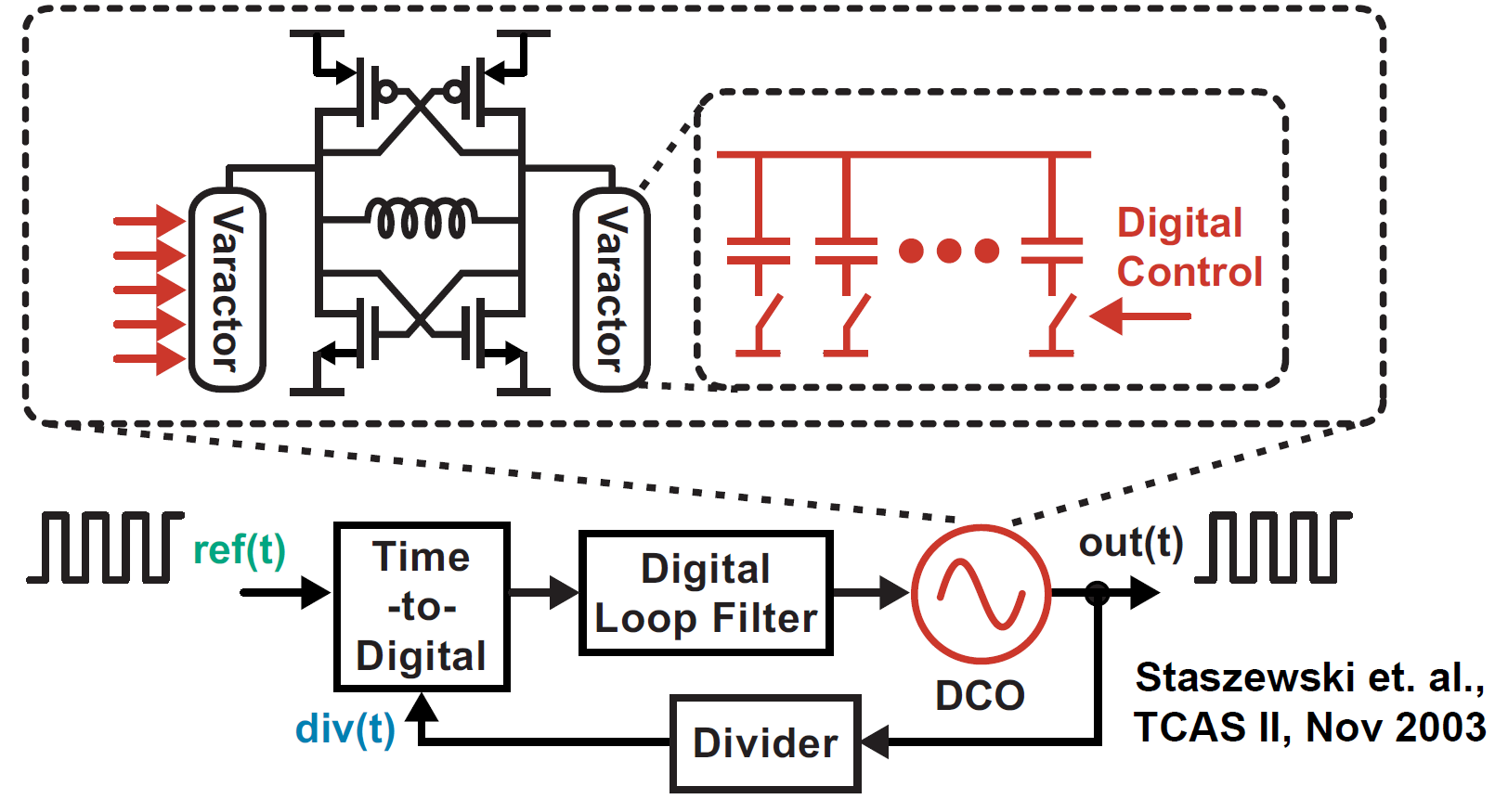

全数字PLL(ADPLL)是一种特殊的PLL,其所有的组件之间的接口均为数字信号,且从底层上依赖于数字设计与数字电路技术。其核心为数控振荡器(DCO),其故意避免模拟调谐电压控制。DCO类似于触发器,即数字电路的基石。其内部是模拟的,但模拟性质不会传播到其边界之外。这使得其环路控制电路可以在完全数字的方式下实现。如下图所示:

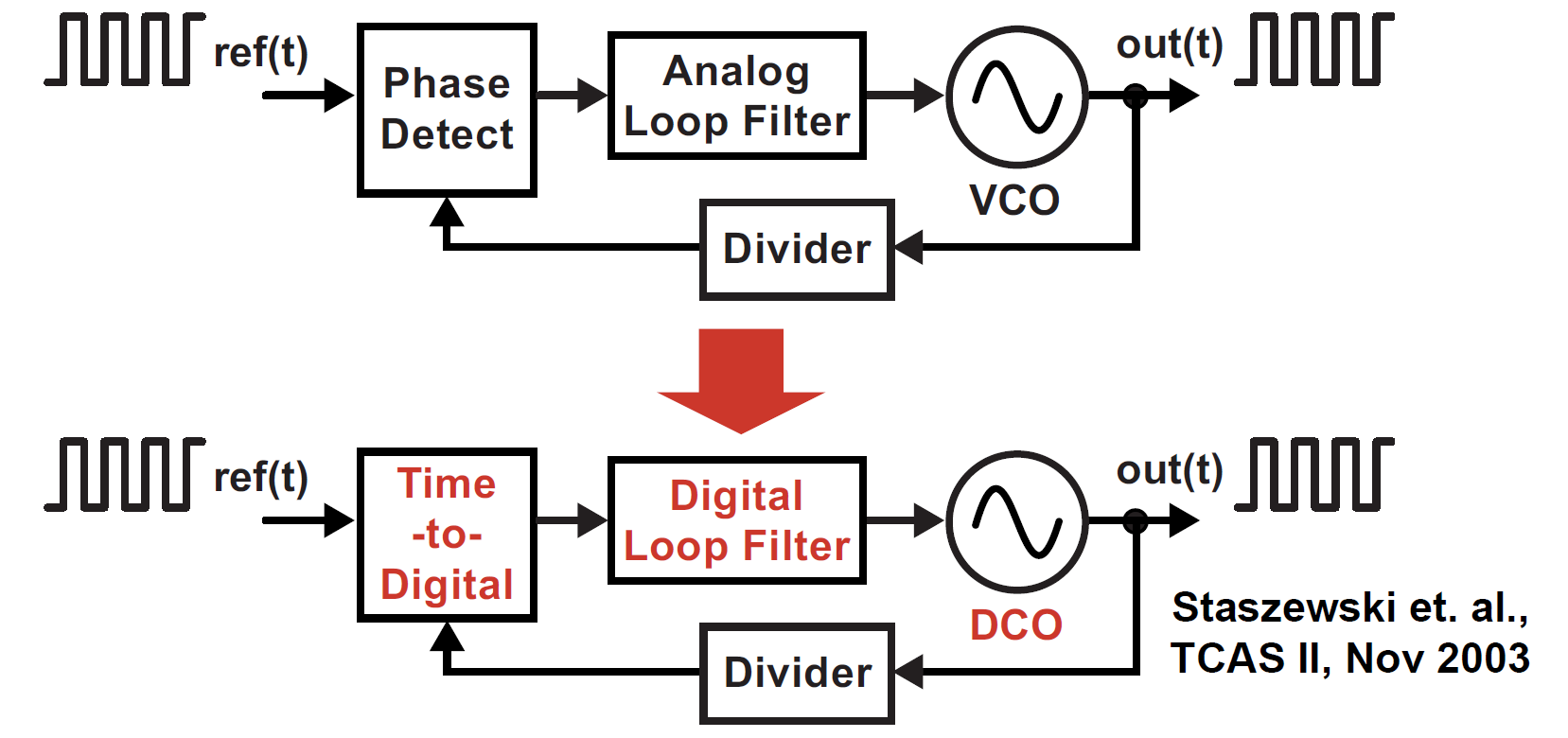

更细节的来说,ADPLL的结构与我们之前介绍的模拟PLL基本类似,鉴相器结构被时间数字转换器(TDC)所取代,模拟环路滤波器被数字环路滤波器DLF取代,压控振荡器VCO被数控振荡器DCO取代。与模拟PLL中各个部件起到的作用类似,TDC的作用是将参考输入时钟与分频器分频后的DCO输出的时钟之间的相位差以数字编码的方式表示出来。DLF对TDC的输出进行低通滤波以获得其数字表示的平均值,并将其作为控制信号输出给DCO。DCO收到DLF的数字控制信号,调整输出的频率。如下图所示:

相较于模拟PLL,数字PLL具备更紧凑的面积,对漏电不敏感的优势。并且随工艺缩放的能力更强。在ADPLL中,关键的设计挑战在于TDC和DCO,它们对于ADPLL的性能起到关键的影响。通过负反馈的原理,ADPLL同样可以做到和模拟PLL一样的输出信号相位跟踪输入信号相位,以及时钟倍频等功能。

我们首先介绍TDC,DLF和DCO三个组件的基本情况,其中TDC和DCO是ADPLL中的关键组件,我们将在后续章节中做详细的讨论。

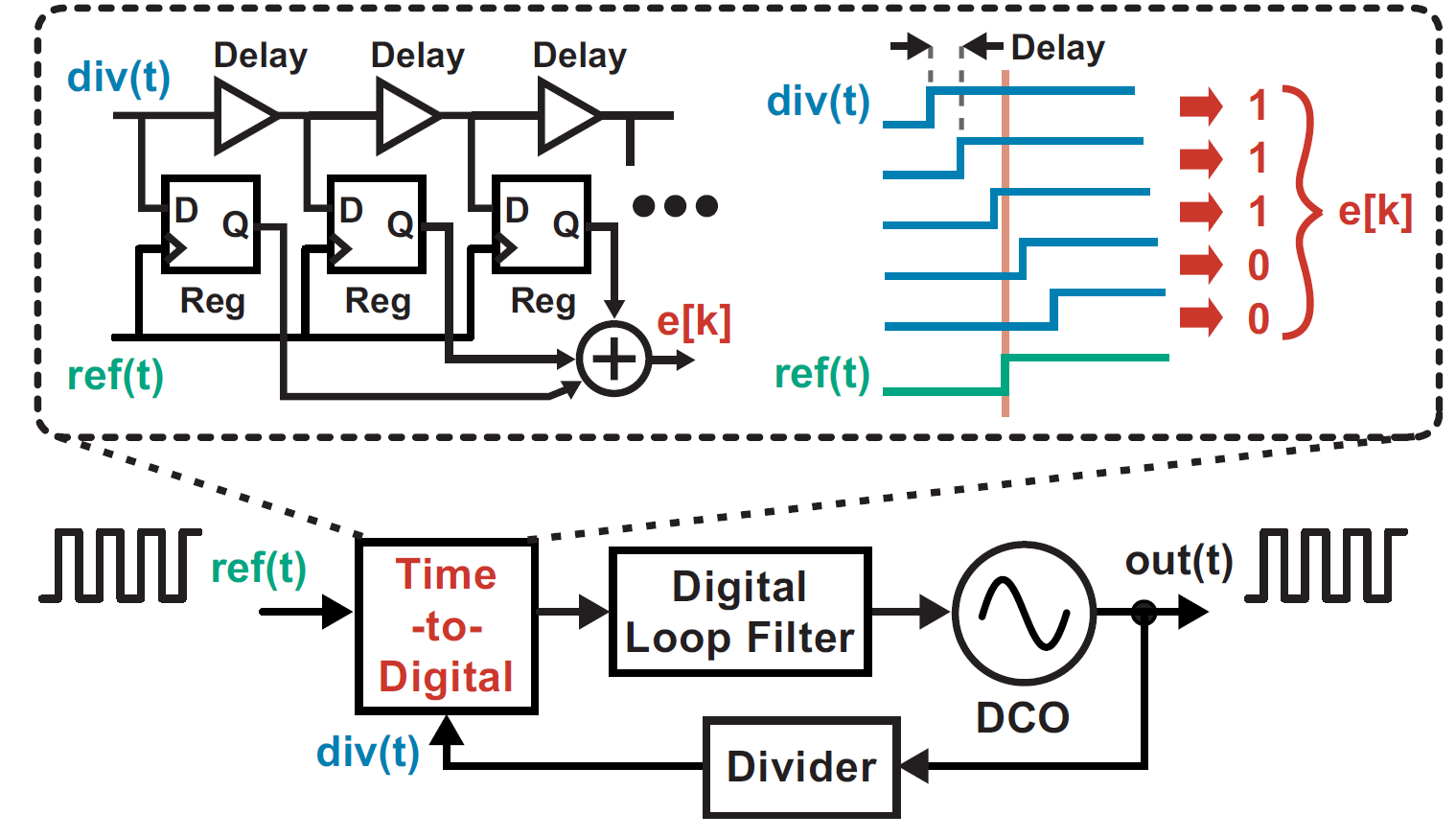

如之前所说,TDC的功能是是将参考输入时钟与分频器分频后的DCO输出的时钟之间的相位差以数字编码的方式表示出来,一种简单的实现方式是通过延迟链和D触发器实现功能,通过D触发器实现参考时钟信号\(ref(t)\)与延迟时钟信号\(div(t)\)的边沿比较,当\(div(t)\)的上升沿超前于\(ref(t)\)时,D触发器Q端会输出1,反之则输出零。这样就会获得一个温度计码表示的时间数字转换结果,进一步通过加法器可以获得二进制表示的结果。这个结构实际上类似于ADC中的Flash ADC结构。如下图所示:

在对TDC建模时,和ADC一样,TDC也会引入量化误差。对于输入的相位偏差\(\phi_e[k]\),通过缩放因子\(T/2\pi\)将其从相位转换到时域,随后叠加量化噪声\(t_q[k]\),最后通过TDC增益\(1/\Delta t_{del}\)放大之后得到转换结果\(e[k]\),因此:

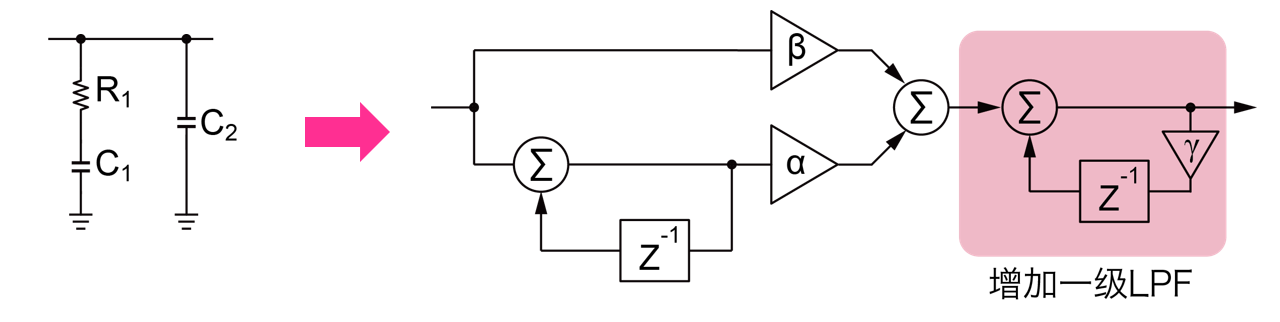

ADPLL允许DLF的设计完全采用数字滤波器的形式,如FIR,IIR等滤波器结构。可以直接将模拟PLL中使用环路滤波器设计为其数字等效,如下图所示:

我们之前分析过这个电路,其传输函数为:

其中\(\omega_z=1/R_1C_1\),\(\omega_p=(C_1+C_2)/R_1C_1C_2\)。对于电阻我们通过简单的线性增益级进行等效,对于电容我们通过积分级与增益级进行等效,因此我们可以获得等效的DLF传输函数为:

这个传输函数可以简单的通过乘法器,加法器,累加器等数字部件实现。

DCO以输入的数字码作为控制,调节其输出信号的频率与相位。一种简单的实现方案是在之前介绍过的VCO的LC振荡器的基础上进行修改,将数字码控制码作为开关的输入,通过开关控制接入电路的电容数量,从而调整接入电容的容值,从而修改其谐振频率:

一个典型的实现如下所示:

这样做的好处是复用模拟PLL的VCO结构,设计上相对简便,但存在着无源器件难以微缩的问题。因此上述方案只是在\(0.13\mu m\)工艺下提出,而更先进工艺的DCO是基于环形振荡器架构实现的。

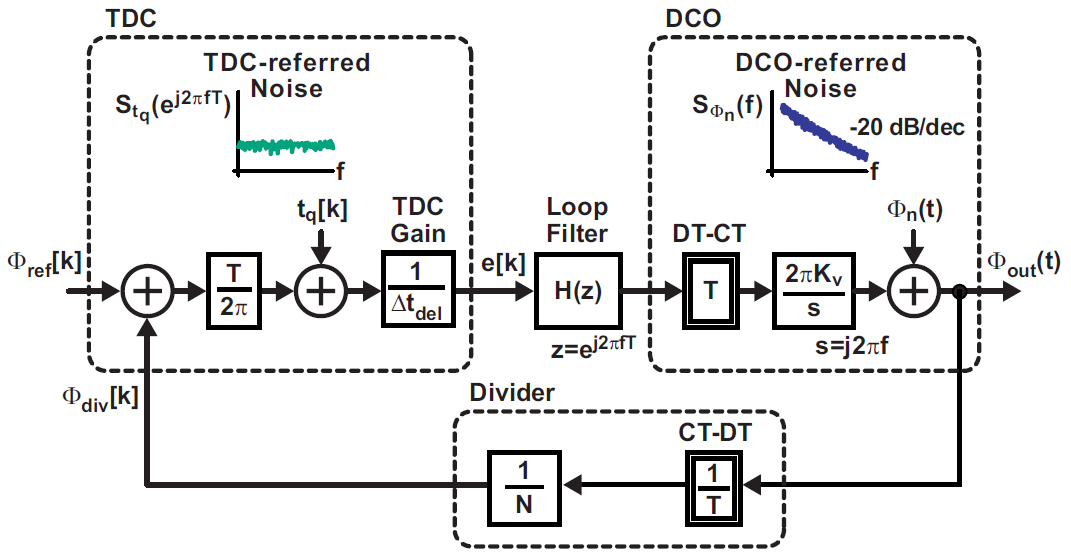

对完整ADPLL进行建模,得到其信号流图如下图所示:

其中TDC引入噪声为\(t_q[k]\),DCO引入相位噪声\(\Phi_n(t)\)。通过分析环路我们可以得到开环传输函数\(A(f)\):

闭环传递函数\(G(f)\):

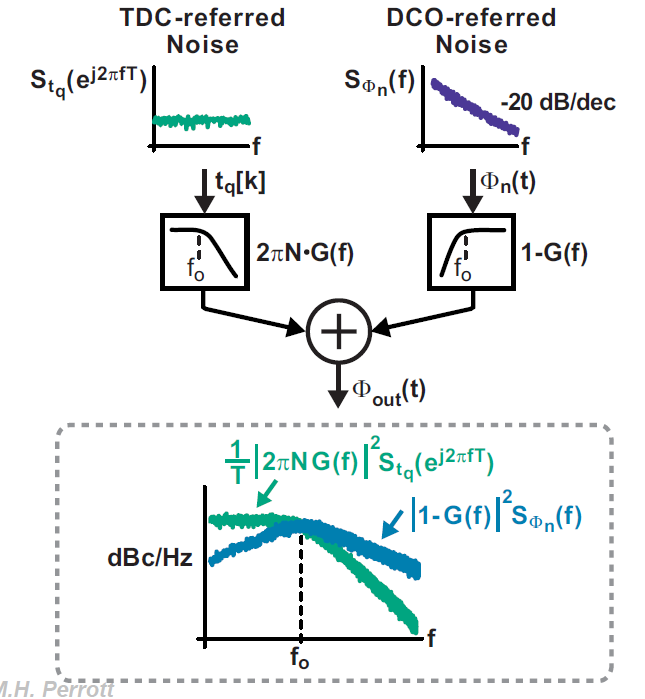

我们分析TDC噪声到输出相位的传输函数\(\Phi_{out}/t_q\)与DCO噪声到输出相位的传输函数\(\Phi_{out}/\Phi_n\),有:

由于\(H(f)\)是低通滤波器,\(G(f)\)也具有低通特性,因此根据\((8.4.7)\),TDC噪声传输函数具有低通特性,而根据\((8.4.8)\),DCO噪声传输函数具有高通特性。

两个噪声传输函数对噪声功率密度谱做噪声整形,得到输出噪声的功率谱:

TDC引入的量化噪声类似于热噪声,而DCO引入的相位噪声类似于\(1/f\)噪声。总体上来看,由于噪声整形的影响,低频处输出噪声受到TDC噪声的支配,而在高频处输出噪声受到DCO噪声的支配。

总而言之,ADPLL带来的优点包括了可以摆脱无源器件带来的面积限制,可以降低电源电压,从而更好的适应工艺缩放。所有模块之间采用数字信号使其PVT敏感性降低。

参考资料:

"All-Digital Frequency Synthesizer In Deep-Submicron CMOS", Staszewski et. al.

浙公网安备 33010602011771号

浙公网安备 33010602011771号