模拟集成电路设计系列博客——7.5.6 时间交错型ADC

7.5.6 时间交错型ADC

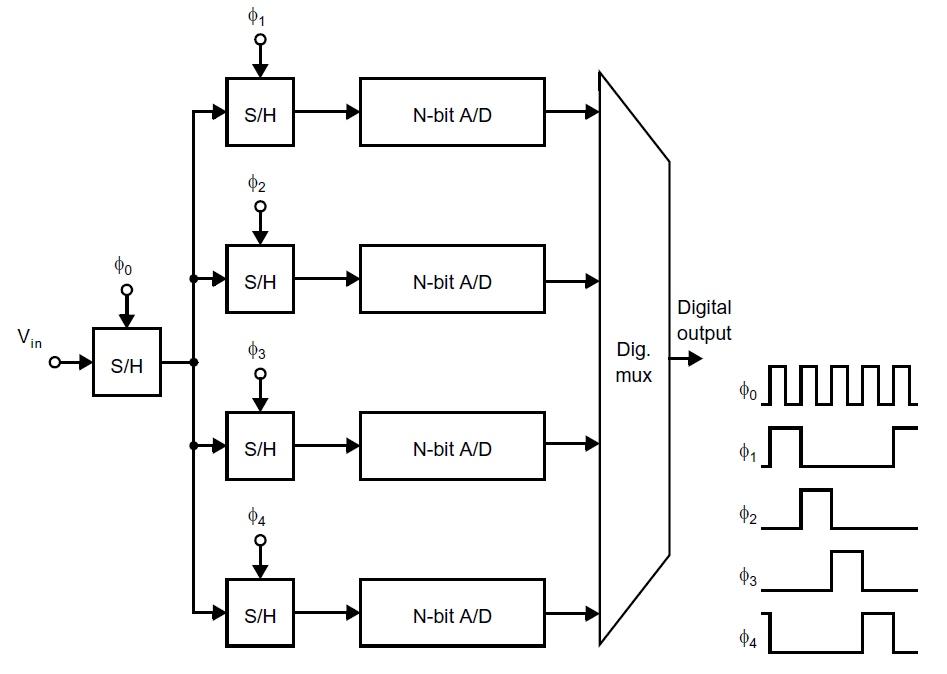

我们可以通过将多个ADC做并行来实现非常高速的ADC[Black, 1980]。下图展示了一个四通道时间交错型ADC的架构图:

此处,\(\phi_0\)是一个四倍于\(\phi_1\)到\(\phi_4\)的速率的时钟。此外,\(\phi_1\)到\(\phi_4\)彼此都落后一个\(\phi_0\)的周期。这样每个转换器都可以连续获得以\(\phi_0\)速率采用的输入信号\(V_{in}\)。通过这种方式,四个ADC可以以输入采样频率的四分之一进行工作。

使用这种方式时,以\(\phi_0\)频率工作的输入采样保持电路成为了关键,而剩余的四个采样保持电路可以容忍较大的时钟漂移,因为信号此时已经被采样好了。因此,有时输入采样保持电路会使用不同的工艺来实现,例如砷化镓,而剩余的采样保持电路可以使用硅工艺。一个\(1GHz\)的6 bit ADC使用了时间交错架构,并且使用了砷化镓的采样保持电路[Poulton, 1987],而四个双极型ADC每个以\(250MHz\)频率工作。

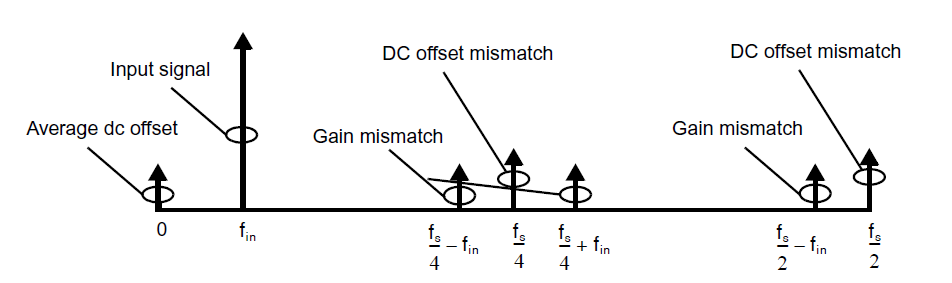

同样关键的问题是不同的采样保持电路和ADC信号路径是高度匹配的,因为不匹配会制造杂音。例如,考虑一个m路时间交错型ADC,有一个ADC有着\(100mV\)的直流偏差。这个系统每\(m\)个数字码会产生一个和其他\((m-1)\)个不同的杂音,其杂音频率为\(f_s/m\)及其谐波。这些杂音独立于输入信号的频率与幅度,并且即使在输入为零时也会产生。另一个错误源是,不同的采样保持电路和ADC电路呈现出不同的信号增益。在这个情况下,由于增益在周期性改变,输入信号实际上相当于乘以了一个周期性信号。因此,假设有一个\(f_{in}\)的正弦信号输入,输出会包含一个\(kf_s/m\pm f_{in}\)的谐波,其中\(k\)为整数。因为这属于内部调制的结果,因此其频率和幅度取决于输入信号的频率和幅度。并行信号路径之间的带宽失配则会导致取决于频率的增益失配,并且也会带来杂音。这些非理想因素在许多的应用中的影响可能是灾难性的,因为杂音可能会出现在感兴趣频带内。下图展示了一个存在偏移和增益误差的输出频谱:

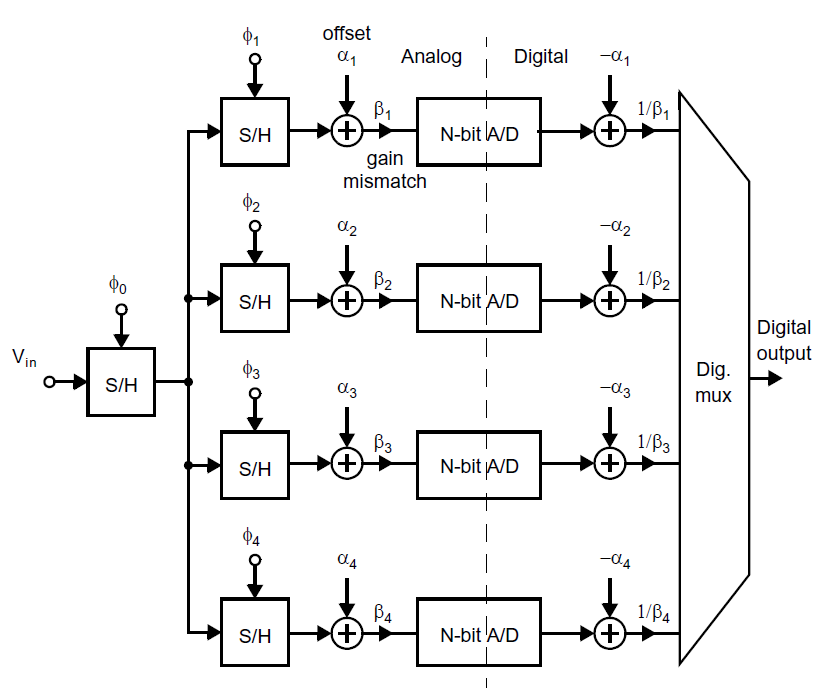

幸运的是,如果不同信号路径之间的失配可以被精确的识别,那么他们就可以通过数字的方式消除掉,如下图所示:

但是及时对其作了消除,偏移和增益失配还是增加了ADC在没有非线性情况下必须要能够处理的动态范围。

浙公网安备 33010602011771号

浙公网安备 33010602011771号