模拟集成电路设计系列博客——7.5.4 插值型ADC

7.5.4 插值型ADC

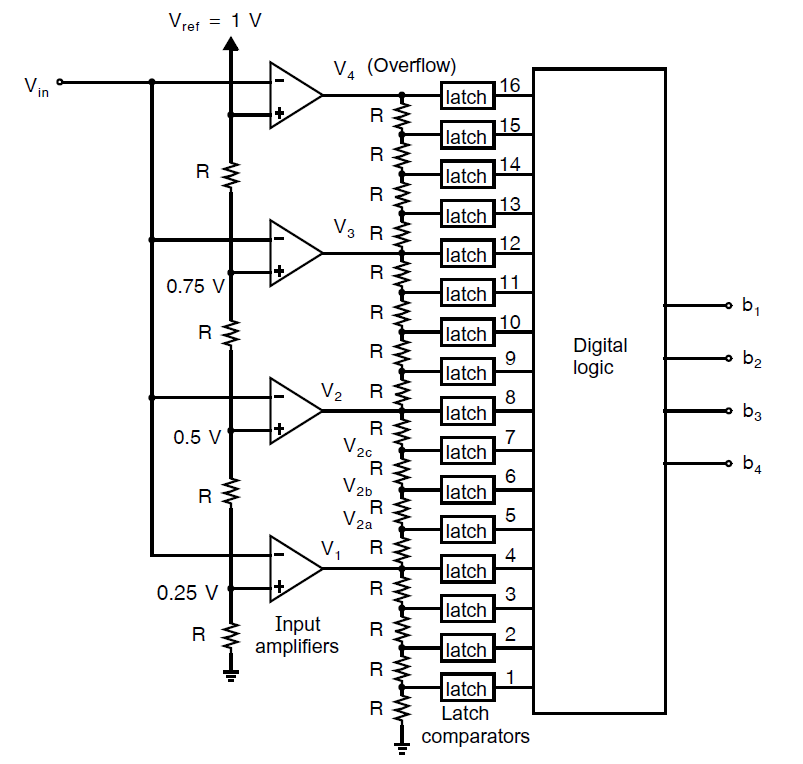

插值型ADC如下图所示使用输入放大器,这些输入放大器在其阈值电压附近表现为线性放大器,但是可以在它们的差分输入够大时饱和。作为结果,后续的锁存器只需要决定放大器输出的符号,因为输入信号和阈值电压之差已经被放大。同时,连接到\(V_{in}\)的输入放大器数量通过在这些放大器之间插值得到了充分的减少。尽管这个方式经常与折叠型ADC架构组合在一起[van de Grift, 1987; van Valburg, 1992],但插值型ADC架构本身也经常被成功的使用[Goodenough, 1989; Steyaert, 1993]。

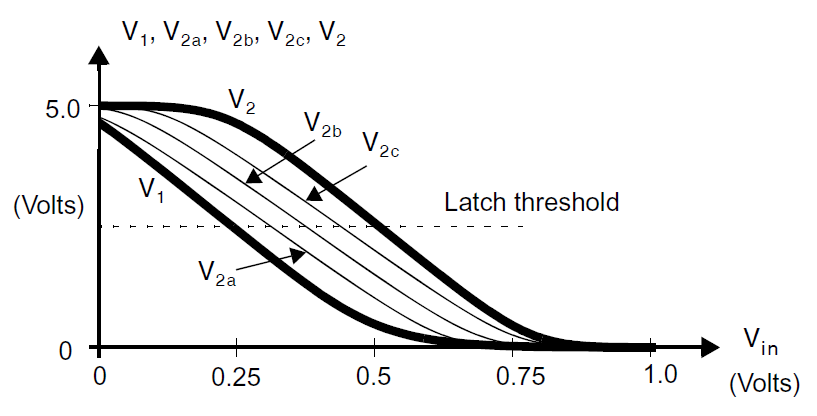

为了进一步理解插值方式,一组可能的输入放大器输出值\(V_1\),\(V_2\)及其插值如下图所示。在图中可以看出,逻辑电平被认定为\(0V\)或者\(5V\),输入放大器的最大增益大概为\(-10\)。同时,此处锁存器的阈值大概在两个逻辑电平的中间点(大概\(2.5V\))。随着\(V_{in}\)增大,\(V_1\)的锁存器首先被触发,随后是\(V_{2a}\),直到\(V_2\)。事实上,\(V_1\)和\(V_2\)之间可以可以创造更多参考电平。需要注意的是为了良好的线性度,插值信号只需要在正确的点穿越锁存器阈值,而剩余的插值信号响应是次要的。一种创造正确的穿越点的方式是确保\(V_1\)和\(V_2\)在他们自己的阈值是线性的。如下图所示,这个线性区是\(0.25<V_{in}<0.5\)。

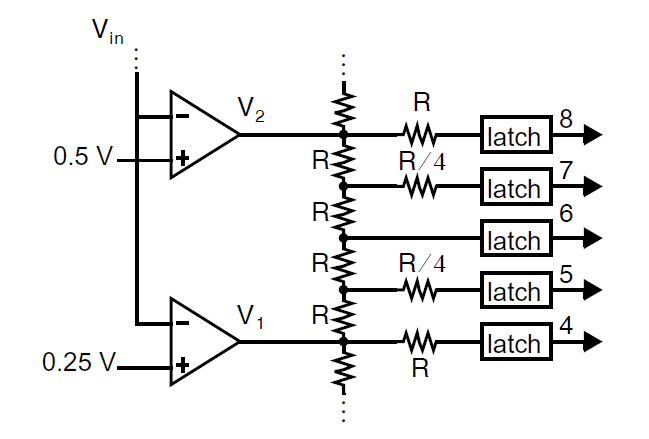

为了快速操作,有必要使得到每个锁存器的延迟都是尽可能相等的。由于锁存比较器有着类似的输入电容,通过增加额外的电阻就可以实现近似相等的延迟,如下图所示:

这些串联电阻使得每个锁存比较器看回电阻串时的阻抗都是相等的,假定输入放大器的输出均为低阻抗[van de Plassche, 1988]。

如早先提到的,插值型ADC架构的主要优点是减少了连接到输入信号\(V_{in}\)的差分对。这个减少使得输入的电容更小(而对于Flash ADC来说输入电容会很大),可以轻微减少功耗,并且要创造的精确参考电压也变得更少。最后,值得一提的是除了电阻串外其他的技术也可以用于实现插值型ADC架构。在[Steyaert, 1993]中,电流镜被用于在比较器间做8次插值。在另一个实现中,使用电容实现了两级的插值[JKusumoto, 1993]。

例题:

使用电流镜,实现对两个电流输出\(I_1\)和\(I_2\)的插值,插值出三个间隔。讨论这个架构相比传统Flash ADC的架构可以减少多少输入电容?

解答:

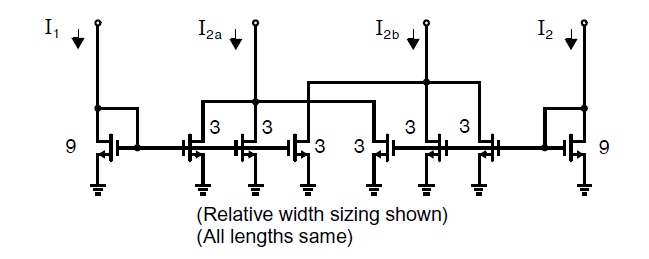

如果要插值出三个间隔,就需要增加两个新电流\(I_{2a}\)和\(I_{2b}\),从而:

这两个输出电流可以通过下图中的方式实现:

这四个电流可以转换成电压后再送到锁存器中。也可以直接直接送入到使用电流作为输入的锁存器中。

由于我们此处做的是三插值,这个转换器需要传统Flash ADC三分之一的输入放大器数量。因此这个插值型ADC架构的输入电容相比Flash ADC可以减少三分之二。

浙公网安备 33010602011771号

浙公网安备 33010602011771号