模拟集成电路设计系列博客——7.3.1 并联比较型ADC基本介绍

7.3.1 并联比较型ADC基本介绍

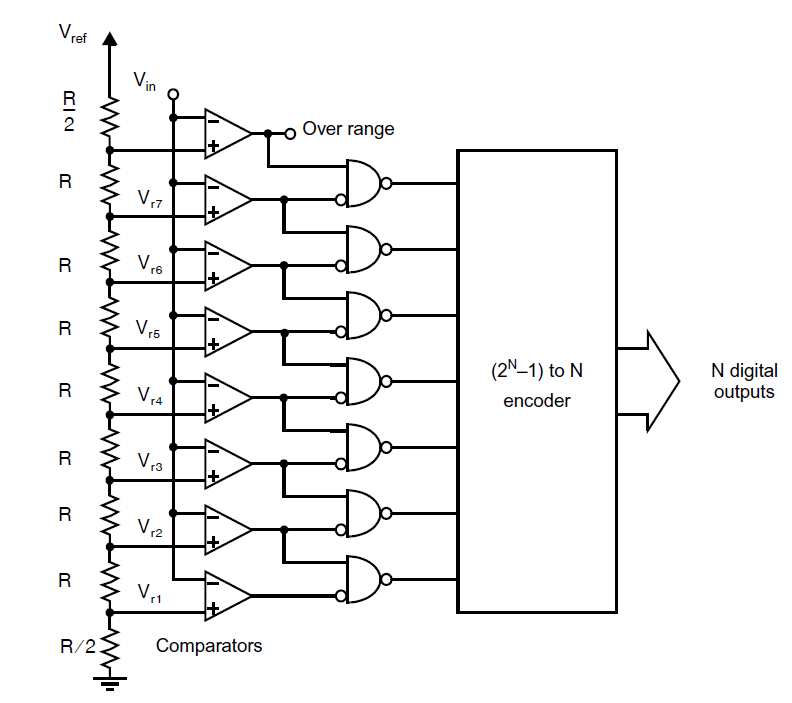

并联比较型ADC(后续都称作Flash ADC)是实现超高速转换器的标准方式。Flash ADC的输入信号被并行的馈入\(2^N\)个比较器中,如下图所示:

每个比较器被连接到电阻串的节点上。任何连接到电阻串节点的比较器,如果\(V_{ri}\)大于\(V_{in}\)有着1的输出,而\(V_{ri}\)小于\(V_{in}\)有着0的输出。这样的输出码是以温度计码的形式表示的(之所以叫温度计码是因为看上去像温度计里面的水银条)。注意在顶部和底部的电阻被设置为\(R/2\),从而在ADC中创造一个0.5LSB的偏移。

有一个0输入连接在其反相输入端的与非门,1输入连接到其非反相输入端,监测比较器输出从1到0的翻转,并且会以0进行输出。其他的所有与非门输出则会是1,从而实现一个简单的编码。这样的设计使得可以通过检测是否有超过一个0输出来进行错误检测,这种错误称为冒泡错误,也可以进行错误纠正。

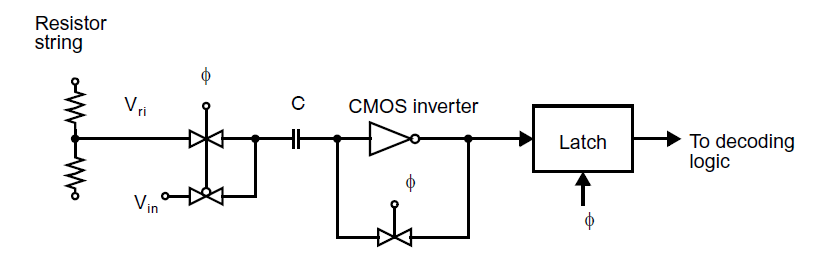

Flash ADC非常快速,但是其比较器数量的增长跟随分辨率\(N\)的指数,所以他们通常消耗很大的面积,并且非常消耗能量,即使对于一个不大的\(N\)——尤其是在时钟很快的时候。一种实现一个小时钟CMOS比较器的方式是使用CMOS反相器,如下图所示[Dingwall, 1979]:

当\(\phi\)为高时,反相器被设置到其双向稳定工作点,其输入电压等于其输出电压(例如阈值电压)。一般来说通过偶数个反相器,可以形成一个环形振荡器;然而在单个CMOS比较其中,反相器作为一个只有一个极点的单极放大器(没有非主极点)工作,所以保证了稳定性。通过将这个反相器设置到其阈值电压,另一边的\(C\)被充电到\(V_{ri}\)。当\(\phi\)降低时,反相器可以根据其输入电压自由的被拉高或者被拉低。与此同时,电容的另一侧被拉到输入电压\(V_{in}\)。由于电容在反相器的一侧是浮动的,\(C\)必须保持其原始的电荷,因此反相器的输入会根据\(V_{ri}\)和\(V_{in}\)的差发生改变,由于反相器的输入处于一个双相稳定点,\(V_{ri}\)和\(V_{in}\)的差值会决定反相器的输出会改变到哪个方向。但是,需要注意的是这个简单的比较器的电源抑制能力很差,一般这是高速比较器中的一个重要设计参数。通过全差分反相器可以帮助解决这一缺点。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具