模拟集成电路设计系列博客——7.2.1 流水线ADC基本介绍

7.2.1 流水线ADC基本介绍

流水线ADC和逐次比较型ADC类似,通过迭代搜索查找能够精确反应模拟输入信号的数字码。但是,相比较于通过单个模拟电路执行迭代,流水线ADC有着独立的模拟级来专门执行每次转换。流水线ADC的信号流如下图所示:

所有的模拟级在每个时钟周期时进行工作,并且每个执行一个差分输入采样。由于\(N\)个迭代同时在进行,所以流水线ADC相比逐次比较型ADC会快上\(N\)倍,并且能够每个周期都进行一次输出。因此,流水线ADC经常被用于需要高速的应用。尽管\(N\)次转换能够并行,每次输入采样的完整转换在整个流水线中仍然需要\(N\)个周期,因此在流水线转换器中存在着\(N\)个时钟周期的延迟,这点与逐次逼近型转换器一样。

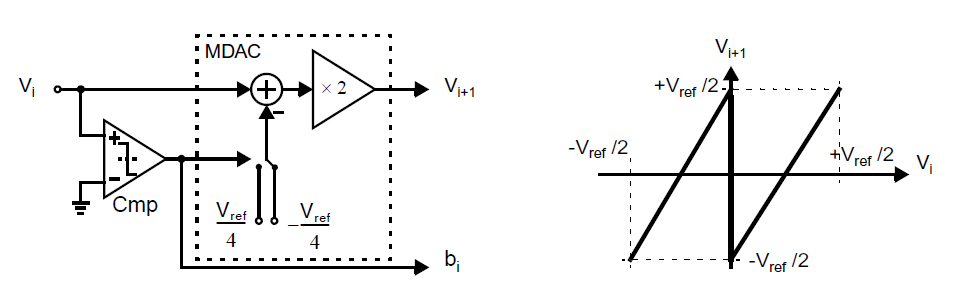

先从最简单的每级1比特流水线ADC开始介绍,每一级都接受上一级的输出作为输入,将其与一个参考阈值进行比较,并通过一个乘法DAC(MDAC)来形成一个残差信号:

如下图所示:

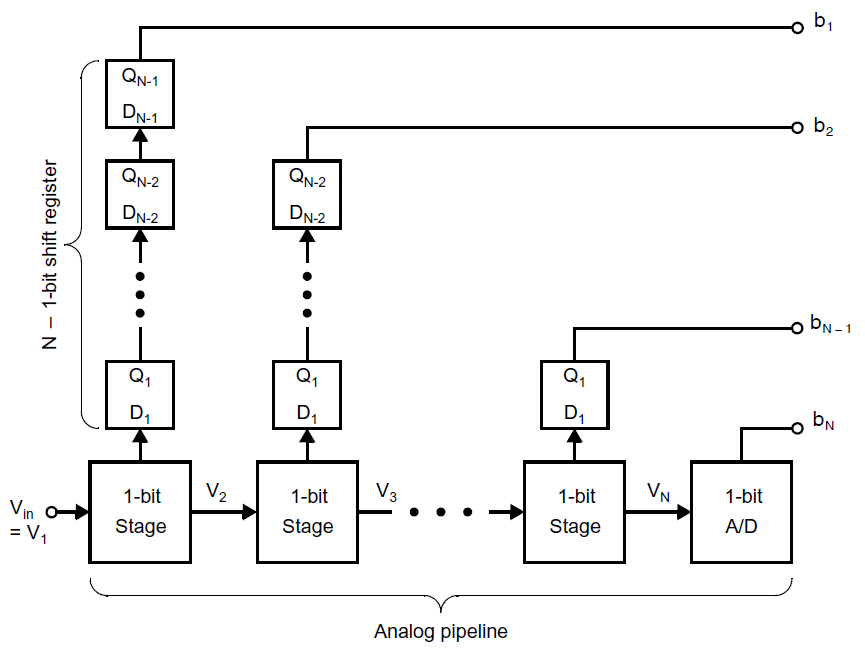

流水线ADC的每一级进行一个比较,找到一比特的结果\(b_i\)。但是由于每一级都工作在不同的采样上,这些数字信号必须通过可变长度的移位寄存器进行重新对齐,如下图所示:

转换的结果可以视作对原始输入采样进行\(N\)比特量化,误差范围在\(\pm V_{ref}/2\)。

最后,注意最终的残差信号不需要再被送入到下一个残差级,因此最后的MDAC可以省略掉,最后一级仅仅需要一个1比特的ADC(比较器)来产生\(b_N\)。

例题1:

考虑一个3比特,每阶段1比特的流水线ADC,其\(V_{ref}=1V\)。求所有级的残差电压\(V_i\)以及最终的输出码,采样输入电压为\(V_{in}=240mV\)。

解答:

输入信号给定\(V_1=V_{in}=240mV\),流水线ADC的第一级的比较器将会输出一个正的结果,\(b_1=1\)。这之后,从输入减去\(V_{ref}/4=250mV\)并将结果乘以2倍。

由于\(V_2<0\),在下一个时钟周期,第二级流水级将会产生一个逻辑低电平,\(b_2=0\),使得\(V_{ref}/4\)被加入到下一级的残差结果上:

最后,第三级将会输出一个逻辑高电平,使得最终的输出码为\(b_1b_2b_3=101\),等效为一个量化后的输入电压\(V_{in}=187.5mV\)。

每级1比特流水线ADC架构的问题是,任何比较器的偏移会导致不可修复的错误。为了使得每级1比特流水线ADC有着\(10mV\)分辨率,第一级比较器需要有着高于\(10mV\)的精度,第二级必须高于\(20mV\),第三级高于\(40mV\),以此类推。进度需求逐级递减,因为沿着流水线前进时,后一级工作在放大后的残差信号,因此他们对于转换器的整体精度影响也随着流水线前进而逐级递减。尽管如此,对于比较器的限制意味着每级1比特流水线结构很少使用。

例题2:

重复例子1中的计算,但此次假定比较器总的第二级有\(30mV\)的偏移。

解答:

如例题1中的分析,流水线ADC第一级会输出一个正的结果\(b_1=1\),使得\(V_2=-20mV\),这一次由于第二级比较器的偏移导致第二级产生一个逻辑电平\(b_2=1\),使得残差项上减去一个\(V_{ref}/4\):

这个残差结果超过了\(\pm V_{ref}/2\)的范围,因此进一步导致下一级的错误。最后一级会输出逻辑低电平,使得最终输出的码字为\(b_1b_2b_3=110\),或者\(V_{in}=375mV\),相比上一个例题中没有偏移的情况,最终的量化误差更大。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具