ASAP7nm PDK介绍

ASAP7nm PDK介绍

概述

最近在调研后面教学用的PDK,考虑到需要给学生发的PDK尽量绕开版权问题,因此Foundry PDK是不敢用的,大概把Synopsys家的SAED28_32nm,Cadence家的GPDK45nm,以及几个开源PDK都大概看了一下,目前倾向于用ASAP7nm这个PDK。

来说一下主要的分析和考量,首先C家和S家给的PDK的都是可以跑一个比较完整的flow,尤其是S家的SAED28_32nm,非常全,除了STD Cell,还给了Memory Compiler,IO,PLL等,可以说无限接近一个Foundry的商用PDK了,C家的GPDK相对东西少一些,但是IO库也给了(但不全,没有GDS,是虚拟IO),没有Memory Compiler,没有PLL。而ASAP7nm里是没有Memory Compiler,没有IO,没有PLL的,处于一个有点缺斤少两的状态。但前两者都有个致命的问题,主要是厂家为了推广自家工具而推出的教学PDK,所以都和自家的工具有着极高的绑定,例如SAED的模拟PDK只有他们自家的Custom Compiler能开,而主流在用的Virtuoso套件开不了,signoff的DRC/LVS rule也是只支持自家的IC Validator。而GPDK的DRC/LVS rule也是只有自家的Assura能开,并不支持主流的Signoff工具Calibre(众所周知这两家的工具以前是有点故事的)。而ASAP在这方面贴心的多,基本上和常见的Foundry PDK的做法一致,给Virtuoso能开的模拟PDK,以及Calibre能开的DRC/LVS rule。尽管也许能想办法倒腾一下SAED或者GPDK解决上述的工具支持问题,但我不太想在这方面太过折腾,总之还是教学用比较贴近实际开发时Flow来做吧。整体上想教的一个flow是VCS&Verdi(front-end)-> DC(synthesis)-> Innovus(backend)-> PT(timing signoff)-> Calibre(physical signoff)这样的一套,不过得看教学可用的软件license情况,到时候再说吧。回到ASAP的优势上来,除了能够用主流的flow,不必被框在某家的工具里之外,还有一点是这是个7nm FinFET的PDK,众所周知目前国内在先进工艺上被卡的是比较厉害的,虽然主要被卡的是制造那块,但设计这块目前教学FinFET工艺的普及度也很低,让学生尽早接触FinFET工艺对于国内半导体产业往先进制程发展的意义显然更大一些,综上所述,尽管ASAP有相比成熟商用PDK缺少的东西较多的缺点,但瑕不掩瑜,如果有条件的话,后续还可以尝试自己搓点IO,Memory Compiler,PLL这些东西加到教学flow里,使得整体上更加完善。

ASAP7是The OpenRoad Project的一部分,主要贡献者来自亚利桑那大学 (The University of Arizona)和ARM,作者发布的文章见:

- L. T. Clark, V. Vashishtha, L. Shifren, A. Gujja, S. Sinha, B. Cline, C. Ramamurthy, and G. Yeric, “ASAP: A 7-nm finFET predictive process design kit,” Microelectronics Journal, vol. 53, pp. 105-115, Jul. 2016.

这里有篇paper做了教育PDK的细致对比,感兴趣的可以自行阅读。https://pages.hmc.edu/harris/research/asap7.pdf

然后回到ASAP7nm的PDK的内容分析上,ASAP7nm的文件树如下:

./ASAP_7nm/

├── asap7_pdk_r1p7

│ ├── asap7ssc7p5t_05

│ ├── calibre

│ ├── cdslib

│ ├── docs

│ ├── drc

│ ├── lvs

│ ├── models

│ └── pex

├── asap7sc6t_26

│ ├── CDL

│ ├── Datasheet

│ ├── GDS

│ ├── LEF

│ ├── LIB

│ ├── qrc

│ ├── techlef_misc

│ └── Verilog

├── asap7sc7p5t_28

│ ├── CDL

│ ├── Datasheet

│ ├── GDS

│ ├── LEF

│ ├── LIB

│ ├── license

│ ├── qrc

│ ├── techlef_misc

│ └── Verilog

└── asap7_sram_0p0

├── gds

├── generated

└── verilog

其中asap7sc6t_26和asap7sc7pt5_28是数字标准单元库,分别是6-track和7.5-track,asap7_pdk_r1p7是模拟PDK,asap7_sram_0p0是SRAM库。我们按顺序一个一个来看。

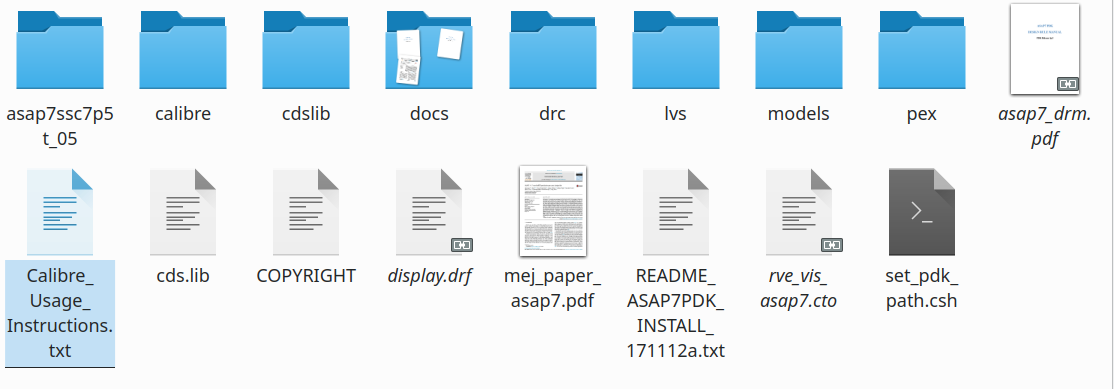

模拟PDK

模拟PDK需要走一个简单的安装流程,具体来说是,先去cdslib/setup下,编辑set_pdk_path.csh,把其中setenv PDK_DIR PDKdirectory里的PDKdirectory改成自己的PDK安装路径,比如我这里改成了:

setenv PDK_DIR /opt/PDKs/ASAP_7nm/asap7_pdk_r1p7

然后在asap7_pdk_r1p7目录下用csh分别运行set_pdk_path.csh和setup_asap7.csh两个脚本就行了。

./cdslib/setup/set_pdk_path.csh

./cdslib/setup/setup_asap7.csh

安装完成后目录下会多出一点东西:

开Virtuoso,cdslib里添加DEFINE asap7_TechLib PDK_DIR/cdslib/asap7_TechLib,把工艺库加进来就行了,还有一个sample STD Cell的lib,用DEFINE asap7ssc7p5t PDK_DIR/asap7ssc7p5t_05来添加。

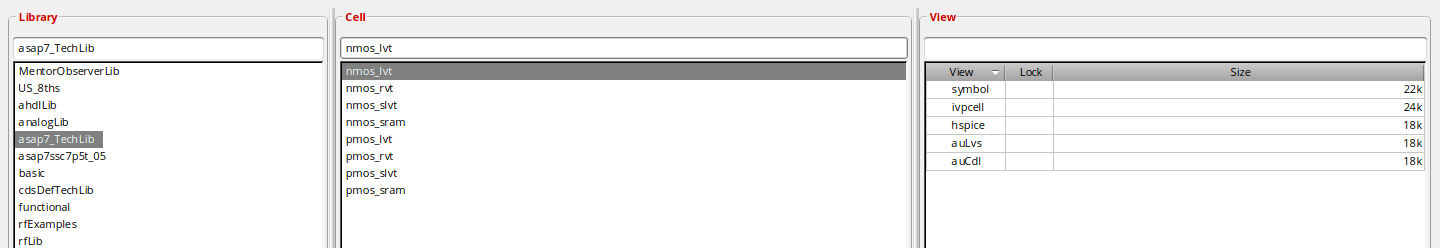

可以看到asap7_TechLib下给的cell其实挺少的,只有lvt,rvt,slvt和sram四种的nmos和pmos,阈值电压从低到高。没有一般PDK会给的电阻,电容,二极管那些,并且管子没有layout view,这个是有点坑的事情。另外仿真用的模型只有hspice view没有spectre view,这个也有点抽象。总体来说感觉不是一个可以比较完整走模拟flow的PDK,相比C家的GPDK还是差的比较多。不过有STD Cell和SRAM的情况下,走个数字flow问题不是太大。

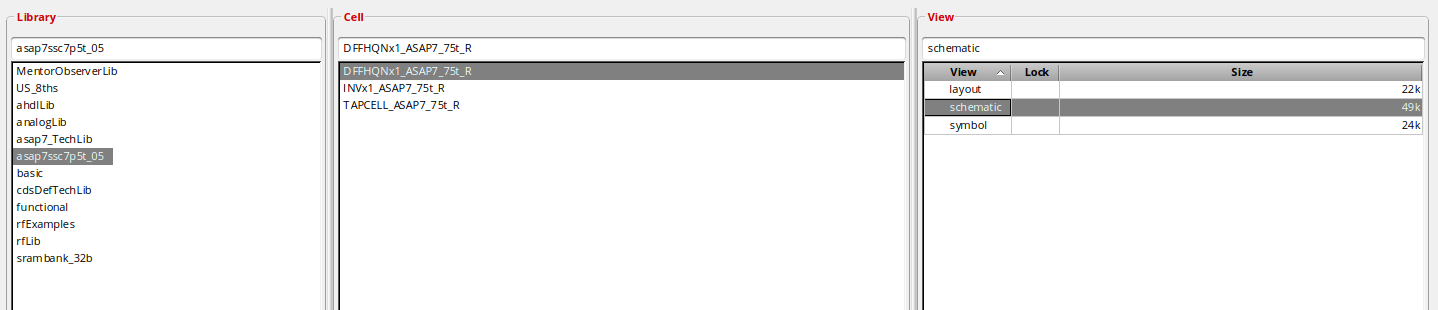

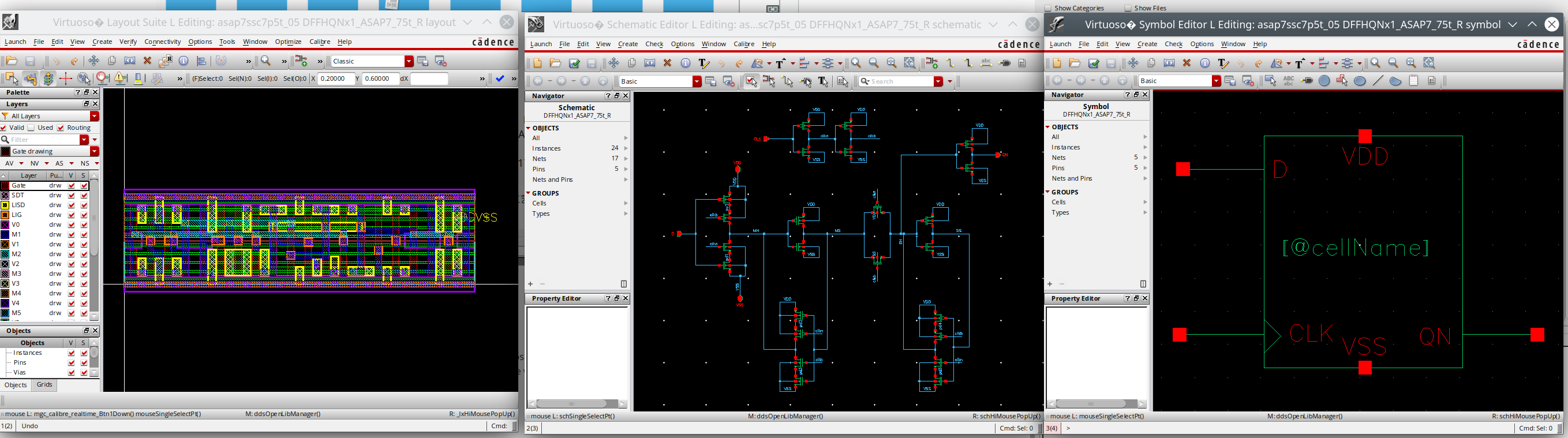

而asap7ssc7p5t_05下面是几个STD Cell,并给了layout:

以这个D触发器的cel为例:

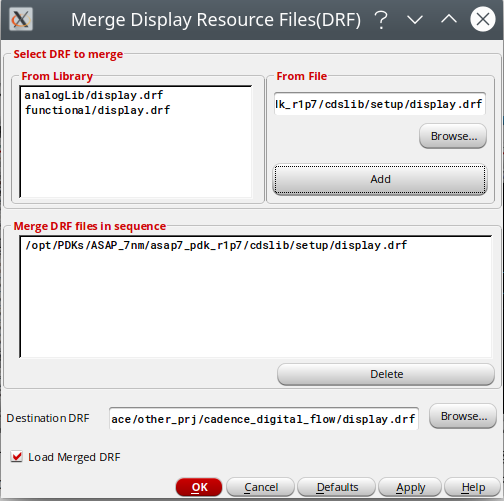

打开版图时可能会报display.drf没有merge的问题,这时开的layout全是黄框,通过CIW->Tools->Display Resource Manager...打开Display Resources Tool box,然后点Merge...,在From File中用Browse...选到asap7_pdk_r1p7下的display.drf,然后点Add,最后Destination DRF,在工程目录下新建一个display.drf,然后Browse上去,点ok即可。

可以看到这个PDK里面一共是1P9M,算上PAD层次一共10层金属。

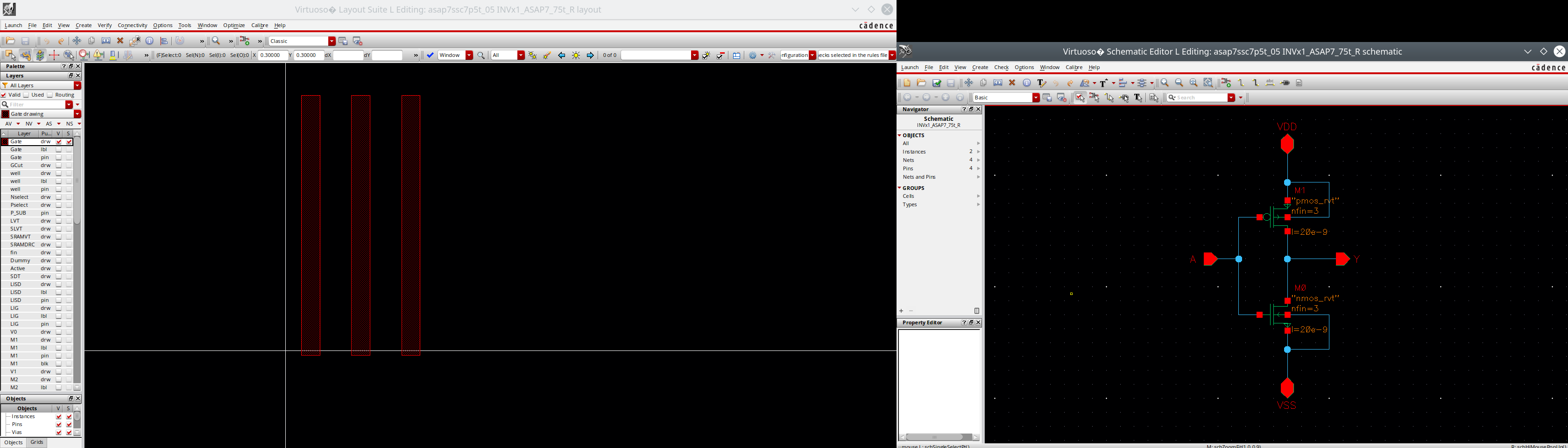

再看看inv这个cel,只开到gate层次,可以看到和schematic是对上的,nfin=3时,栅一共是三条,和平面晶体管还是挺不一样的。

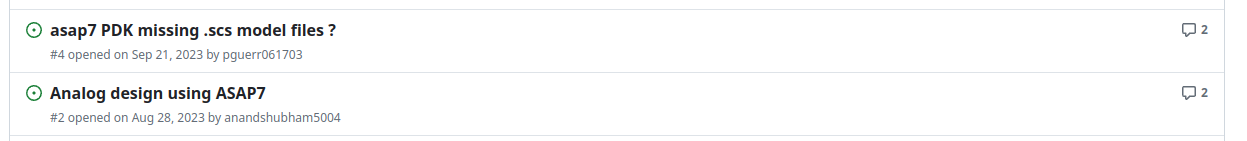

总体来说,这个模拟PDK对于我们做开发意义不大,主要的问题是缺少电阻,电容,二极管等必要器件,且没有给layout和spectre模型,github issue上23年有人提问过相同的问题,但是作者好像也没有正面回答。

但用来读取layout,进行简单的layout编辑,应该还是可以的。Design Rule文档可以在asap7_pdk_r1p7下找到,asap7_drm.pdf。DRC,LVS和RCX rule都在calibre文件夹下,但需要注意的是其无法直接从github上获取,需要去官网上进行获取。

SRAM库

asap7_pdk_r1p7能说的暂时先这么多,然后我们看一下asap7_sram_0p0这个SRAM库。之前提过,ASAP7并没有给memory compiler,即直接输入参数然后输出对应的memory的LEF,GDS,Verilog,LIB等file,这里的SRAM库实际上也不支持做到tapeout的程度,gds文件夹下是三个layout的示例,分别是32b,64b和128b(port width),而verilog文件夹下是一个示例用的64宽度,1024深度的SRAM行为模型。这两个文件夹下的内容应该都没法用到PR流程里,主要是generated文件夹下,有LEF,LIB和verilog三个文件夹。里面的内容分别是不同width和depth的SRAM的LEF,LIB和verilog,这里的命名方式可以简单分析一下,例如srambank_128x4x16,前两者之积应该对应了SRAM的depth,而最后一个对应了SRAM的width,比如下面的代码里,SRAM宽度是16,而深度是128*4=512。整个库一共提供了36个Size的SRAM,宽度从16到80,步进为2,深度则分别为256,512和1024,因此最大的尺寸是80*1024/8=10KB,最小是16*256/8=0.5KB。

// synchronous SRAM verilog

module srambank_128x4x16_6t122 (

input clk

, input [8:0] ADDRESS // address

, input [15:0] wd // data to write

, input banksel // access enable

, input read // read enable

, input write // write enable

, output reg [15:0] dataout // latched data output (only updated on read)

);

reg [15:0] mem [511:0];

always @ (posedge(clk))

begin // should have an error assert on read & write at once...

if (write & banksel)

mem[ADDRESS] <= wd;

else if (read & banksel)

dataout <= mem[ADDRESS]; // output is latched until next read, independent of writes

end

endmodule //

从行为级模型可以看出,就是很简单的同步单口SRAM模型,只有一套读写口,以及片选,读写使能信号和时钟,接口还是非常简单的,相比Foundry SRAM来说,没有DFT的接口。

由于有LEF,LIB和Verilog,用这个SRAM库走设计+综合+PR流程是没有太大的问题的,但是由于没有GDS和CDL网表,实际上是没法做DRC和LVS检查的,是一个比较遗憾的问题。

后面可以写一个简单的脚本,根据用户输入把对应尺寸的SRAM的LEF,LIB和verilog给筛出来,当做简单的Memory Compiler使用。不过一般Foundry的Memory Compiler还会要一个Mux的参数来控制SRAM的物理长宽,现在ASAP7这里还没有这个功能。

import os

import shutil

def copy_files(width, depth, source_dirs):

# 创建目标文件夹的名字

dest_dir = f"sram_{width}x{depth}"

# 计算 depth 参数除以 4 的值

depth_divided_by_4 = int(depth) // 4

# 初始化一个变量来跟踪是否找到了任何文件

found_files = False

# 遍历源文件夹

for dir in source_dirs:

for file_name in os.listdir(dir):

# 检查文件名是否包含 width 和 depth_divided_by_4

if str(width) in file_name and str(depth_divided_by_4) in file_name:

# 如果找到了匹配的文件,创建对应的目标子文件夹

if not found_files:

os.makedirs(dest_dir, exist_ok=True)

found_files = True

# 创建对应的目标子文件夹

dest_subdir = os.path.join(dest_dir, os.path.basename(dir))

if not os.path.exists(dest_subdir):

os.makedirs(dest_subdir)

# 复制文件到目标子文件夹

shutil.copy(os.path.join(dir, file_name), dest_subdir)

# 如果没有找到任何文件,打印报错信息

if not found_files:

print("错误:没有找到任何匹配的文件。")

# 用户输入

width = input("请输入 width: ")

depth = input("请输入 depth: ")

# 源文件夹列表

source_dirs = ["../generated/LEF", "../generated/LIB", "../generated/verilog"]

# 调用函数

copy_files(width, depth, source_dirs)

用AI非常快速的搓了一个,这个脚本会从 ../generated/LEF,../generated/LIB 和 ../generated/verilog 这三个目录中查找文件名匹配用户输入的 width 和 depth 参数的结果的文件,然后将这些文件复制到名为 sram_{width}x{depth} 的新文件夹中的对应子文件夹,其中 {width} 和 {depth} 是用户输入的参数。如果没有找到任何匹配的文件,脚本会打印报错信息,并且不会创建目标文件夹。

创建一个新的asap_mc文件夹在asap7_sram_0p0目录下,把asap_mc.py这个脚本放在asap_mc下,用python运行脚本,对应输入参数即可,例如:

sasasatori@sasasatori-System-Product-Name:/opt/PDKs/ASAP_7nm/asap7_sram_0p0/asap_mc$ python ./asap_mc.py

请输入 width: 20

请输入 depth: 256

会产生一个sram_20x256的文件夹,下面有LEF,LIB,verilog三个子文件夹,里面是从generated文件夹下对应查找到的文件。

如果长度和宽度输入非法,那么就会报找不到报错,不会产生任何文件。

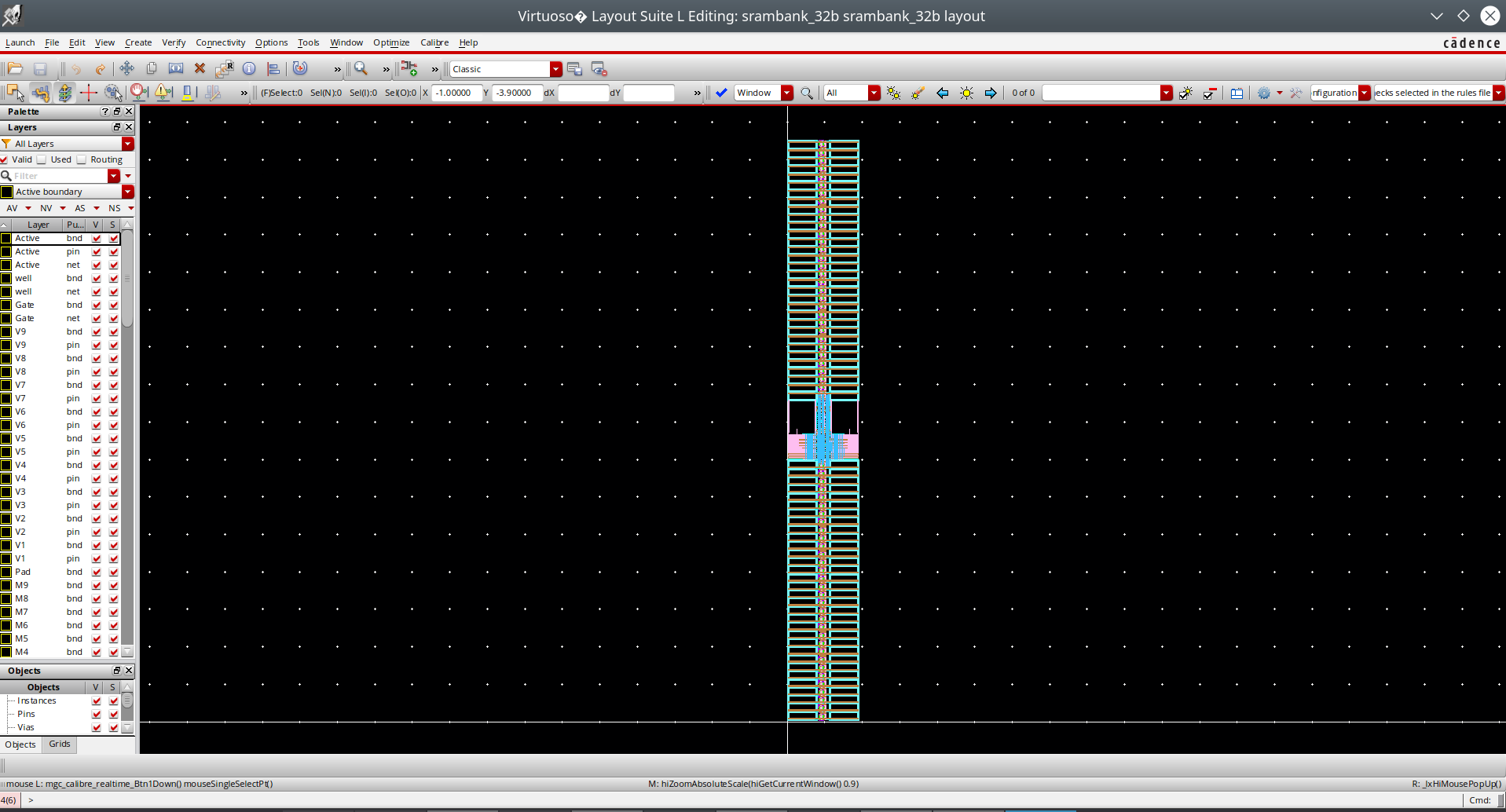

虽然generated没有给GDS,但是这里我们可以读取一个asap7_sram_0p0/gds下的srambank_32b.gds,新建一个仓库后stream in进来,可以看到sram bank的layout,上下是SRAM阵列,中间是decode的logic。

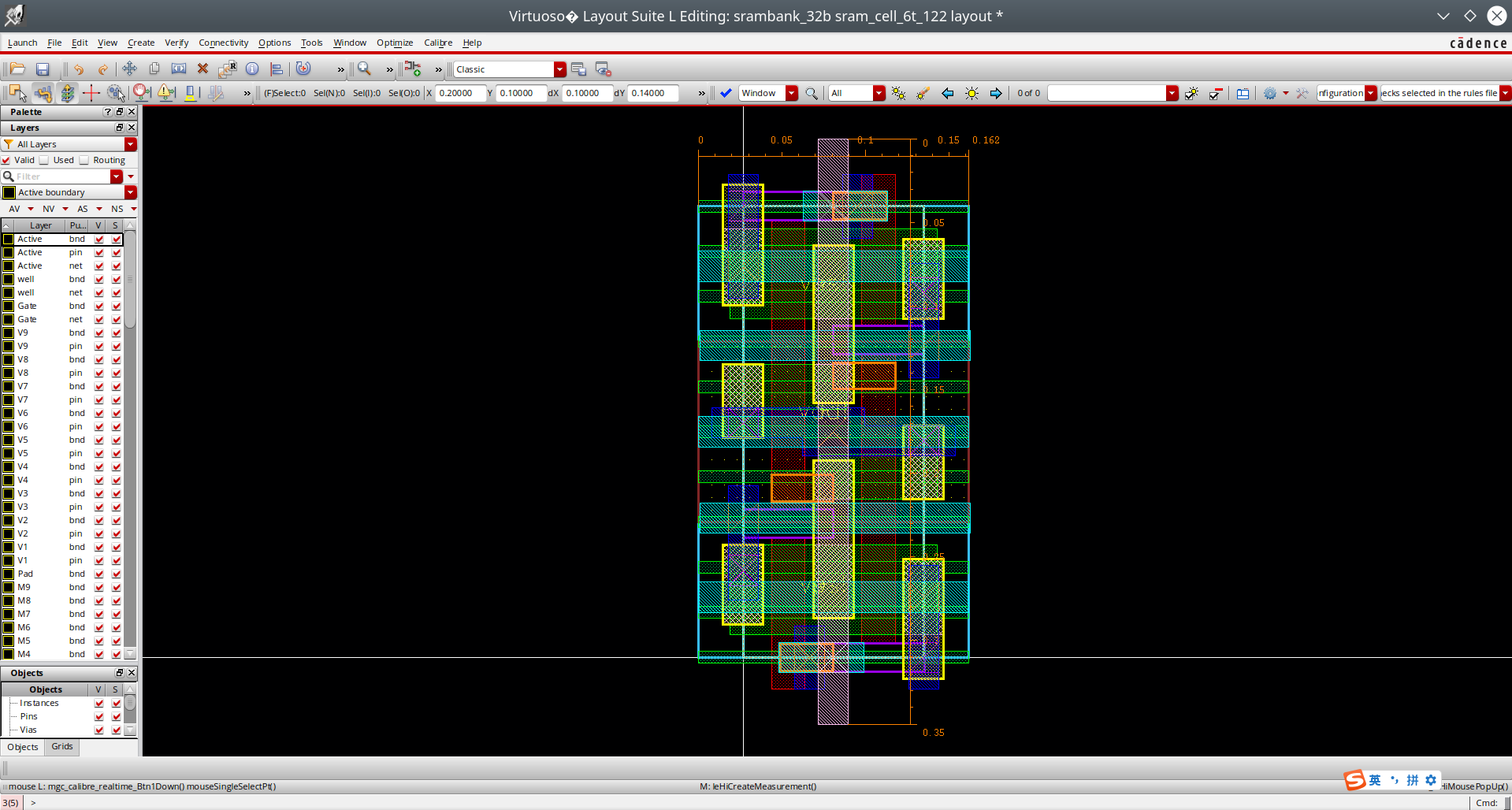

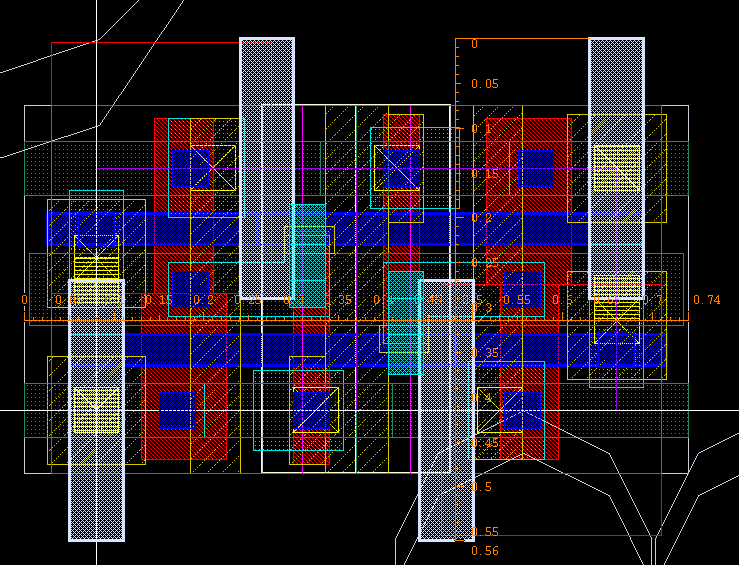

单个SRAM Cell的尺寸只有0.162um*0.35um=0.057um^2,可以说很小了。

与之相对的,一个t28的SRAM Cell的尺寸是0.56um*0.74um=0.414um^2,是ASAP7的7.26倍。

标准单元库

接下来看标准单元库的内容,7p5t版本和6t版本区别不大,所以我这里以7p5t为例,来对内容做一个主要的分析。从目录来看是一个从前端到后端的比较完整的库,并且库大小也是比较大,将近6个G。

其中CDL是网表。Datasheet下是标准单元的信息文档。GDS是版图文件。LEF是标准单元的Frame,Innovus可以直接吃,但没有S家工具可以直接吃的Milkyway或者NDM。LIB分成CCS和NLDM两个,CCS是相比NLDM更精确的延迟模型,详见:https://blog.csdn.net/u011075954/article/details/121229023。

license下是库的license声明,qrc下是C家工具用的寄生参数文件,QRC是C家工具,StarRC是S家工具,不过都可以抽出SPEF后给PT用。techlef_misc下是工艺lef文件,给Innovus吃的,还放了两个示例脚本。Verilog下是标准单元的verilog网表。

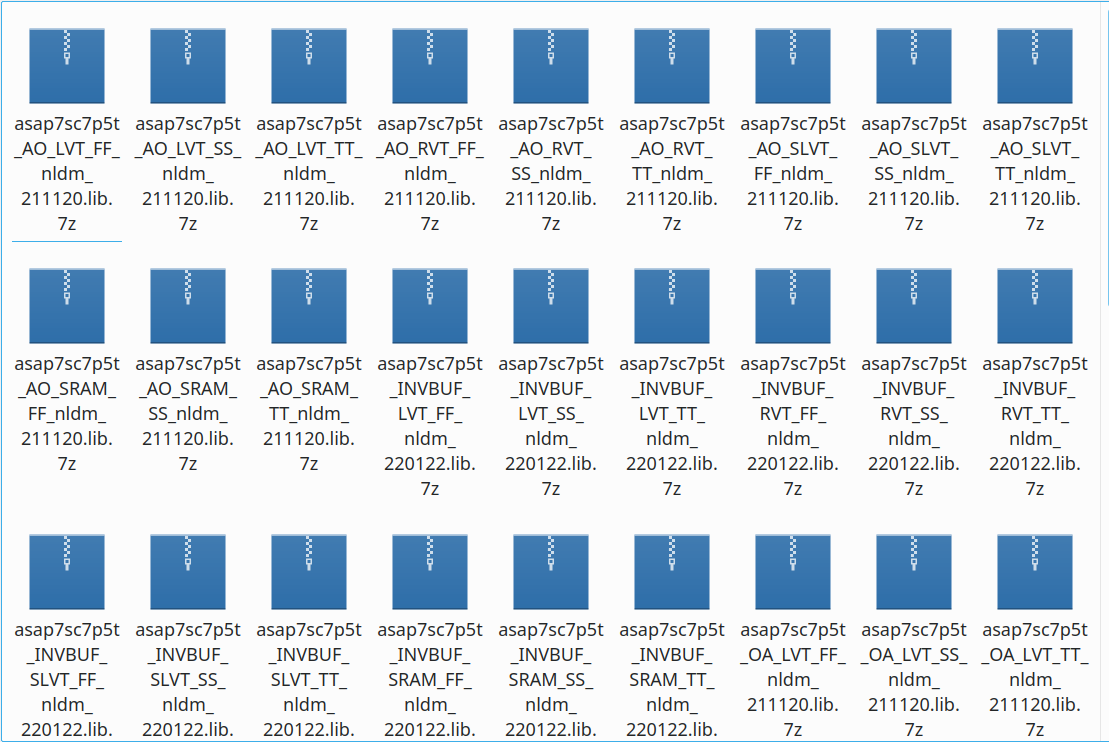

从LIB/NLDM文件夹下可以看到分了SS,TT,FF三个Corner,这个库做Multi-Corner是没问题的。

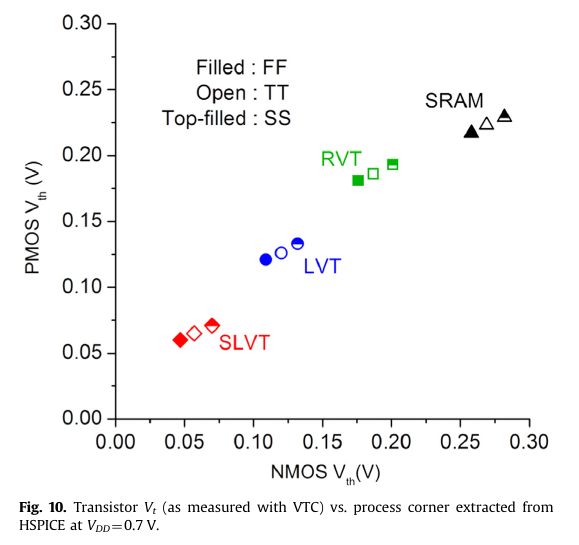

然后每类标准单元给了SLVT,LVT,RVT,SRAM四种器件的类型,这个和我们之前在PDK里面看到的也是一致的,分别是超低阈值,低阈值,正常阈值和SRAM阈值四种器件(这里SRAM阈值器件可以当成HVT器件来看待?),看论文里SLVT阈值电压在0.05V左右,LVT在0.125V左右,RVT在0.2V左右,SRAM的NMOS在0.275V左右,PMOS在0.225V左右。把Corner和器件类型排列组合一下,每类器件就有3*4=12种了。

在此基础上,具体提供的Cell包括了基本逻辑门的SIMPLE Cells,时序器件DFF的SEQ Cells,反相器BUFF的INVBUF Cells以及与或门和或与门的AO Cells以及OA Cells,总共5类,算是比较齐全的标准单元库了。

值得一提的是,7p5t下的Verilog文件里只有TT Corner,6t下的有SS,TT,FF三个Corner,但不同Corner的文件内容似乎无差异。此外6t的库里多出了一类反相器Cell,CKINVDC Cells,推测是给时钟用的。

结语

至此算是完成了对ASAP7这个开源PDK的一个较为全面的分析,后续会尝试在这个PDK的基础上去run一个设计用于教学实验,整个ASAP7除了calibre的rule外均可以从github上获取,考虑到国内访问github可能存在的网络不便的问题,我在百度网盘上也对整个库做了一下备份,有需要者可告明来意,我会share链接。

参考资料

PDK:The-OpenROAD-Project/asap7 (github.com)

asap7 reference design:Centre-for-Hardware-Security/asap7_reference_design: reference block design for the ASAP7nm library in Cadence Innovus (github.com)

介绍文件:ASAP7: A 7-nm finFET predictive process design kit - ScienceDirect

浙公网安备 33010602011771号

浙公网安备 33010602011771号