24年5.12流片复盘

非常值得纪念的一天,因为去年这个时候流片delay,今年顺利流出去了,这是一个大的进步,但是还是要做复盘。

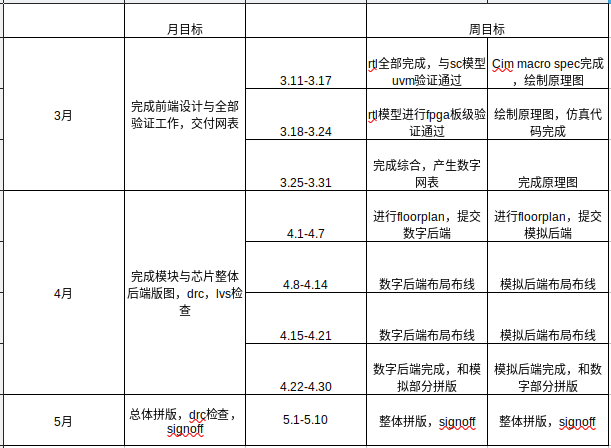

首先是进度整体上的复盘。这次流片从一月初开始进行规划,到五月初投片,总共花费五个月时间,五个月内,按照最初的时间规划,一月是把规划基本都做完,给项目参与人员一段上手熟悉任务的时间,二月份开始推研发进度,三、四、五月份是紧锣密鼓的推进项目进度,前端一个月,后端一个月,最后一周多时间做merge和signoff。

对比规划,从实际情况来看,一月份总体规划上没有太大的问题,要设计的macro的基本方案和soc的方案都做完了,虽然还没写spec做详细的设计,但大方向已经没问题,各个方向的人也领了任务开始初步弄了。到了二月初,负责RTL开发,SystemC和UVM的都差不多上道了,虽然整体工程还没搭建起来,但工作算是开始进行了。

二月份,由于过年是在这段时间,加上年后我去了趟美国,二月份我自己这边实际上没推动多少进度,到了月底,RTL,SystemC和UVM各自有一些进展,RTL那边算是比较超过预期的,基本的SoC已经成功搭建起来开始run了,SystemC也有个可以跑的东西了,UVM仍然还在弄一些简单的demo,还没有按照设想的那样跑通自动化测试的流程。二月底我从美国回来之后,开始介入到各个人的工作中去,首先肯定是工程整体上把框架给建立起来,用CMake,Makefile和Shell搭建了第一版的all_in_one工程,可以使用shell脚本来启动包括RTL编译,RTL仿真,SystemC编译,SystemC执行,驱动软件编译的功能。这是最初步的版本,后来完善后的all_in_one工程的shell脚本包括了不同版本的RTL编译和仿真,RTL综合,SystemC编译可执行文件和执行,以及编译到动态链接库,UVM编译,UVM仿真,软件驱动编译等功能。搭建了这个工程后开始推进展迟缓的UVM那边的进度,以及安排RTL和SystemC负责的人开始挂载外设。

三月份是比较繁忙的一个月,按照规划需要把前端的部分全部完成,帮助UVM那边用DPI把多线程的问题调通了之后,我开始负责自己弄的macro那边的RTL和SystemC模型开发的部分,RTL的进度是比较快的,基本上按时完成了RTL上的开发,开始上FPGA进行调试,中间一些功能测试上碰到一些bug,前后总共消耗了大概两周的时间,UVM那边则是到了三月下旬终于搭建起了能够把RTL和SystemC模型放在一起自动比较trace的功能。我自己macro的部分在去上海开会时完成了RTL参考模型的代码,并交给模拟那边开始做原理图,在月底时弄完了SystemC的代码。整个macro的原理图部分delay了大概一周,在四月初完成了。

四月份同样繁忙,综合进度比预期慢了一周多一些,一方面是FPGA的调试debug比想象中的时间要久,本来以为一周可以结束,最后全功能pass实际上花了两周。然后我做综合时memory compiler上踩坑,一直在用ARM的memory compiler,后面发现原来是用MC2的,浪费了几天时间。UVM开始发挥作用,帮助SystemC模型和RTL发现一些暗坑,只不过由于整体进入后端了,除去特别严重的bug之外,代码基本上没有再做返工。macro原理图完成后开始进入后端,此时因为还没有进行仿真,macro还是有不少问题的。对macro做混仿debug的工作大概持续到了3月下旬,过程中发现的bug就反馈到原理图,已经验证好的模块立刻开始做后端。最后整个macro在五月一时刚好完成,比预期慢了一周。好在由于用了lef的方式去做,merge的时间被节省下来了,所以相当于是flow的改进刚好弥补了这一周的进度delay。数字后端的推进速度也比想象的慢,预期上对于我的小设计能一周左右出结果,但因为最后是三个人在一起做的,所以都是花了一个月的时间,到了五月初才把最终的gds给出来,比预期delay了一周多。四月底时还交了一版GDS去dry run,影响了一些进度。

由于前面的delay,最后的工作就比较紧了,实际上最后顶层大图加总体DRC,LVS clean大概消耗了四天左右,挺要命的,好在顺利signoff了。

最后对整体的得失做做反思吧,首先是做得好的方面,SoC整个研发过程中借用开源节省时间这个之前也说过了,此外一个比较重要的事情是把macro做了IP化,自己写了LIB,抽了LEF,让数模两边的进度得到了一些并行,所以两边虽然各自delay了一周,但是因为merge基本上没怎么花时间,所以最后总的进度还是赶上了,此外在整体规划时尽可能的将大部分工作放到数字flow里面去弄,并在顶层的模拟模块直接复用以前做好的模拟IP,也节省了一些时间,相比去年,模块和顶层的工作量都少了很多,后面会考虑进一步延续这个思路,把目前的LDO+PLL的Analog模块做一个IP,IO也放到自动化的flow里面。也可以看看ADPLL的设计,看看能不能直接做一个可综合的PLL的IP放进来,LDO变成片外的稳压。此外TSMC28的大部分问题我们已经很熟悉了,这次没有踩什么PDK上的坑。此外今年基本上处理了除了数字后端以外的全部flow,数字模拟的前端,数字综合,模拟的后端,包括merge,dummy,DRC,LVS等很多都是在我这边搞定的,也是验证了我的观点,在紧要关头,最靠谱的永远是自己。

做的坏的方面,还是老毛病,对进度的把控不够严格,造成了大概一周的delay,有些delay是项目成员身上的,而是我自己这边直接造成的,不过这里的delay其实反过来看,不一定是执行端上的问题,在做规划的时候把一些问题给想象的太简单了,以为一周能搞定,实际上碰到一些麻烦的bug就是得用两周,这也是说明项目管理不是一个简单的纯静态过程,定好几个ddl就可以不管了,过程中需要不停的动态考虑每个环节的时间,哪个能加速,也说明在进行项目规划时就得留好一到两周的余量(但这个余量不能放到明面上来讲)。然后是整体上flow是还是留了不少手动的部分,在最后导致了一阵慌乱,以后可以考虑进一步简化过程,这个上面也分析过了,不表。最后还是对新flow不熟悉踩坑浪费的时间,比如第一次做LEF,返修了几次才给出来能用的,还有memory compiler上的踩坑,也是花了一段时间才熟悉清楚,浪费了综合的宝贵时间,并且由于不熟悉memory compiler出的SRAM的时序,反过来导致原来在理想SRAM模型上跑通的设计又得回头debug,其实可以更早的把理想SRAM模型换到compier SRAM模型上。

总结:进一步优化flow,提升效率,整理好可复用的结构,明年可以以此为基础做进一步迭代,将SRAM Compiler设计加入仿真的flow提前,并把后仿的时间做进规划里。进一步提升能力,今年争取自己能上去做数字后端 ,今年外包确实做的太慢了,硬是把后仿的时间挤没了,甚至还导致差点来不及signoff。

工程文件树:

.

├── all_in_one.sh

├── hw

│ ├── fpga

│ └── tapeout

├── README.md

├── sc

│ ├── build_exe

│ ├── build_so

│ ├── CMakeLists.txt

│ ├── doc

│ ├── Dockerfile

│ ├── inc

│ ├── LICENSE

│ ├── log.txt

│ ├── README.md

│ ├── run.sh

│ ├── spdlog

│ ├── src

│ ├── tests

│ └── user_guide.md

├── sw

│ ├── project

│ └── toolchain

└── uvm

├── prj

├── tb

└── work

all_in_one.sh脚本:

#!/bin/bash

#define using kde or gnome

use_gnome=0

if [ ! -n "$1" ]; then

echo "please input parameters, use './all_in_one.sh help' to see valid parameters"

fi

if [ "$1" == "help" ]; then

echo "use './all_in_one.sh sw' to build software driver"

echo "use './all_in_one.sh sc so' to compile shared library of systemc simulator for uvm running"

echo "use './all_in_one.sh sc exe' to compile systemc simulator executable file for running simulator"

echo "use './all_in_one.sh sc log' to run systemc simulator and save result to log, should be used after sc exe"

echo "use './all_in_one.sh sc' to run systemc simulator and print result in terminal, should be used after sc exe"

echo "use './all_in_one.sh hw fpga' to compile and run the fpga rtl code under soc testbench for peripheral function testing"

echo "use './all_in_one.sh hw tapeout' to compile and run the tapeout rtl code under soc testbench for peripheral function testing"

echo "use './all_in_one.sh hw xxxx jtag' to compile and run the rtl code under jtag testbench and start jtag debugger, xxxx should be fpga or tapeout"

echo "use './all_in_one.sh hw xxxx sim' to show rtl simulation waveform in verdi, should be used after hw fpga or hw tapeout, xxxx should be fpga or tapeout"

echo "use './all_in_one.sh hw tapeout syn' to run dc synthesis"

echo "use './all_in_one.sh uvm com xxxx' to compile uvm verification platform, xxxx should be fpga or tapeout, should be used after sc so"

echo "use './all_in_one.sh uvm sim [CASE]' to start uvm verification platform, [CASE] should be uvm case name, currently is my_case0"

elif [ "$1" == "sw" ]; then

cd ./sw/project

./build.sh

cd ../..

elif [ "$1" == "sc" ]; then

if [ "$2" == "so" ]; then

cd ./sc

./run.sh so

cd ..

elif [ "$2" == "exe" ]; then

cd ./sc

./run.sh exe

cd ..

elif [ "$2" == "log" ]; then

cd ./sc

./run.sh run > log.txt

cd ..

elif [ ! -n "$2" ]; then

cd ./sc

./run.sh run

cd ..

else

echo "invalid second parameter"

fi

elif [ "$1" == "hw" ]; then

if [ "$2" == "tapeout" ]; then

if [ "$3" == "jtag" ]; then

if [ ${use_gnome} == 1 ]; then

gnome-terminal -- bash -c "cd ./sw/toolchain/openocd; sleep 10; pwd; ./jtag_tcp_gnome.sh; exec bash;"

else

konsole --noclose -e /bin/bash -c "cd ./sw/toolchain/openocd; sleep 10; pwd; ./jtag_tcp_kde.sh; exec bash;" &

fi

cd ./hw/tapeout/prj

make vcs_jtag

cd ../../..

elif [ "$3" == "sim" ]; then

cd ./hw/tapeout/prj

make verdi_soc

cd ../../..

elif [ "$3" == "syn" ]; then

cd ./hw/tapeout/prj

make dc

cd ../../..

elif [ ! -n "$3" ]; then

cd ./hw/tapeout/prj

make vcs_soc

cd ../../..

else

echo "invalid third parameter"

fi

elif [ "$2" == "fpga" ]; then

if [ "$3" == "jtag" ]; then

if [ ${use_gnome} == 1 ]; then

gnome-terminal -- bash -c "cd ./sw/toolchain/openocd; sleep 10; pwd; ./jtag_tcp_gnome.sh; exec bash;"

else

konsole --noclose -e /bin/bash -c "cd ./sw/toolchain/openocd; sleep 10; pwd; ./jtag_tcp_kde.sh; exec bash;" &

fi

cd ./hw/fpga/prj

make vcs_jtag

cd ../../..

elif [ "$3" == "sim" ]; then

cd ./hw/fpga/prj

make verdi_soc

cd ../../..

elif [ ! -n "$3" ]; then

cd ./hw/fpga/prj

make vcs_soc

cd ../../..

else

echo "invalid third parameter"

fi

elif [ ! -n "$2" ]; then

echo "please give second parameter, fpga or tapeout"

else

echo "invalid second parameter"

fi

elif [ "$1" == "uvm" ]; then

if [ "$2" == "com" ]; then

if [ "$3" == "fpga" ]; then

cd ./uvm/prj

make vcs_com_fpga

cd ../../..

elif [ "$3" == "tapeout" ]; then

cd ./uvm/prj

make vcs_com_tapeout

cd ../../..

elif [ ! -n "$3" ]; then

echo "please give second parameter, fpga or tapeout"

else

echo "invalid third parameter"

fi

elif [ "$2" == "sim" ]; then

cd ./uvm/prj

if [ -z "$3" ]; then

echo "Usage: $0 uvm sim [CASE]"

exit 1

fi

CASE=$3

make vcs_sim CASE=$CASE

cd ../../..

elif [ ! -n "$2" ]; then

echo "please give second parameter, com or sim"

else

echo "invalid second parameter"

fi

else

echo "invalid parameter, please use ./all_in_one.sh help to see valid parameters"

fi

进度表:

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具