模拟集成电路设计系列博客——6.2.5 毛刺

6.2.5 毛刺

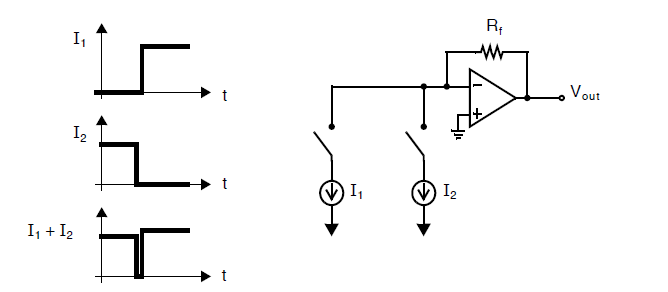

数字逻辑的毛刺是转换器进行高速工作时的一个主要问题,\({b_1,b_2,...,b_N}\)与开关信号直接关联。毛刺的来源是开关切换不同信号的延迟。例如,但数字码从\(0111...1\)切换到\(1000...0\)时,所有的\(N-1\)的LSB都关闭,而MSB打开,然而,有可能LSB开关的电流先于MSB开关的电流关断,使得总的电流瞬间降到零。与之相对,如果LSB开关的电流慢于MSB开关的电流,那么电流会瞬间变化到最大值。在这两个例子中,输出上都会出现毛刺,除非两个延迟精确匹配,然而对于每个分支上有着不同电流的电路来说这基本上是不可能的。可以用下图来理解毛刺的机理:

可以通过限制带宽的方式来降低毛刺的干扰(通过在上图中的电阻\(R_f\)两侧放一个电容),但是这种方式也会降低电路的速度。另一种方式是在输出信号上使用一个采样保持电路。最后,最常用的方式是将数字码从二进制码转换为温度计码,下一章节将进行讨论。

浙公网安备 33010602011771号

浙公网安备 33010602011771号