模拟集成电路设计系列博客——6.2.1 二进制权重电阻DAC

6.2.1 二进制权重电阻DAC

一种主流的实现D/A转换器的方式是将一组信号以二进制方式进行组合。这组二进制信号可以是电流(在电阻或者电流方式中),但二进制权重的电荷也经常使用。在这个章节中,将首先介绍店主方式,然后是和电荷重分布的模式和电流模式。在这个远离下并不能保证单调性,因为完全不同的组件被用于将数字码转换成模拟电压或者电流,并且在二进制权重阵列中大比重的部分打开或关闭时一般会观察到打的查封非线性(DNL,Differential Non-Linearity)。例如,这个失配效应一般在转换器的MSB改变时最大,使得此处有着最大的DNL。

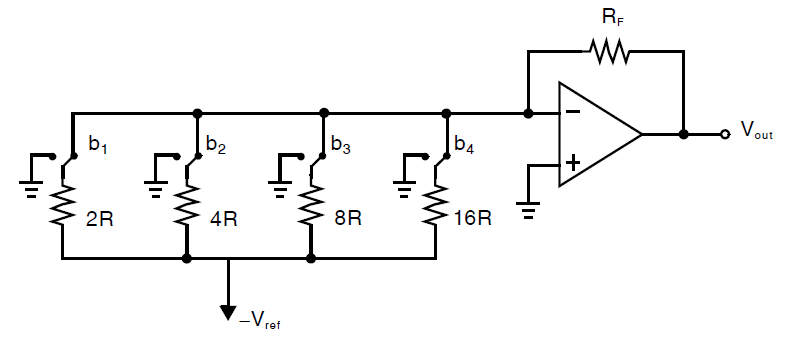

二进制权重电阻转换器对于双极型晶体管工艺来说更受欢迎,因为双极型晶体管差分对可以用于电流开关。一个基本的4-bit转换器架构如下图所示:

假设\(b_i\)为1,那么第\(i\)个电阻上会有来从放大器的虚地点的电流,否则电流会来自于地。因此,我们有:

\[V_{out}=-R_FV_{ref}(-\frac{b_1}{2R}-\frac{b_2}{4R}-\frac{b_3}{8R}-...)=(\frac{R_F}{R}V_{ref})B_{in} \tag{6.2.1}

\]

其中:

\[B_{in}=b_12^{-1}+b_22^{-2}+b_32^{-3}+... \tag{6.2.2}

\]

尽管这种模式并不需要许多电阻或者开关,但是仍然有一些缺点。电阻和电流的比例是\(2^N\),因此取决于\(N\),值可能会很大。这个大电流比例同样要求开关进行缩放,从而对于分布广泛的不同电流仍然可以使得开关上的压降相等。同时,这个方式没有保证单调性。最后,在高速应用中这种方式会引发毛刺。

标签:

模拟集成电路

, 模拟集成电路设计系列

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具

2023-05-01 SystemVerilog for Design Edition 2 Chapter 3 SystemVerilog Literal Values and Built-in Data Types