模拟集成电路设计系列博客——6.1.2 折叠电阻串DAC

6.1.2 折叠电阻串DAC

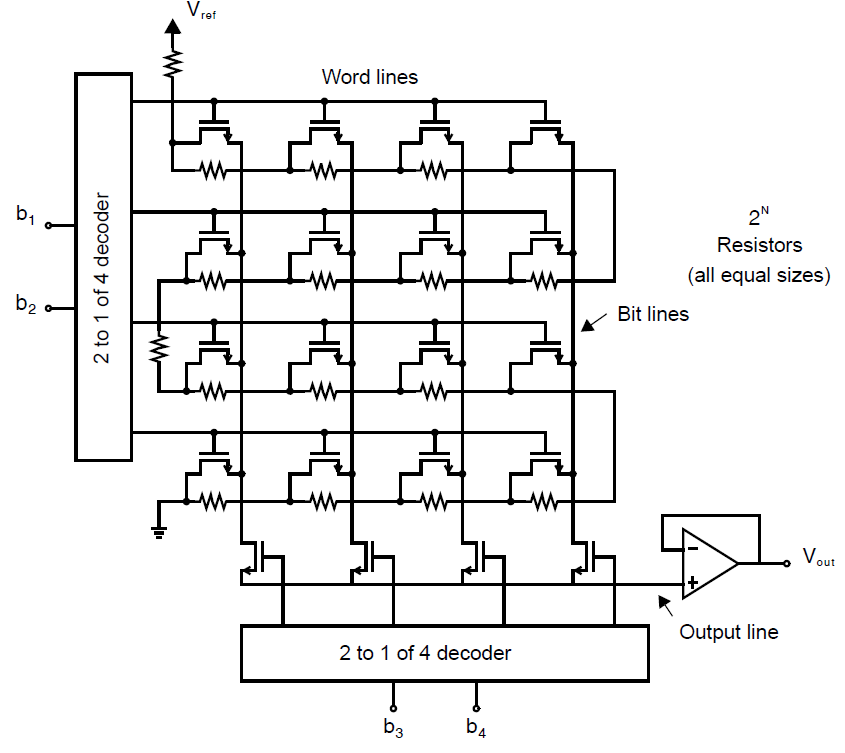

为了减少数字解码的数量以及大的容性负载,可以使用折叠电阻串D/A,如下图所示[Abrial,1988]:

这种方式使得解码非常类似于数字存储器,从而减少了总的解码区域。在上图中的4-bit例子中,为了转换数字码,高2比特{b1,b2}决定了需要选中的单个字线(其他的保持为低)。一个字线会连接到四个相邻的电阻节点,每个电阻节点又会连接到一个位线,位线通过位线解码器连接到输出缓冲器上。注意到现在连接到输出线上的晶体管连接点总数现在为\(2\sqrt{2^N}\),因为只有一部分晶体管直接连接到输出项上,儿其他的则被连接到选择用的位线上。因此,以10-bit的转换器为例,使用折叠电阻串的方式可以只有64个连接点的容性负载,而如果使用上一节中解码器设计方案,则需要1024个连接点。

然而不幸的是,速度并不能等比例的跟着快速上升,因为在字线拉高之后,所有的位线也需要被拉到新的电压水平,不只有连接到输出缓冲器的那一根位线。

浙公网安备 33010602011771号

浙公网安备 33010602011771号