模拟集成电路设计系列博客——6.1.1 电阻串DAC

6.1.1 电阻串DAC

最直接的实现\(N-bit\) D/A转换器的方式是产生\(2^N\)个参考信号,并根据数字输入码,将合适的信号传递到输出。我们将这种D/A转换器成为基于解码器的转换器。

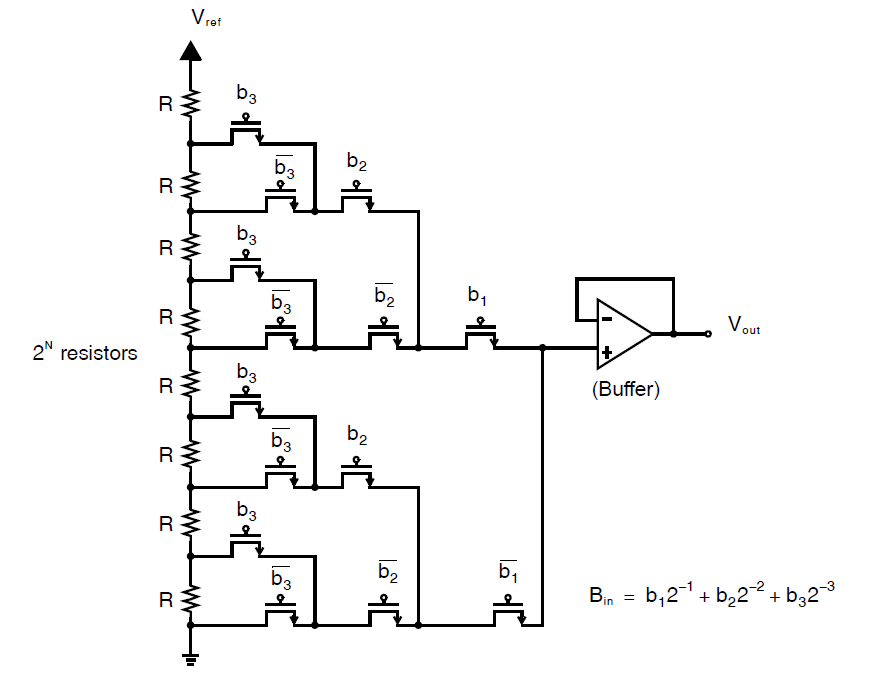

最早的8-bit集成MOS D/A转换器是基于通过一个开关网络选择一部分分段电阻串[Hamade,1978]。开关网络连接在一个树型解码器上。如下图中的3-bit D/A转换器所示:

注意在这个电路中有且仅有一个低阻路径存在于电阻串与输出缓冲器的输入之间,这个路径由数字输入码\(B_{in}\)决定。在一个CMOS视线中,一般会使用传输门而非n沟道开关。然而,当只使用n沟道导通晶体管时,树状解码器可以很紧凑的布局布线,因为在实现中不需要有布线交叉。通用,仅使用n沟道晶体管的方式与使用CMOS的传输门方式速度上相差不大。传输门方式有额外的漏极和源极对地的电容,但这个额外的电容可以通过因为n沟道和p沟道晶体管的并联组合减小的开关电阻来抵消。此外,传输门实现可以工作的更靠近正电源电压。

在电阻串方式中,如果假定缓冲器的输出偏移电压不取决于输入电压。D/A转换器通过每个电阻串的节点电压低于其相邻的上级节点电压来确保单调性。同时,D/A的进度取决于电阻串中\(R\)的匹配精度。同时电阻匹配进度取决于使用何种电阻,使用多晶硅电阻可以得到大概10-bit的精度。

开关网络的延迟是速度的主要限制,然而在乘法D/A中,电阻串中的延迟也会成为一个主要的延迟源,因为\(V_{ref}\)将会变成第二个输入信号。一个有效的减小\(RC\)类型电路(即只有实轴极点的电路)建立时间行为的方式是使用零时间常数方式[Sedra,1991]。

具体来说,主高频时间常数可以通过独立的时间常数之和来估计,因为对于每个电容来说,其他的电容都被设置为零(被替换为开路)。为了找到给定电容的独立时间常数,独立电压源被替换为地(独立电流源被替换为开路),电容看到的电阻就被决定了。

例题:

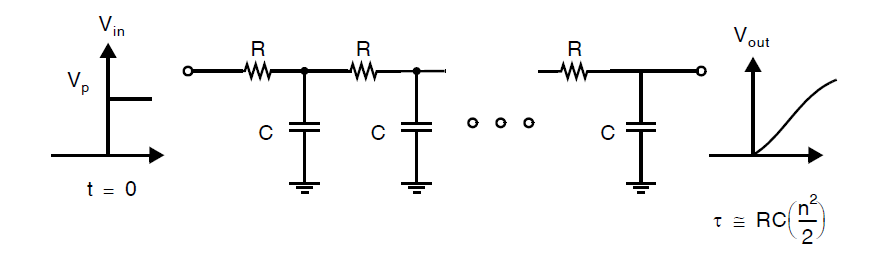

估计一个\(n\)个电阻组成的网络的时间常数,每个电阻都是串联,在每个节点上有电容负载\(C\),如下图所示,时间常数为\(\tau=RC(n^2/2)\)。输出达到最终值得百分之0.1时需要多少建立时间?

解答:

左侧第一个电容的零值时间常数为RC,左侧第二个电容的独立时间常数为2RC,以此类推,高频主时间常数\(\tau\)可以估计为:

从1加到n,根据等差求和公式为\(n(n+1)/2\),因此对于很大的\(n\),主要时间常数可以近似表达为:

使用这个时间常数来估计输出电压的充电行为,我们有:

因此,对于\(v_{out}\)等于0.999\(V_p\),我们发现需要\(7\tau\)的时间。

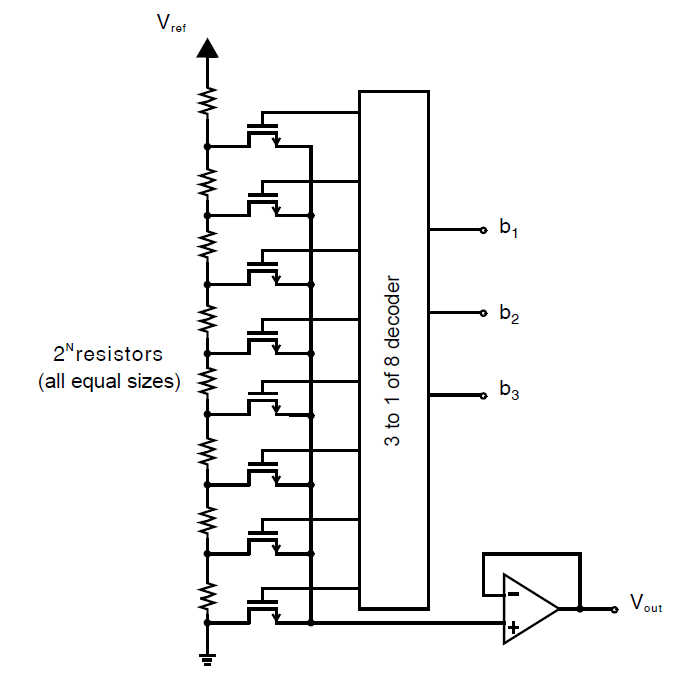

在更高速的应用中,可以使用逻辑电路制作解码器,将解码结果的总线连接到电阻串节点上,如下图所示:

这种方式,需要更大的解码器面积,并且在总线上有更大的容性负载,因为\(2^N\)个晶体管要连接到总线上。但是,如果数字解码器使用流水线,那么D/A也可以变得很快。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具