Virtuoso绘制模拟模块Frame并导出LEF

数模混合Flow时一些pin多的模拟模块可以通过导出lib和LEF,合并到数字flow中进行自动布线。

第一步肯定是和后端那边确定macro的形状以及各个端口的出pin方向和metal layer。这些确认完了之后,就可以开始做lef了。

网络上的教程交的是用abstract做,但实际上这是个很老旧的软件了,现在virtuoso本身就可以搞定全部的功能,我具体的操作如下:

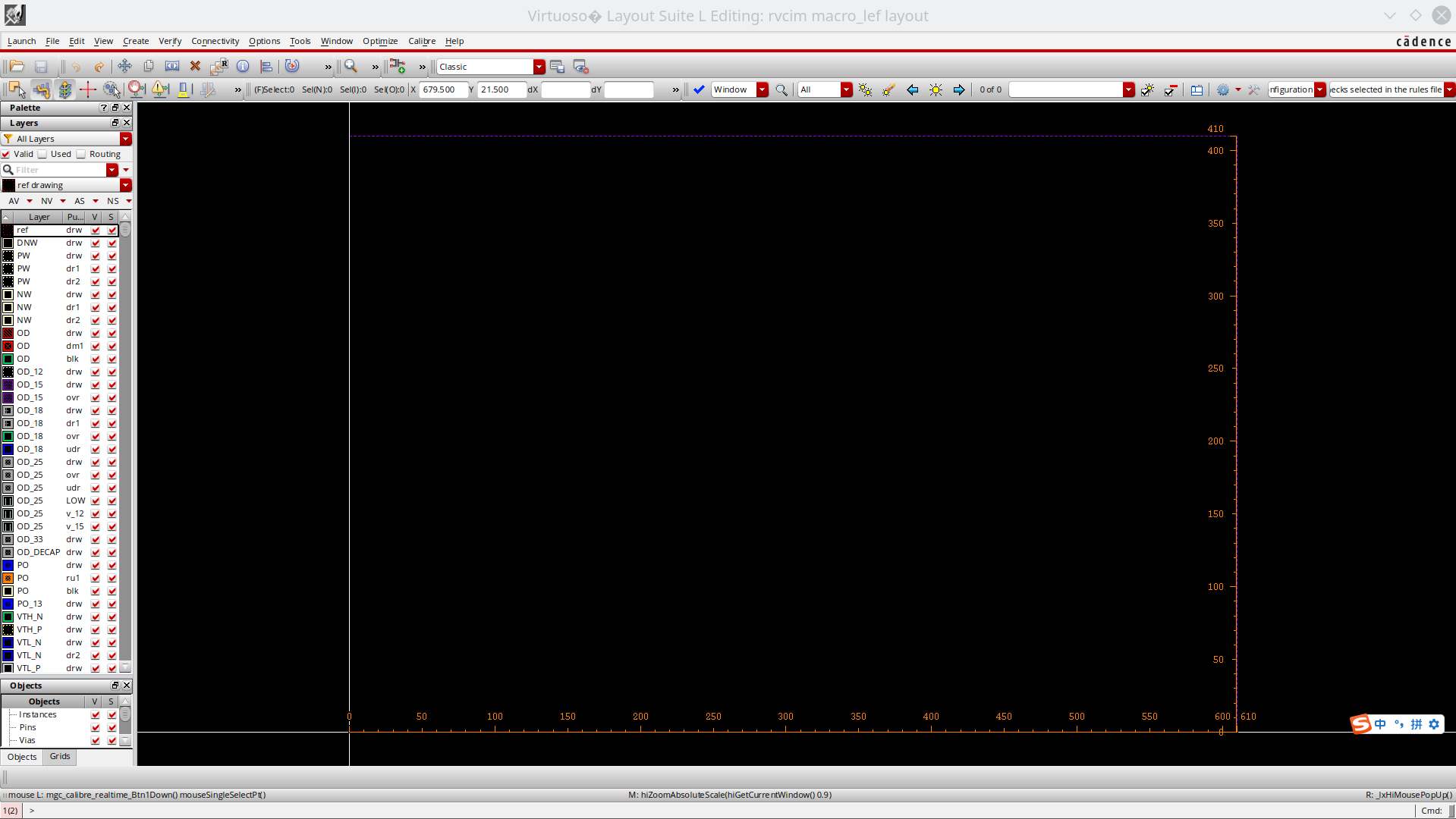

第一步先新建一个layout view,选择Create->P&R objects->P&R Boundry,根据约定的形状拉一个pr boundry出来,左下角放在0,0坐标。

可以先create两个ruler把长宽位置定好(不规则几何形状这里不讨论,一般也不要把macro搞成不规则形状)

第二步是拉线,我这里没有直接用create_pin的方法,稍微绕了点路,但是应该会更好一些。先create wire,如果是单独的线就Create->Wring->Wire,如果是总线就Create->Wiring->Bus。也可以直接快捷键p&F3或者ctrl+shift+x&F3。拉线前先在LSW里面选到要出pin的layer,比如m3,m4这些,确定之前记得和模拟那边check走线layer和方向的问题,比如我们这里奇数层走竖线,偶数层走横线,那么竖向出线的部分就要放在奇数层,横向出线的则放到偶数层。

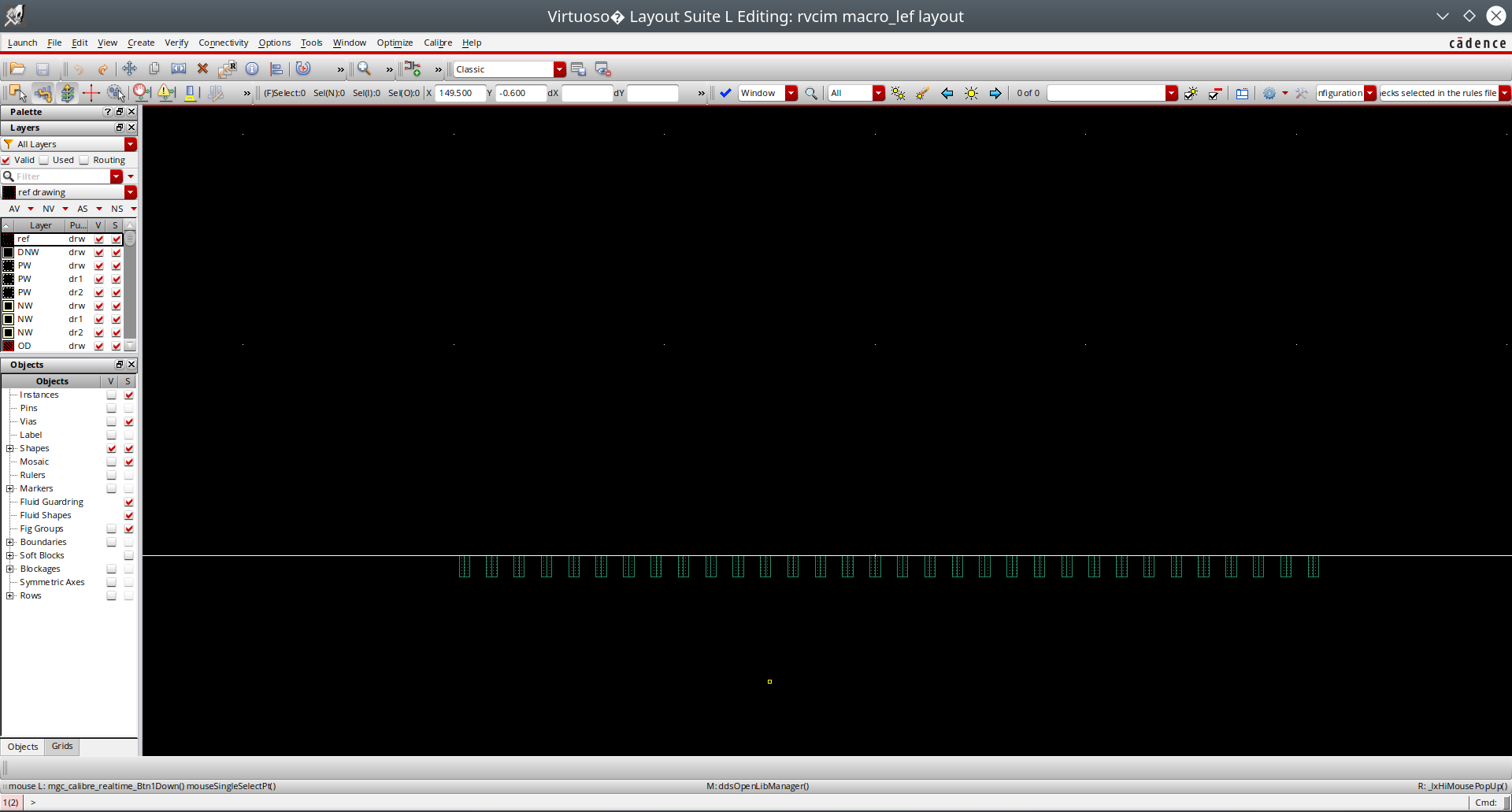

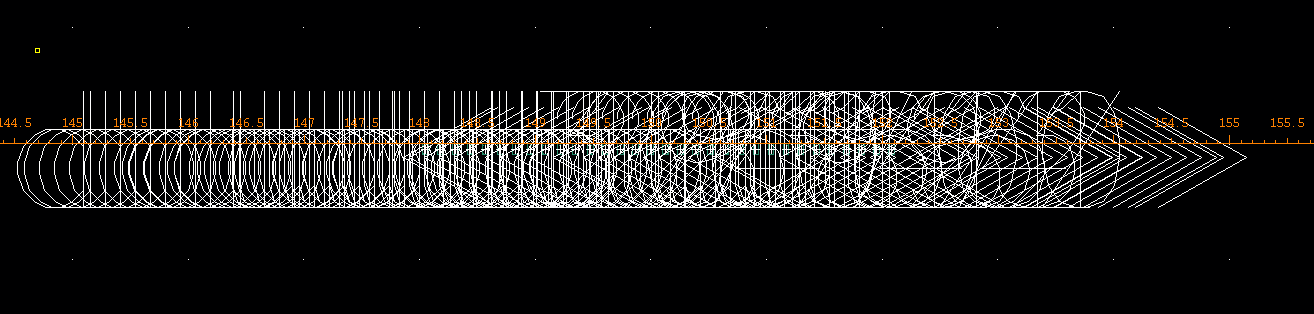

比如这里的dout<31:0>就是用create bus的方式产生的,ctrl+shift+x后再按F3,就会编辑bus的属性,Net Name就填dout<31:0>就行,点到别的格子里面之后就会自动展开成独立的线,下面的Number of Bits也会自动修改好。然后All Nets Width和All Nets Bit Spacing根据自己需要的线宽线距设定好,就能拉一组总线出来。注意这里没有Layer可以选,会直接生成在LSW中选的Layer。

然后把这组总线选个地方开始移动鼠标拉出来就行,拉到自己想要的长度后双击鼠标,bus就好了。

如果是生成单个wire的话,就p,然后直接拉线,然后和Bus一样F3设定属性,改好Net Name和Width,拉完之后双击。

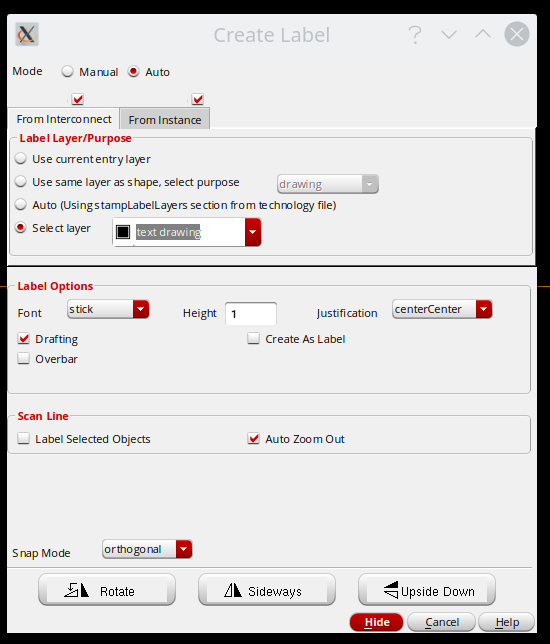

第三步是加label,Create->Label,然后改一下属性(如果没有出窗口就按一下F3),Mode选到Auto,Select layer选到需要的text的layer。

然后选中之前画好的线的bus,Create->Label,就会自动生成和之前的Net Name同名的Label,这样就都打好了。

这样把所有的bus和wire全部搞定。

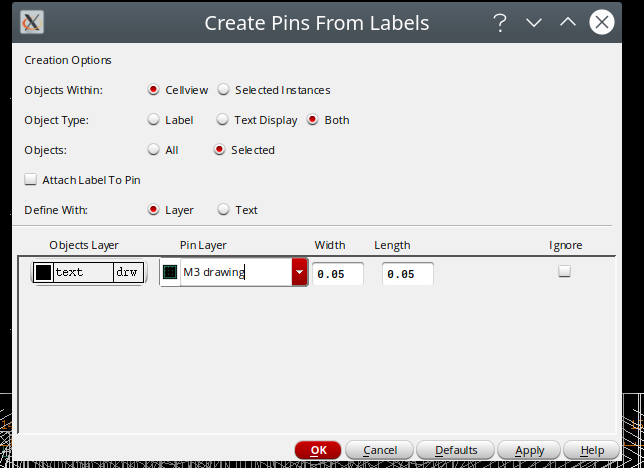

第四步是打pin,选中上一步中生成好的label,再使用Tools->Create Pins from Labels。Objects选成Selected,PinLayer改成要打pin的目标layer,然后点击OK。

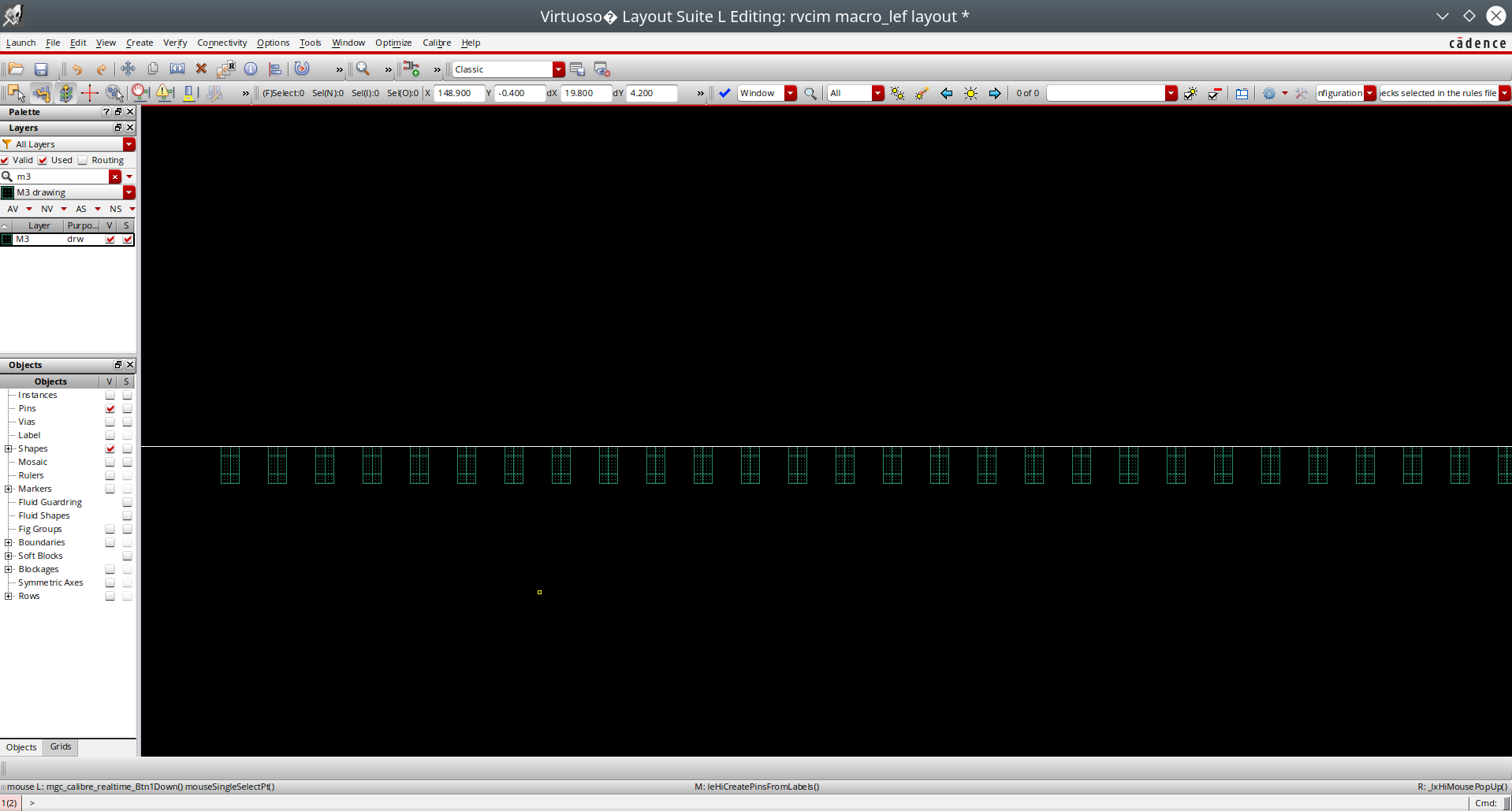

可以看到原来的线上多出了小方块,就是打上的pin。

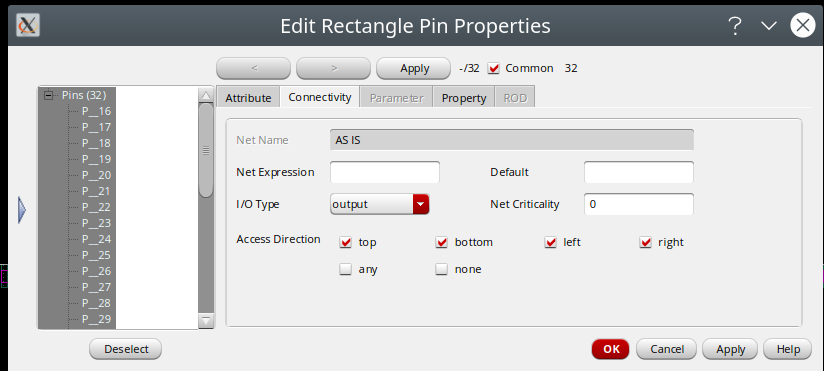

接着就是修改一下pin的direction,和.lib里面的声明对齐。选中所有pin,按q出属性界面,点击Common,能够编辑所有选中的pin的属性。I/O Type改为对应的direction即可。

至此一个layout的frame就好了。

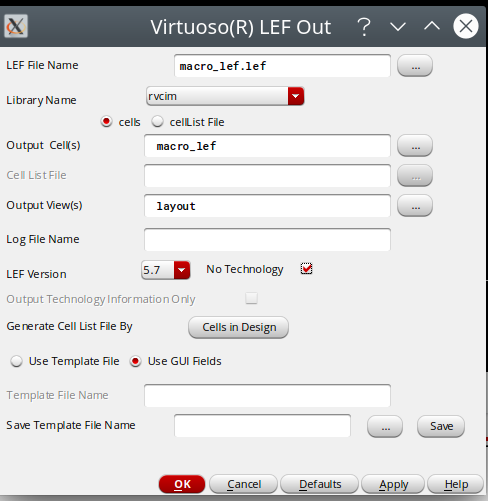

最后一步从这个gds中导出lef,在virtuoso启动处,选择File->Export->LEF。LEF File Name填写生成的lef文件的名字,Library Name,Output Cells,Output Views一步一步选中刚才画好的layout,然后一定要勾选No Technology,不需要带工艺LEF。

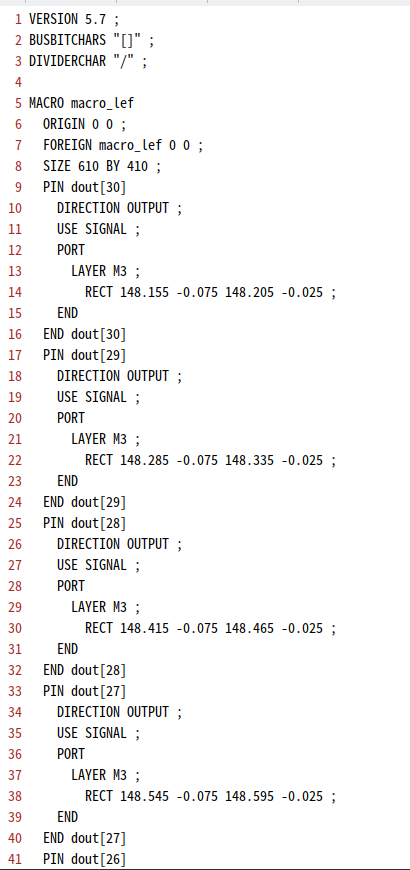

点OK后顺利的话,一会LEF文件就生成好了:

可以再对着layout核对一下LEF的信息。至此做LEF的flow结束。

补两个后续发现的tips:第一点是pin的间距可以设大,不然容易congestion,我这里28nm最后给了0.4um间距。第二点事pin的位置不能乱放,我这里都延伸到prboundry外部去了,正确的操作应该放在prboundry内部,并且pin的位置应该紧贴prboundry。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具