模拟集成电路设计系列博客——4.4.3 频率修调

4.4.3 频率修调

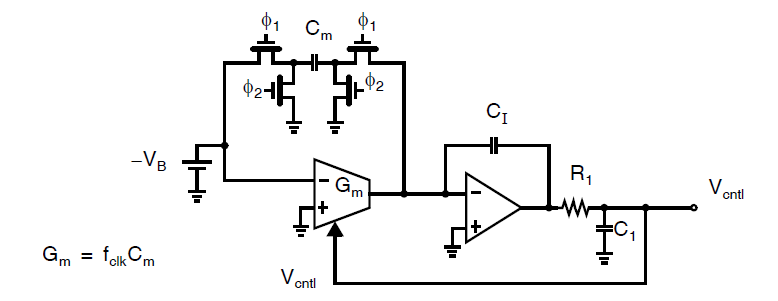

如果有精确的时钟的话,那么可以精确的修调\(G_m/C_A\)。例如,假设设计者有一个精确的时钟频率,称为\(f_{clk}\),那么一种使用开关电容电路进行修调的方式如下图所示[Viswanathan,1982]:

这个修调电路与我们上一节介绍的固定跨导修调电路很像,除了外部电阻被更换为了一个开关电容的等效电阻。开关电容的等效阻抗可以被写为\(R_{eq}=1/(f_{clk}C_m)\),因此跨导值\(G_m\)被设置为\(f_{clk}C_m\)。通过这种方式,\(G_m/C_A\)可以被精确的设置到\(f_{clk}C_m/C_A\)。因此可以不通过任何额外的元件实现精确的频率修调。此外一个额外的低通滤波器\(R_1C_1\)被添加在电路中来滤除开关电容引入的高频波动噪声。需要被注意的是,由于这个方法需要一个时钟信号,有很大的概率是时钟信号会漏到连续时间滤波器中,有可能会通过跨导器控制信号,或者是芯片衬底。

使用这种开关电容修调的一个困难是如果想要一个高频的滤波器,那么就需要一个很大的跨导比例(因此匹配会更差)。例如,考虑100MHz的滤波器,其中\(G_m/C_A\)被设置为\(2\pi \times 100MHz\)。如果电容值\(C_A\)被设置为\(1pF\),那么跨导\(G_m=2\pi \times 10^{-4}V/A\)。因此,假定上图中\(C_m=1pF\),我们需要开关电容的时钟驱动信号频率为:

一眼看上去,设计者可能会考虑通过增大\(C_m\)来减小时钟频率,然而,尽管\(f_{clk}\)得到了减小,由于\(C_m\)变得更大了,建立时间需求变得更难满足了。另一种减小\(f_{clk}\)的方式是让修调电路设置一个更小的跨导值,即\(0.1G_m\)。通过这种方式\(f_{clk}\)可以建校时被,但是滤波器的跨导值必须十倍大于修调电路跨导。因此滤波器和修调电路之间的匹配会更差,导致滤波器的频率精度降低。

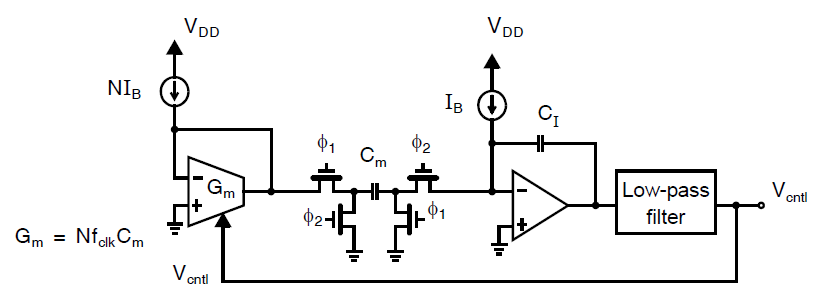

另一种降低开关电容修调电路时钟频率的方式是时钟两个缩放电流源,如下图所示[SilvaMartinez,1992]:

利用开关电容电路\(-1/f_{clk}C_m\)的等效阻抗,并注意到二极管接法的跨导器等效于一个值为\(1/G_m\)的电阻,设计者可以发现但流入积分器的平均电流为零时,跨导值为:

因此时钟频率相比之前的电路可以降低N倍。这个电路用于修调一个\(10.7MHz\)的带通滤波器时,使用\(N=148\),那么时钟频率就仅仅需要\(450KHz\)。低通滤波器同样通过开关电容电路和一个片外电容来实现。

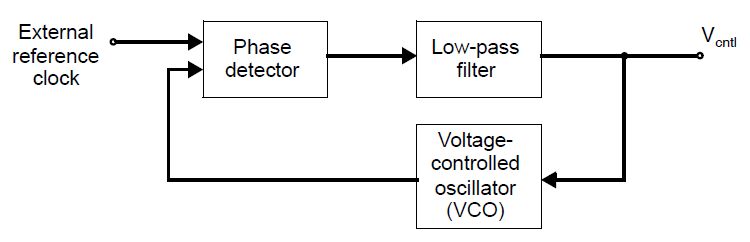

另一种实现频率修调的方式是使用锁相环(PLL),如下图所示[Tan,1978]:

此处,两个连续时间积分器被放置在一个环路中来实现锁相环路中的压控振荡器(VCO)。在电路启动之后,锁相环的负反馈使得VCO的频率和相位锁定在外部参考时钟。一旦VCO的输出锁定在外部参考信号上,VCO的\(G_m/C\)就被设置在一个预期的值上,控制电压\(V_{cntl}\)可以用于修调积分滤波器。需要注意的是,选择外部参考时钟时需要进行trade-off,因为它同时影响修调进度和漏入主滤波器的修调信号。具体来说,为了实现修调电路和主滤波器的最佳匹配,最好选择等于滤波器通带上限边缘的频率。但是主滤波器的噪声增益一般在通带上限边缘时最大,因此漏入主滤波器输出的参考信号也会很严重。当参考时钟频率离开通带上边缘时,匹配变得更差,但是增加了对参考信号漏入的抵抗能力。另一个使用这种方式的问题是,除非对VCO施加对电源变化不敏感的电压控制信号,否则任何电源上的噪声也会注入到控制信号\(V_{cntl}\)。

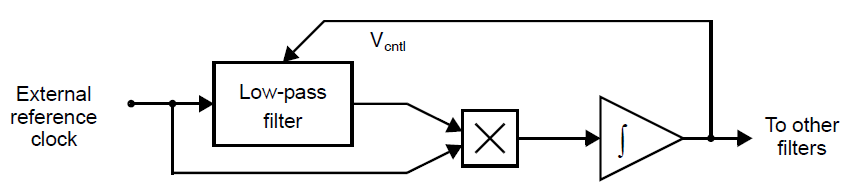

此外,还有一种类似的方式是基于锁定于固定频率输入的跟踪滤波器[Khorramabadi,1984]。这种方式对电源噪声相对不敏感。跟踪滤波器的控制电压被用于调整实际系统中的跨导器,假定跟踪滤波器中的跨导器匹配实际系统中的跨导器。一个这种修调电路的例子如下图所示:

当低通滤波器和外部参考时钟有着相同的谐振频率时,其固定有90度的相移。因此,其输入和输出的相关性为零。如果频率不同,那么乘法器和积分器的相关性非零。从积分器输出到滤波器控制电压的负反馈驱动谐振频率来使得两个频率相等。在完成锁定之后,相同的控制电压可以提供给其他滤波器。其他滤波器可以被修调到已知的时间常数上,假定他们与控制环路中的滤波器匹配。

一个重要的问题是环路中的滤波器需要有很低的时间常数来滤除乘法器输出的两倍于外部参考频率的分量。否则这个分量会导致时钟泄漏到其他被修调的滤波器中。一个这种原理的电路的变种将带阻滤波器和低通滤波器的输出的其中一个获得控制电压时(通过同样的二阶获得)的相关性驱动到零[Kwan,1991]。这种方式在两倍外部参考时钟处有更少的信号分量,并且不需要环路中的滤波器有一个大的时间常数,这使得这种方法更容易在没有外部元件时集成。同时,环路对于相位误差的敏感度更低。其总算能收敛到带阻频率,即使低通和带阻的输出之间的相位差并不是准确的90度。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具