DesignWareBuildingBlock IP的仿真与综合

感谢一下同学的协助,跑通了一个case。

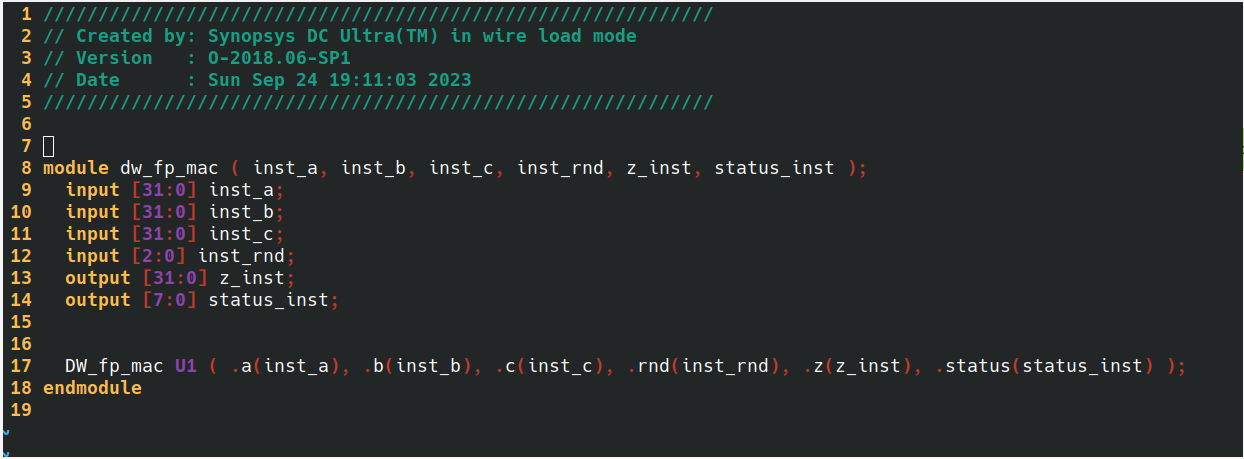

IP核调用 dw_fp_mac.sv

module dw_fp_mac( inst_a, inst_b, inst_c, inst_rnd, z_inst, status_inst );

parameter inst_sig_width = 23;

parameter inst_exp_width = 8;

parameter inst_ieee_compliance = 0;

input [inst_sig_width+inst_exp_width : 0] inst_a;

input [inst_sig_width+inst_exp_width : 0] inst_b;

input [inst_sig_width+inst_exp_width : 0] inst_c;

input [2 : 0] inst_rnd;

output [inst_sig_width+inst_exp_width : 0] z_inst;

output [7 : 0] status_inst;

// Instance of DW_fp_mac

DW_fp_mac #(inst_sig_width, inst_exp_width, inst_ieee_compliance) U1 (

.a(inst_a),

.b(inst_b),

.c(inst_c),

.rnd(inst_rnd),

.z(z_inst),

.status(status_inst) );

endmodule

需要在makefile里添加路径

SYNOPSYS = /home/synopsys/syn/O-2018.06-SP1

#start vcs compile

vcs_com:

cd ../work/vcs && vcs -sverilog -full64 +v2k -debug_pp -timescale=${TIMESCALE} -

cpp g++ -cc gcc -LDFLAGS -LDFLAGS -Wl,--no-as-needed -CFLAGS -fPIE -fsdb -f

../../prj/filelist.f -o ${OUTPUT} -l compile.log -y ${SYNOPSYS}/dw/sim_ver

+libext+.v+.inc +incdir+${SYNOPSYS}/dw/sim_ver

写了一个简单的tb

`timescale 1ps/1ps

module tb_dw_fp_mac;

// Parameters for testbench

parameter inst_sig_width = 23;

parameter inst_exp_width = 8;

parameter inst_ieee_compliance = 0;

// Inputs and Outputs

logic [inst_sig_width+inst_exp_width : 0] inst_a;

logic [inst_sig_width+inst_exp_width : 0] inst_b;

logic [inst_sig_width+inst_exp_width : 0] inst_c;

logic [2 : 0] inst_rnd;

wire [inst_sig_width+inst_exp_width : 0] z_inst;

wire [7 : 0] status_inst;

// Instantiate DW_fp_mac_inst

dw_fp_mac UUT (

.inst_a(inst_a),

.inst_b(inst_b),

.inst_c(inst_c),

.inst_rnd(inst_rnd),

.z_inst(z_inst),

.status_inst(status_inst)

);

task dump_output();

$dumpfile("out.vcd");

$dumpvars(0, tb_dw_fp_mac);

$fsdbDumpfile("tb_dw_fp_mac.fsdb"); //指定生成的的fsdb

$fsdbDumpvars("+all");//$fsdbDumpvars(0,tb_mesh);

//0表示生成u_rec_intra_top模 块及以下所有的仿真数据

$vcdpluson;

//下面这两个是保存所有仿真数据

$vcdplusmemon;

endtask

// Clock generation

logic clk = 0;

always #5 clk = ~clk;

// Reset generation

logic rst = 0;

initial begin

rst = 1;

#10 rst = 0;

end

// Test cases

initial begin

dump_output();

// Test case 1: Multiplication

inst_a = 32'h3F800000; // 1.0

inst_b = 32'h40000000; // 2.0

inst_c = 32'h3F000000; // 0.5

inst_rnd = 3'b000;

#20;

inst_a = 32'h40A9999A; // 5.3

inst_b = 32'h42C75EB8; // 99.685

inst_c = 32'h455C81FA; // 3528.123456 a*b+c = 7FFFFFFF (4,056.453956)

inst_rnd = 3'b000;

#20;

// Add more test cases here...

// Finish simulation

$finish;

end

// Monitor for displaying results

always_ff @(posedge clk) begin

$display("inst_a = %h, inst_b = %h, inst_c = %h, inst_rnd = %b, z_inst = %h,

status_inst = %h",

inst_a, inst_b, inst_c, inst_rnd, z_inst, status_inst);

end

endmodule

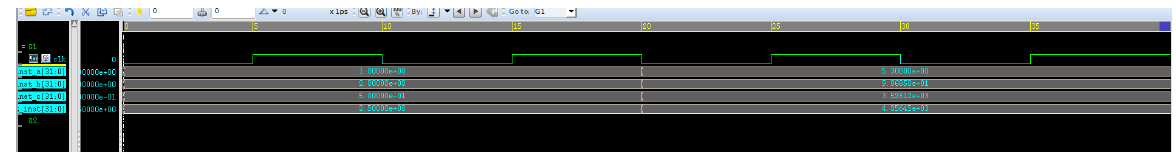

仿真结果

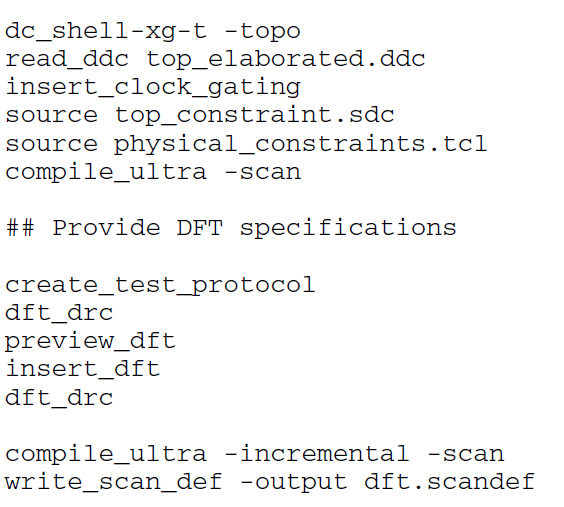

综合脚本:

set design_name "dw_fp_mac"

set stdcel_libs "

../../lib/logic/slow.db

"

set target_library "$stdcel_libs"

set synthetic_library "dw_foundation.sldb"

set link_library "* $target_library dw_foundation.sldb"

sh mkdir -p ./reports

sh mkdir -p ./outputs

set report_path "./reports"

set output_path "./outputs"

set_svf $output_path/${design_name}.svf

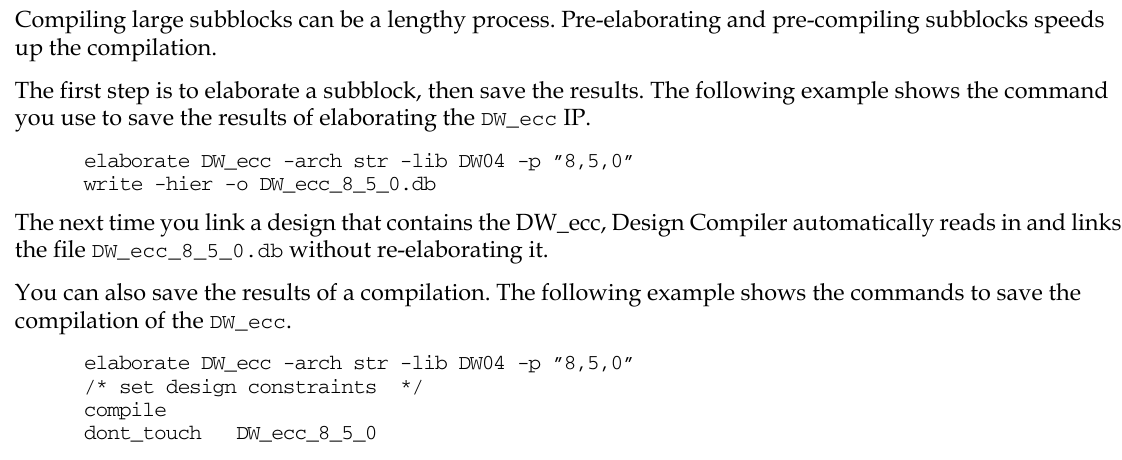

碰到的一个问题是最后吐出来的门级网表中没有IP的门级描述。

这样肯定是无法用于后端的。之前综合时使用的是compile_ultra -incremental命令,查阅DWBB的user_guide后发现:

于是在综合部分修改综合命令为compile:

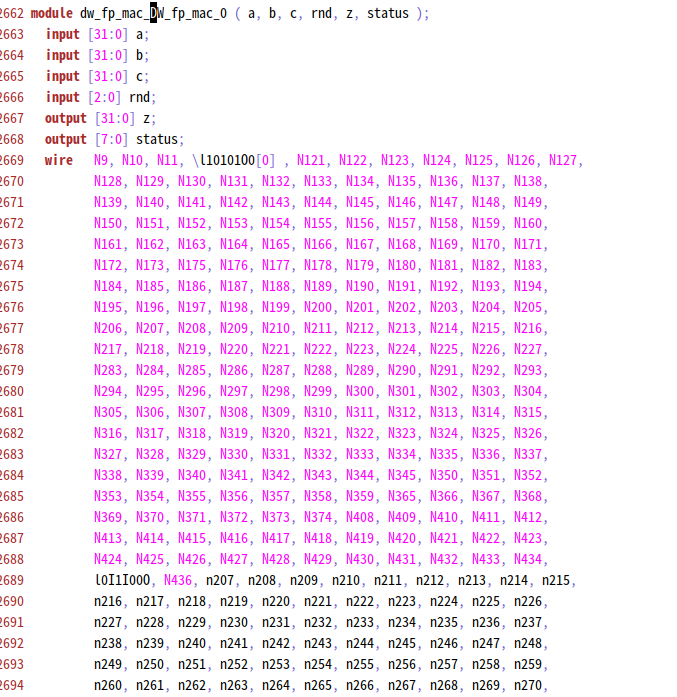

这样就产生了有门级描述的最终网表:

进一步试验后发现直接使用compile_ultra命令也可以,而且综合出的网表质量更高一些,只要去掉-incremental参数即可。-incremental代表进入增量工作模式,我们祖传脚本里就带了这个参数,但是一直没去细究含义,今天碰到这个坑了所以做个记录。

上面是dc user_guide里面的脚本例子,compile_ultra -incremental应该是在compile_ultra一次以后进行增量编译的操作。祖传脚本里却在没有前置的compile_ultra的情况下直接使用compile_ultra -incremental,在没有使用dw_foundation.sldb的情况下之前这样做没有碰到过问题,但是这次知道了实际上不可以的。

浙公网安备 33010602011771号

浙公网安备 33010602011771号