模拟集成电路实践记录_版图及DRC LVS

实验六,版图

6.1 实验背景

6.2 实验内容

- 搭建CMOS反相器原理图并仿真验证

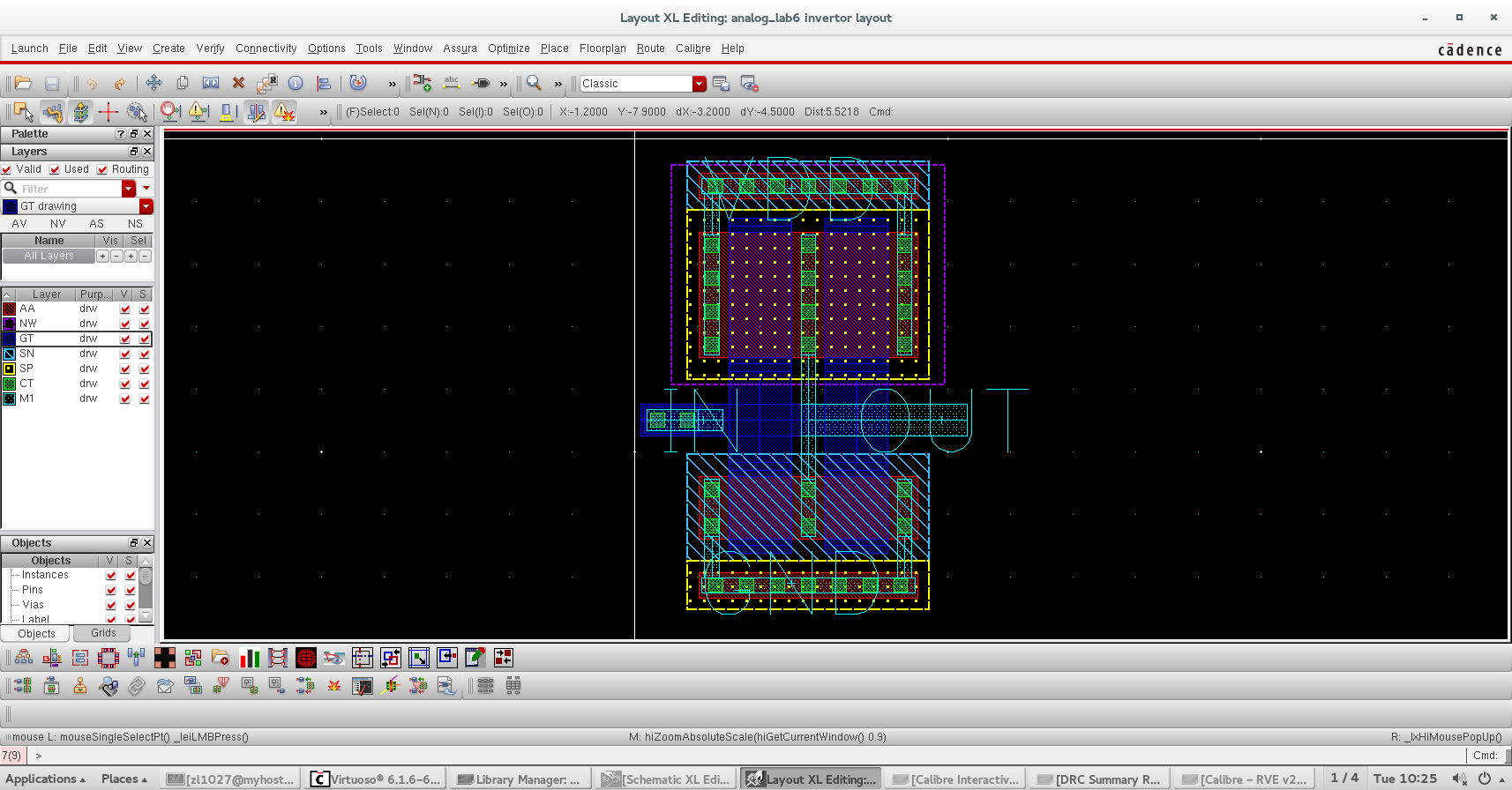

- 绘制反相器版图

- 进行DRC,LVS检查

6.3 实验过程

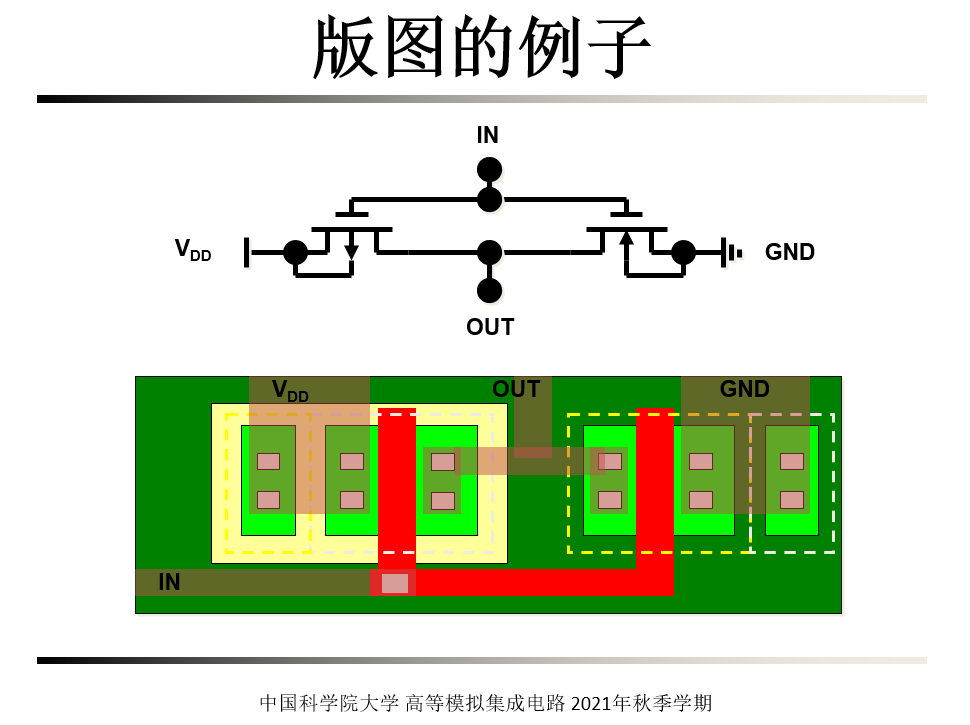

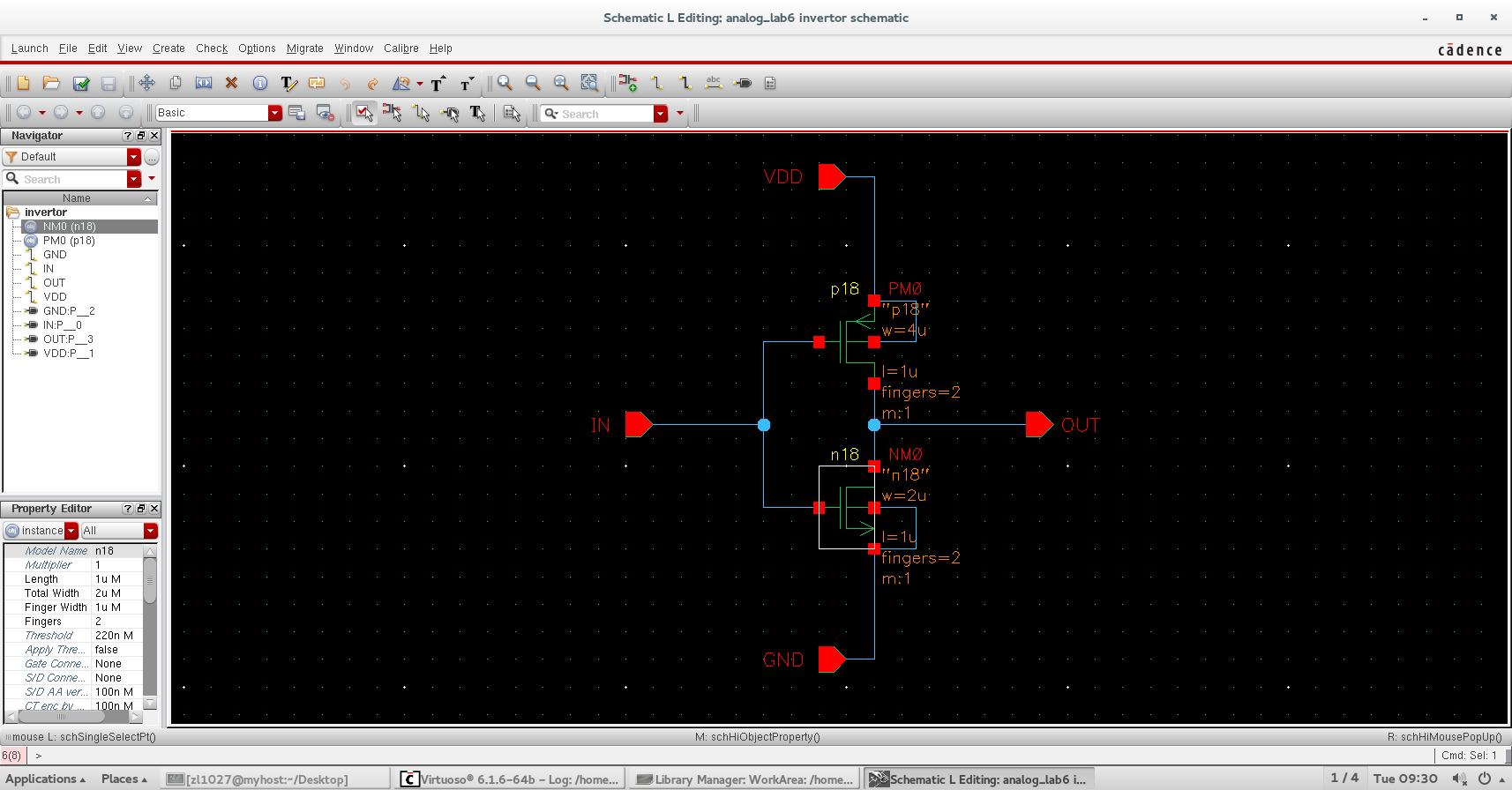

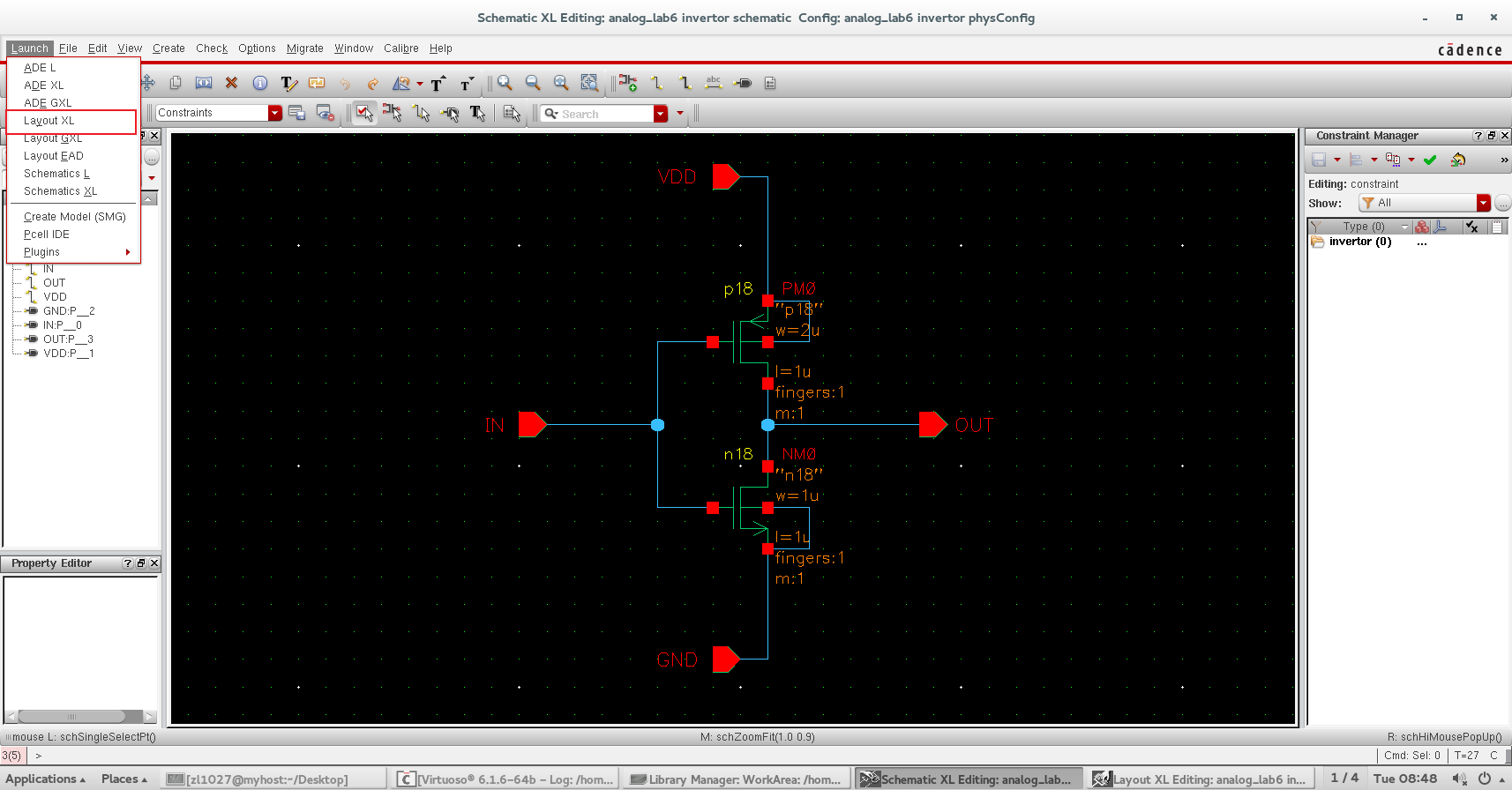

- 如下图所示绘制反相器原理图,NMOS设置W=2um,L=1um,finger=2,PMOS设置W=4um,L=1um,finger=2

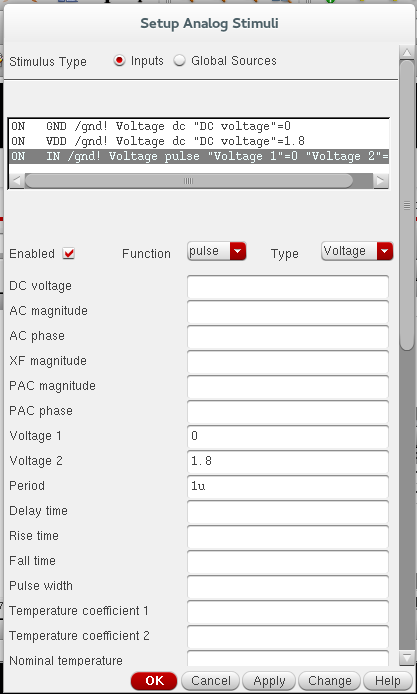

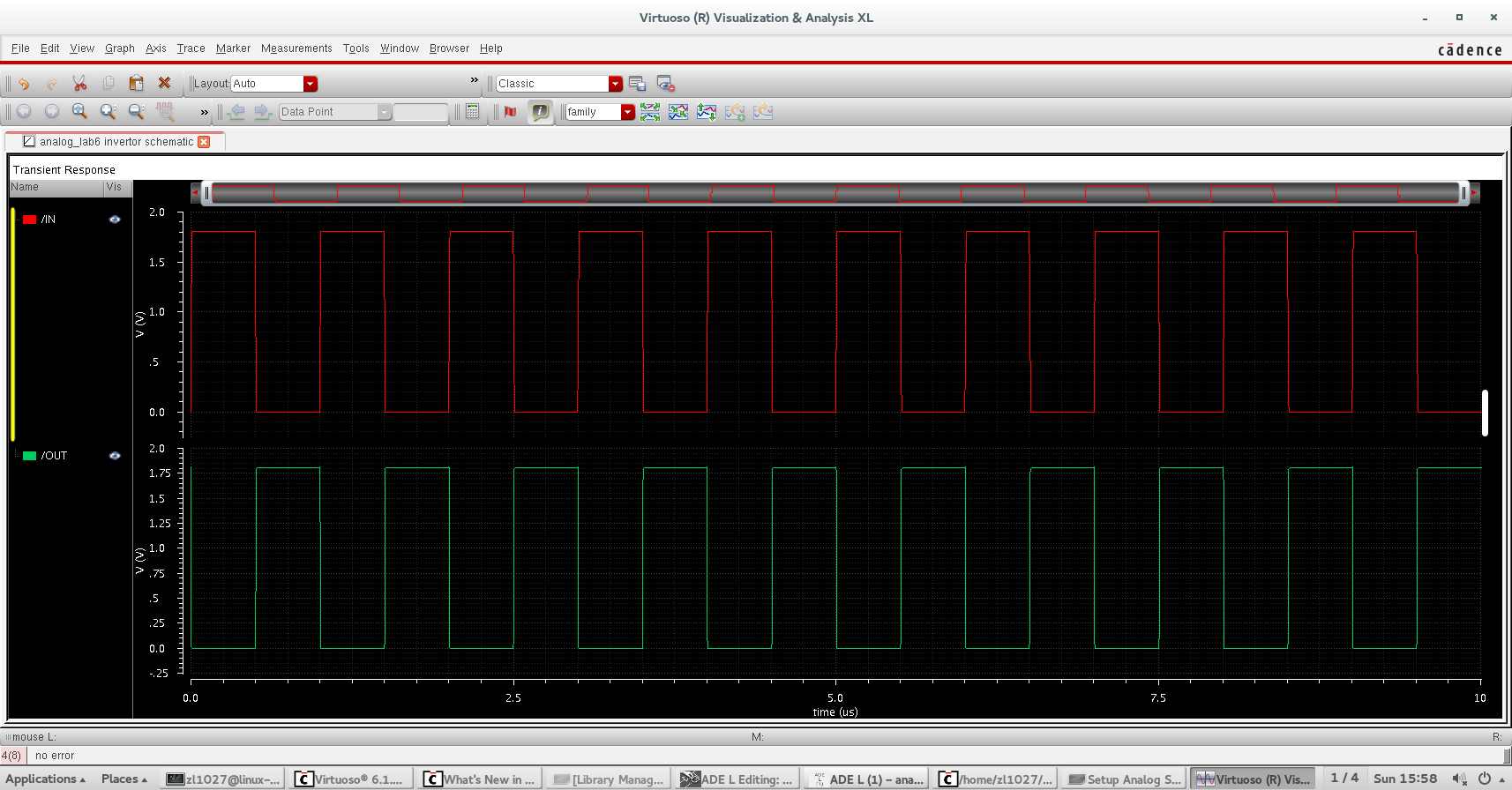

- 设置激励条件,进行瞬态仿真

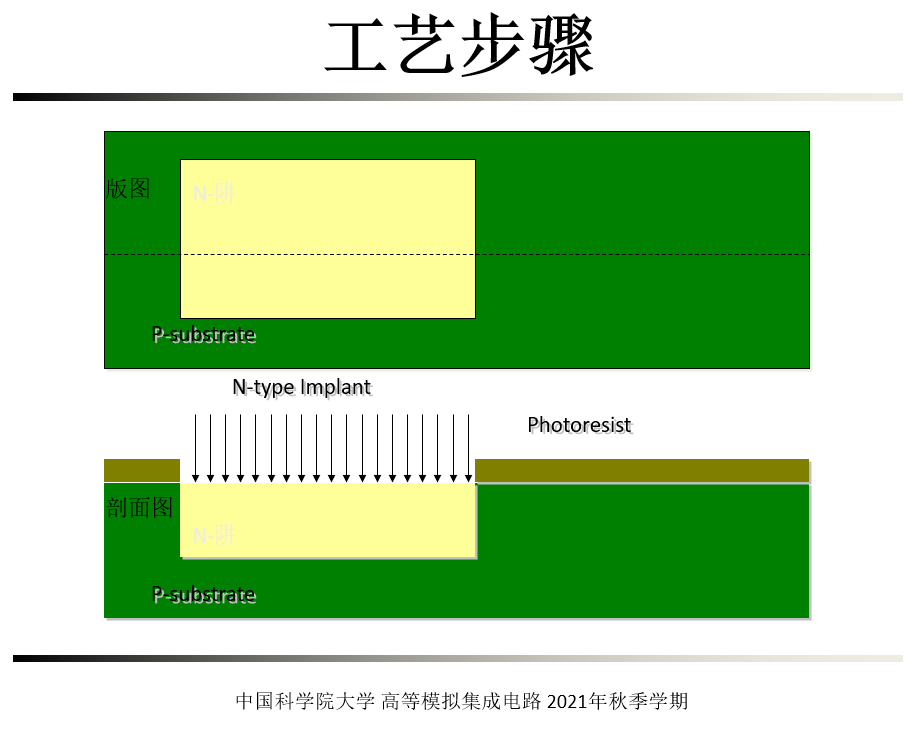

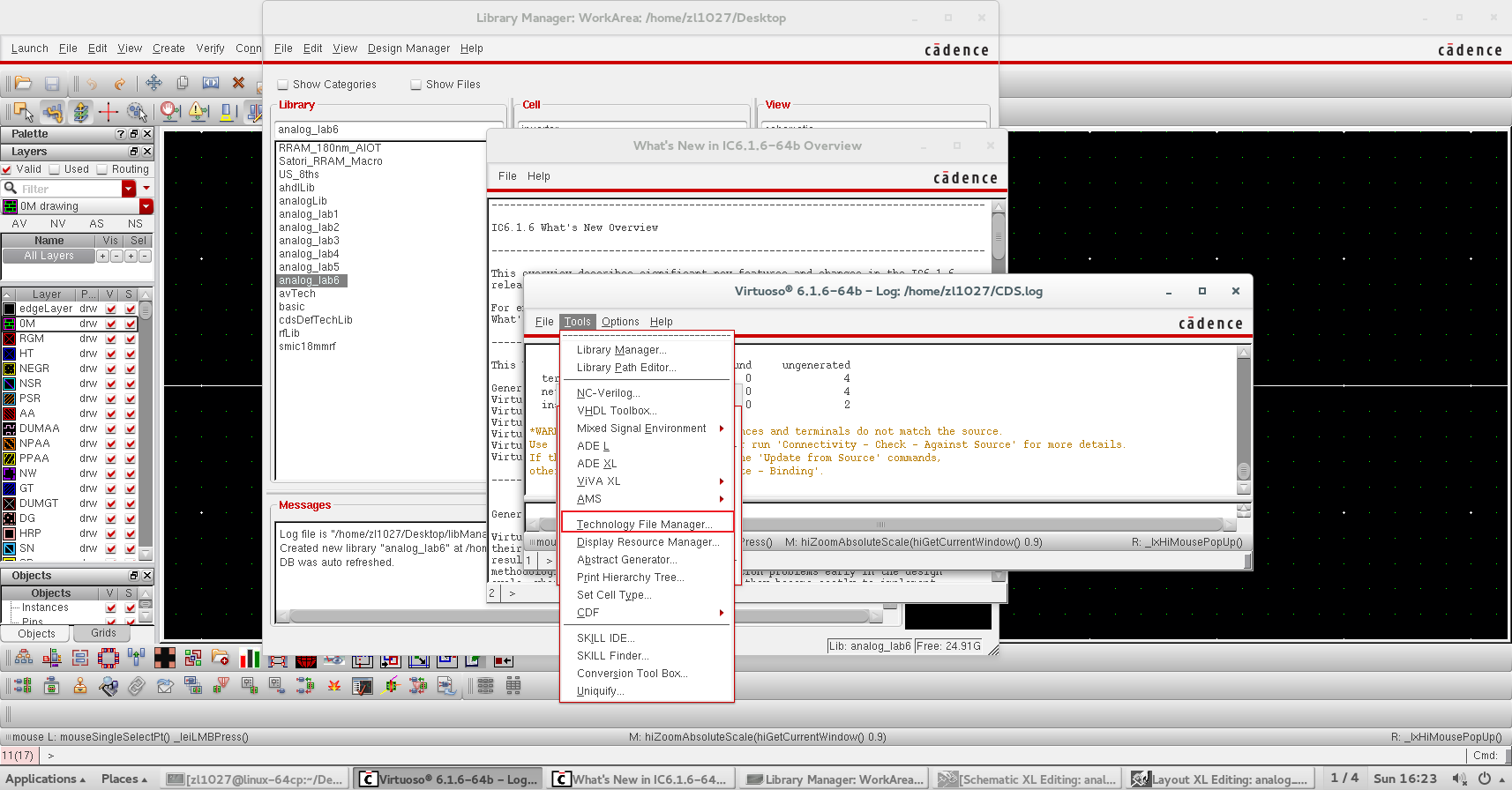

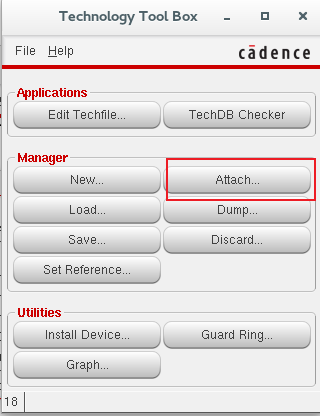

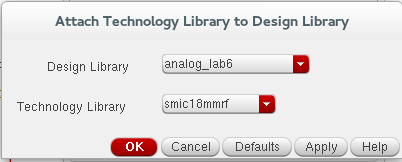

- 在做版图之前需要先把工艺库和Library进行attach,否则创建Layout时显示不出Layer

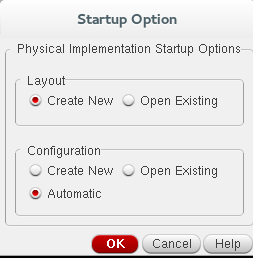

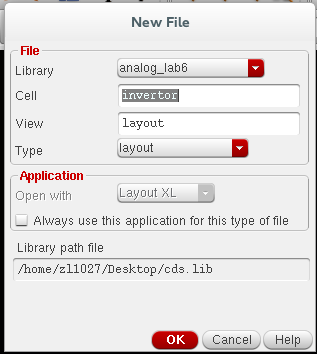

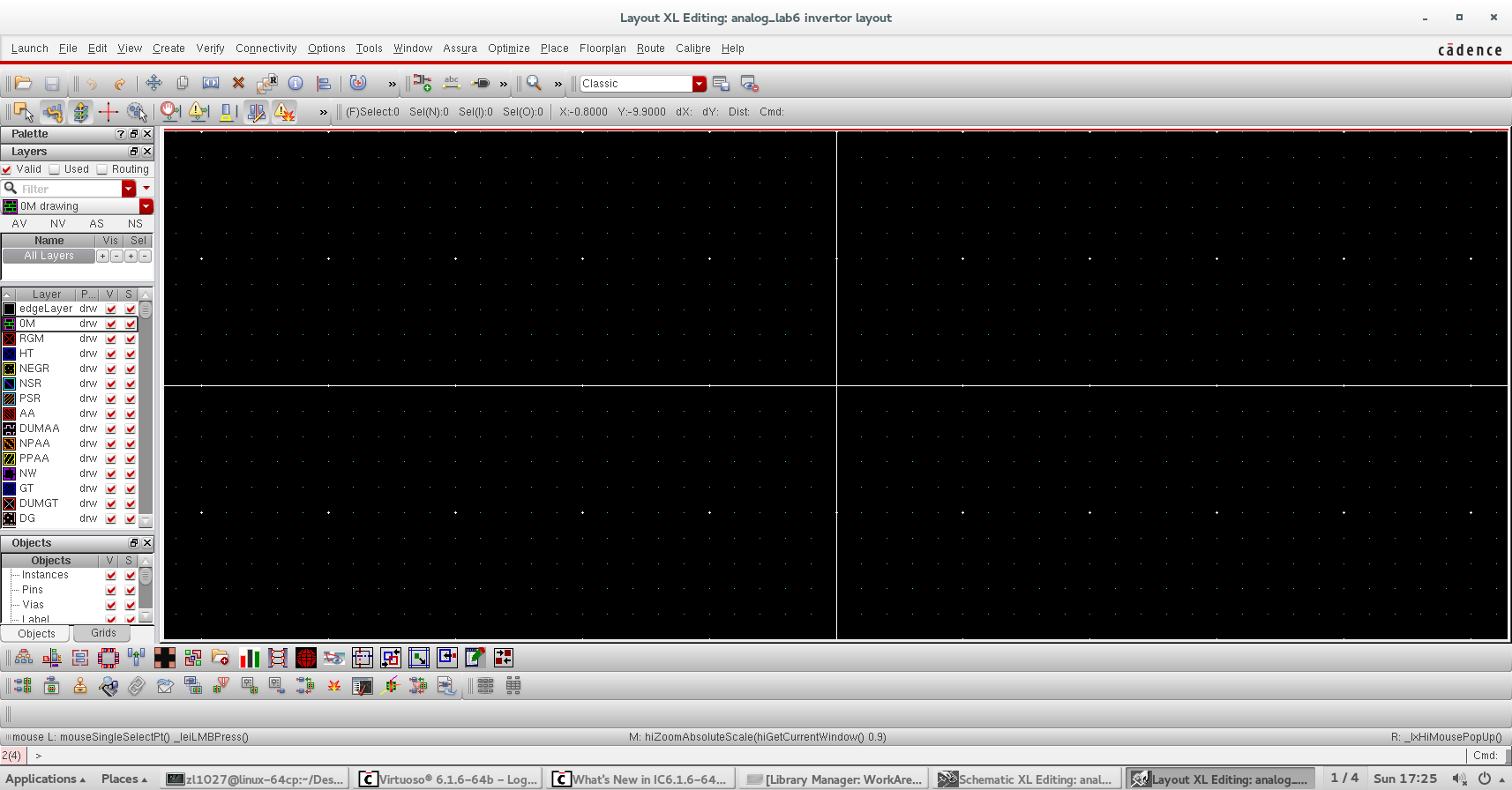

- 创建Layout

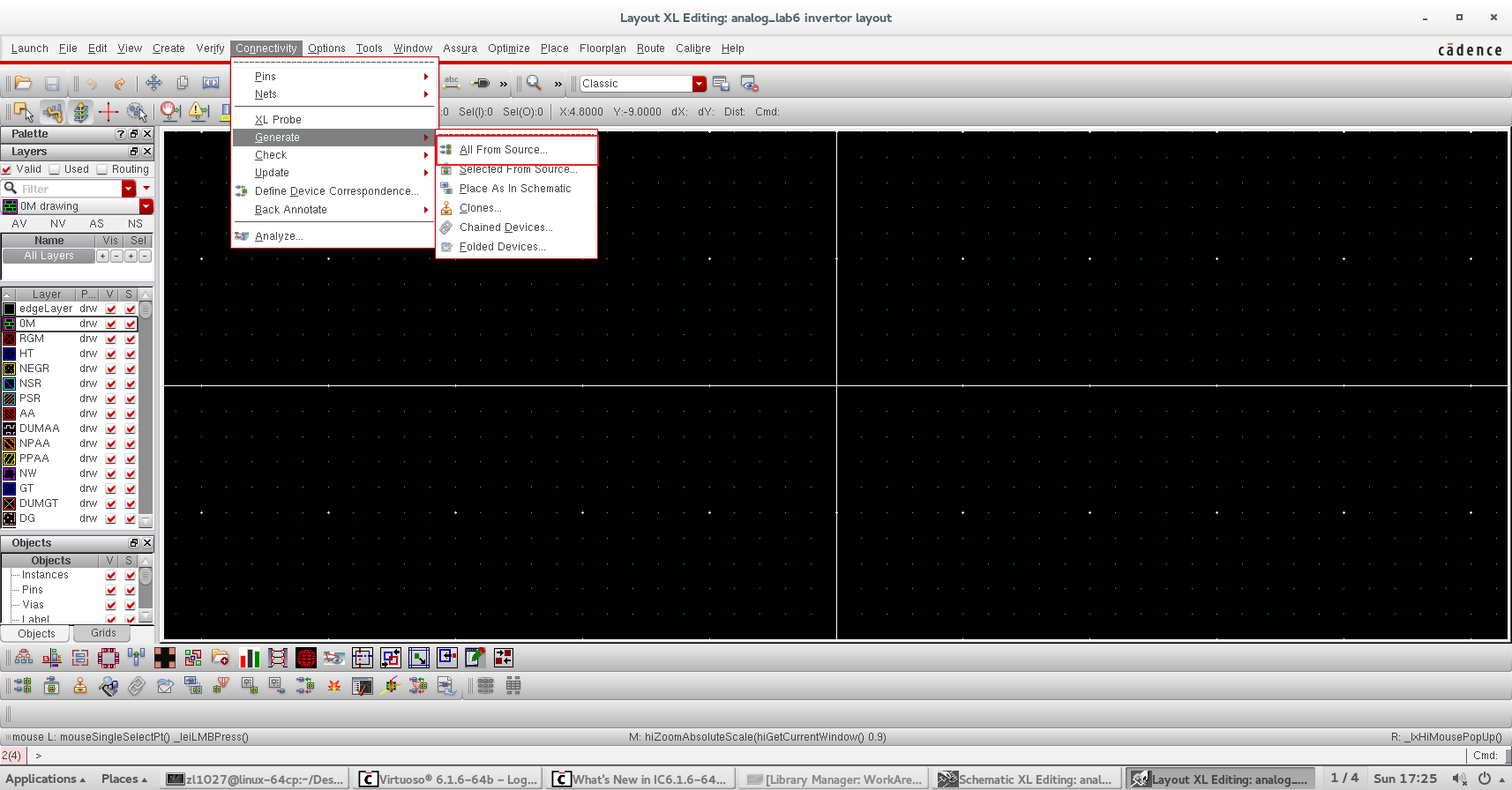

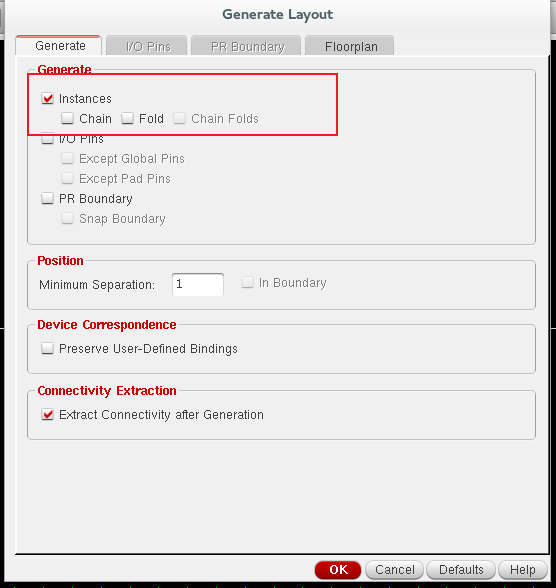

- 从原理图导入Instance

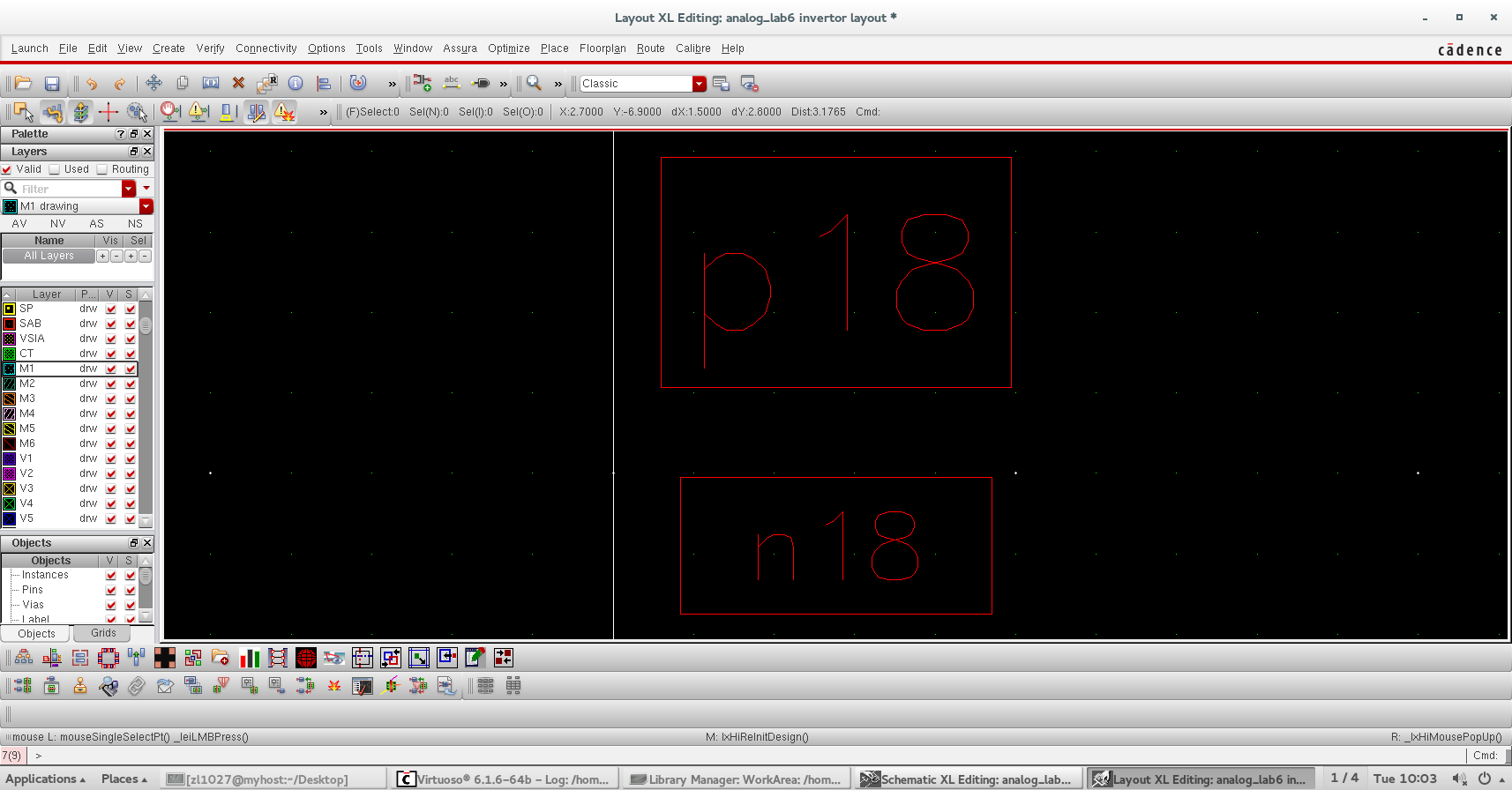

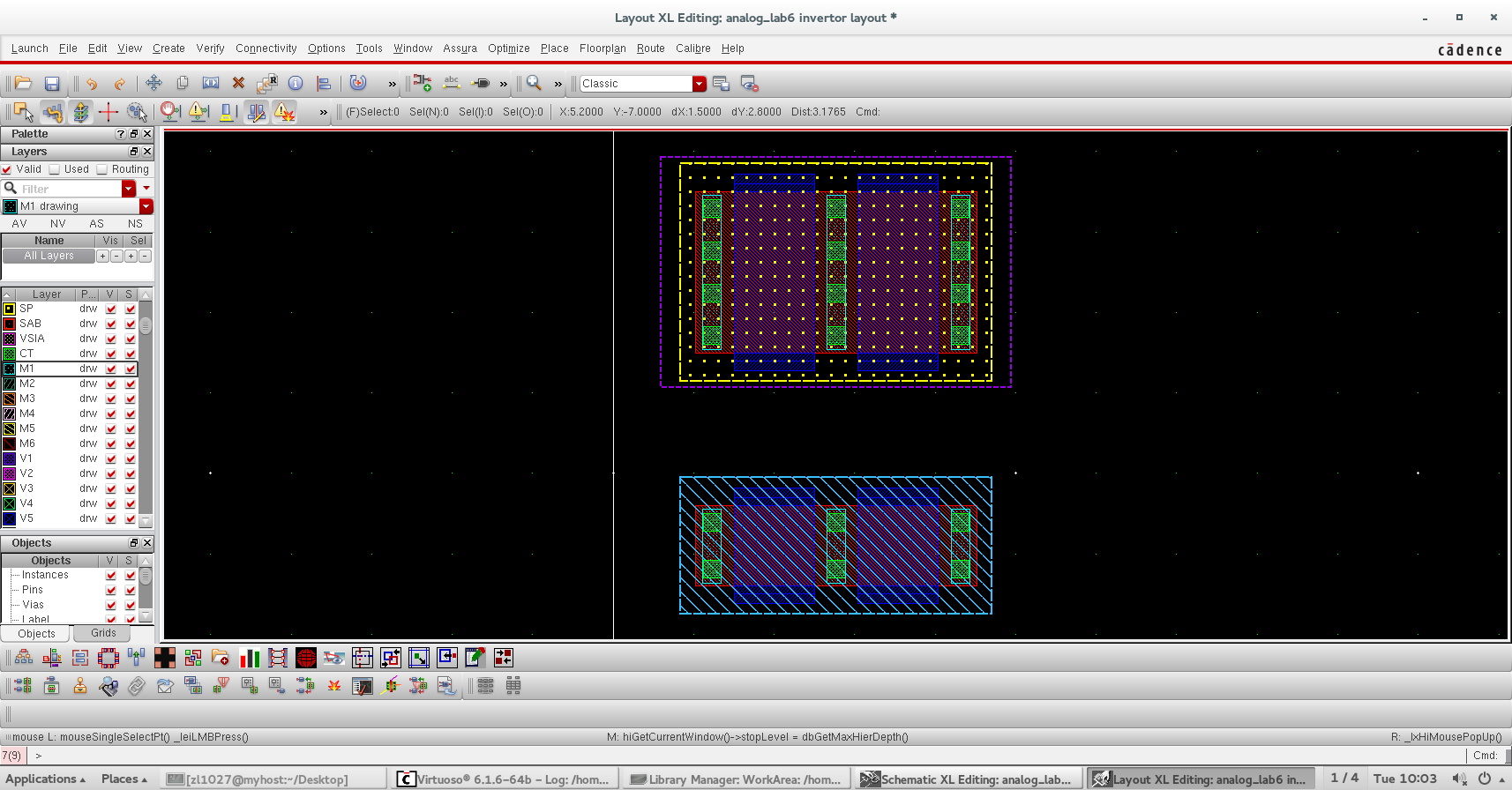

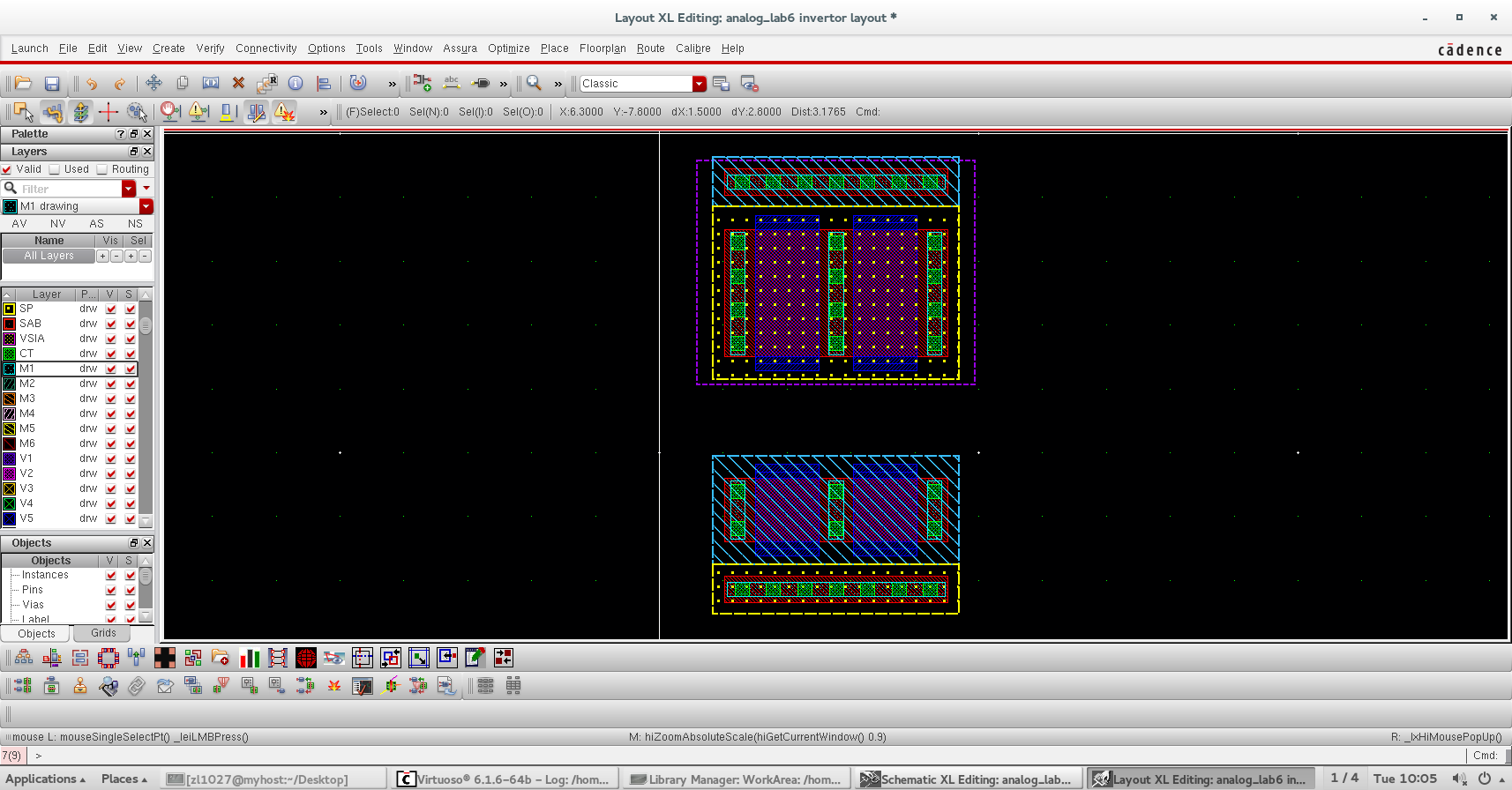

- 导入后的Instance如下图所示(只显示为红框符号),想要查看Layout需要通过Shift+F快捷键进行切换

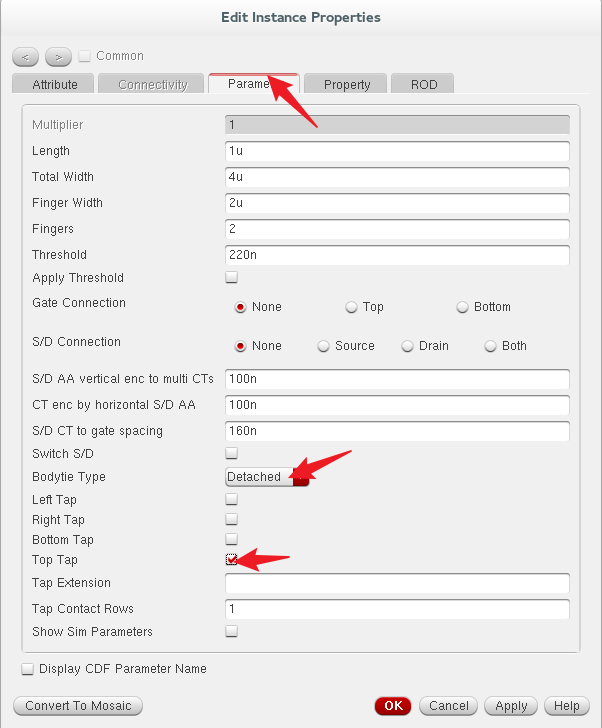

- 这里的NMOS和PMOS都没有显示B极,需要选中Instance后按q进行修改,可以设置衬底在Instance周围的位置(Left、Right、Bottom、Top)

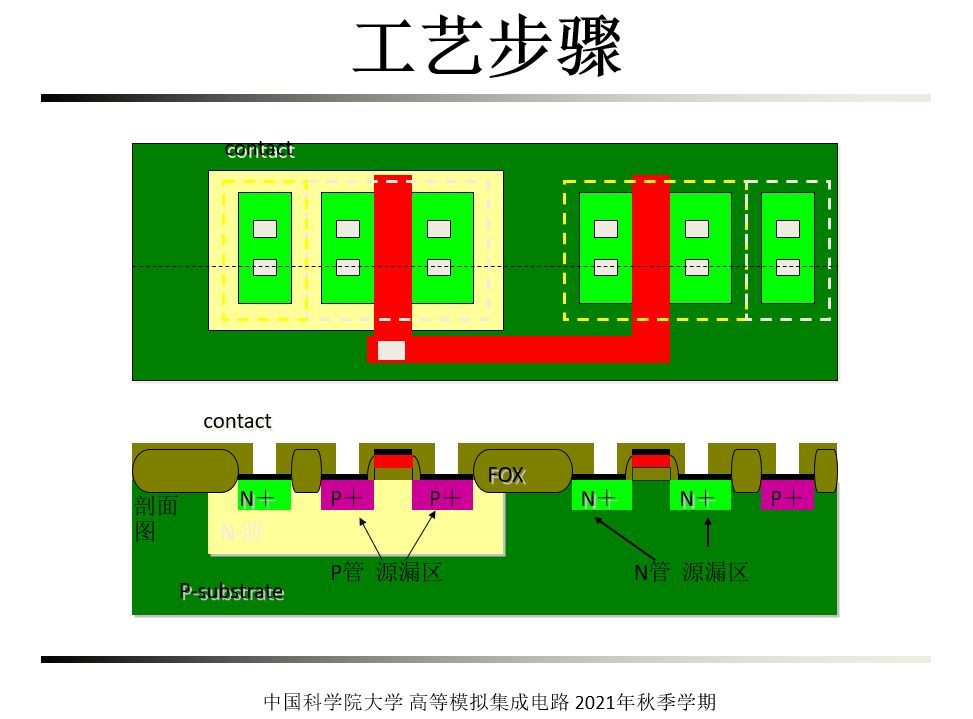

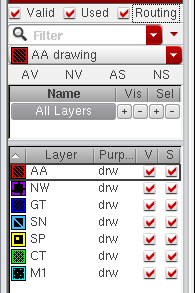

- 为了便于进行布线,在LSW界面中勾选Valid,Used,Routing选项,这样就只剩下了7个Layer,根据反相器的原理进行版图的绘制,并添加Label

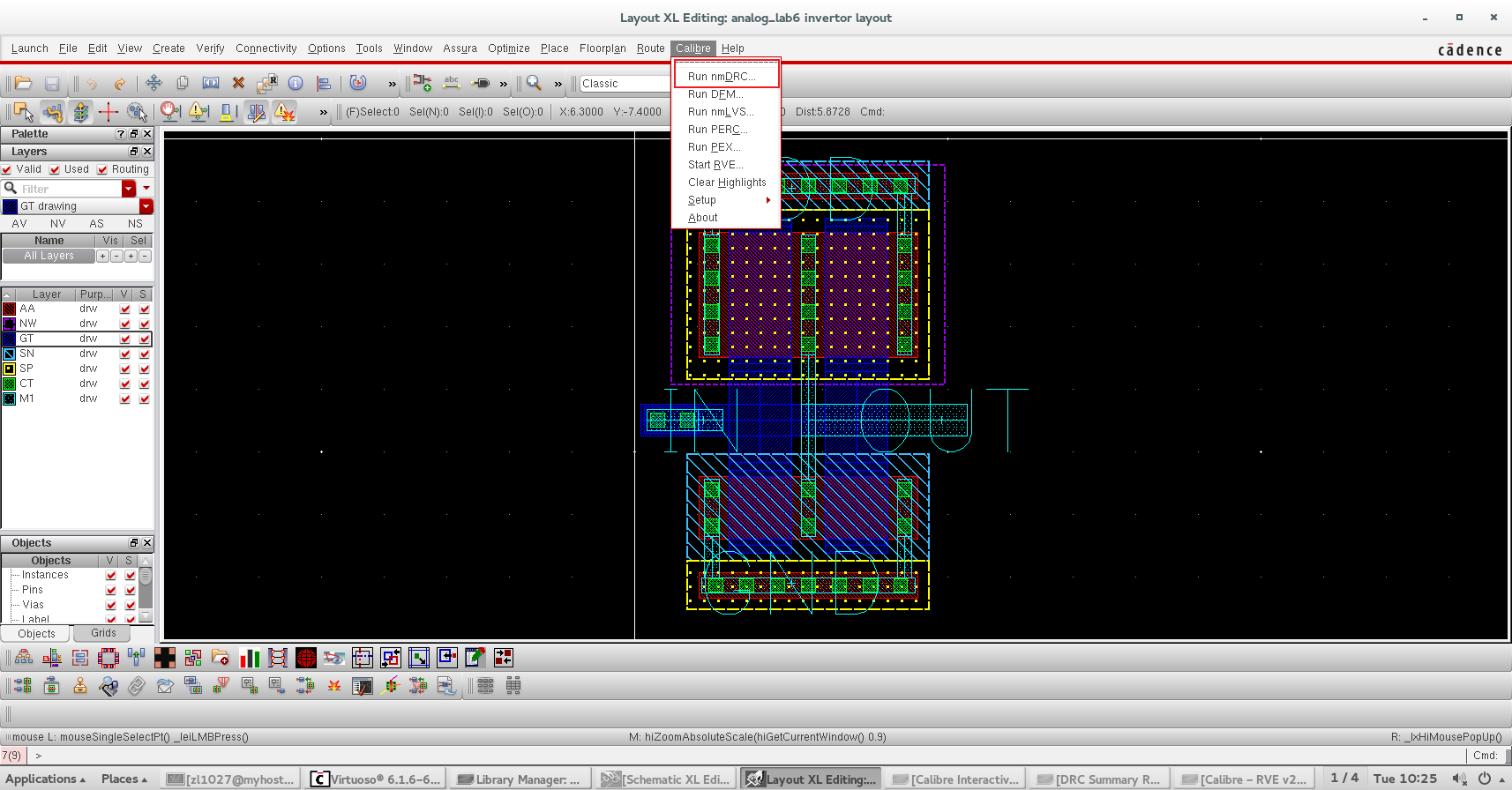

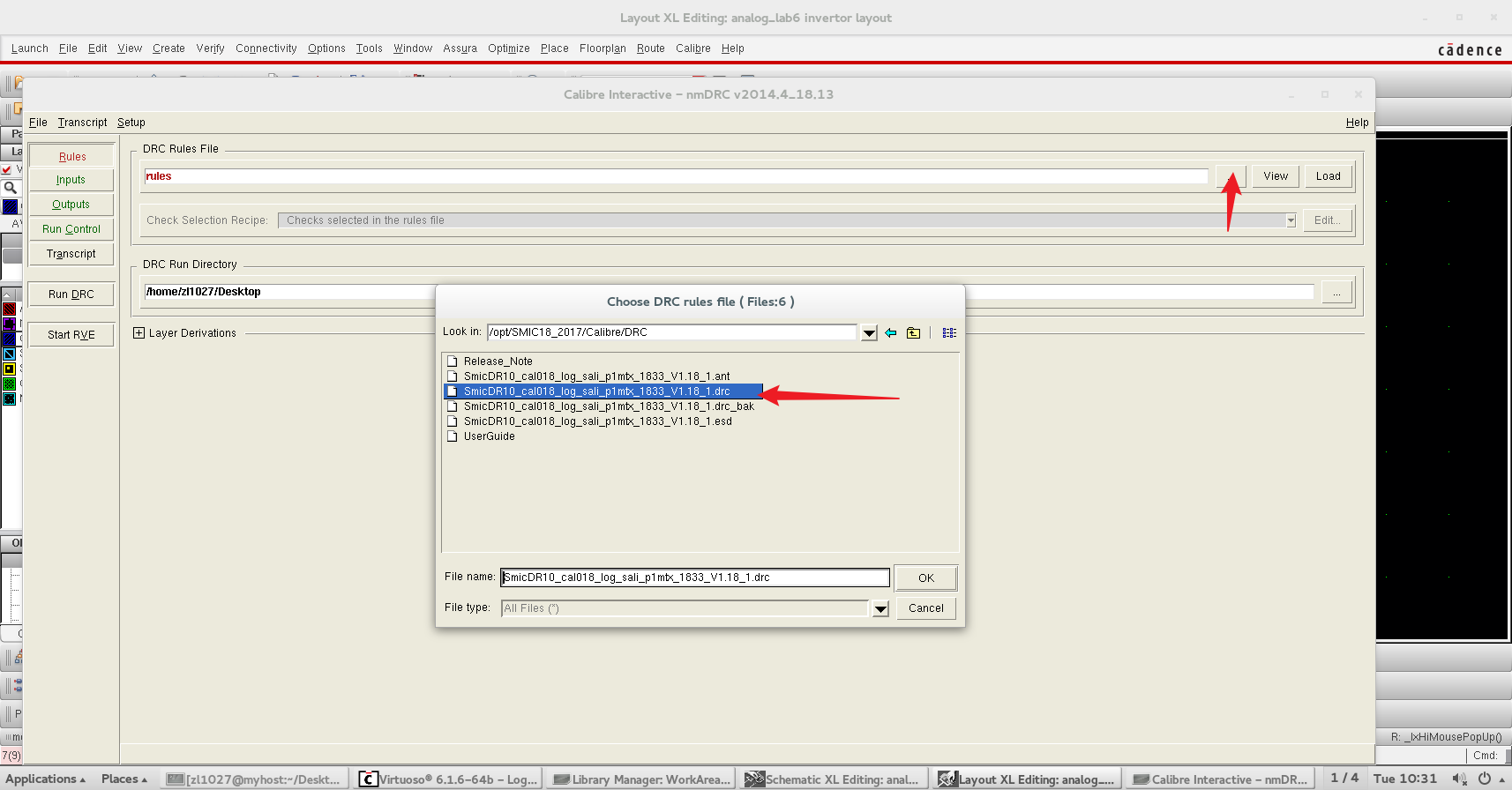

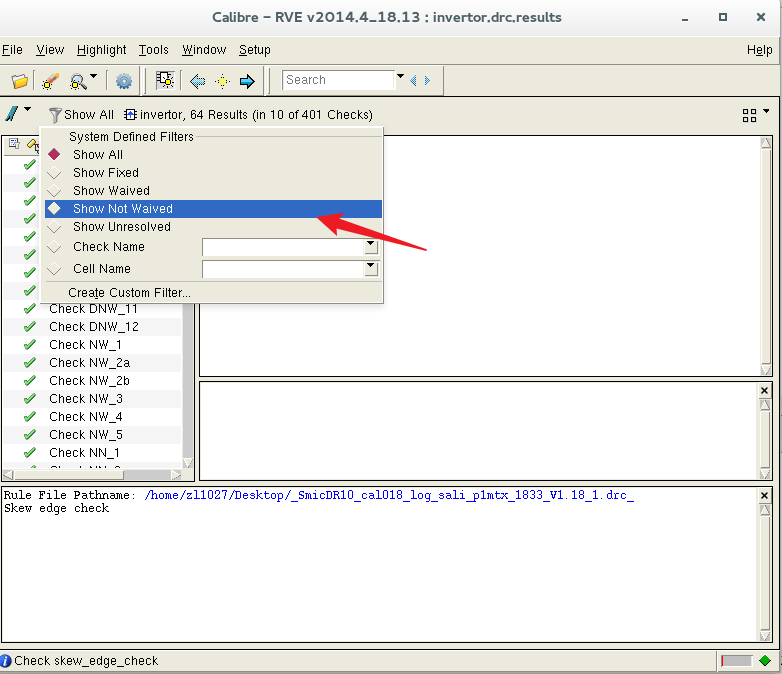

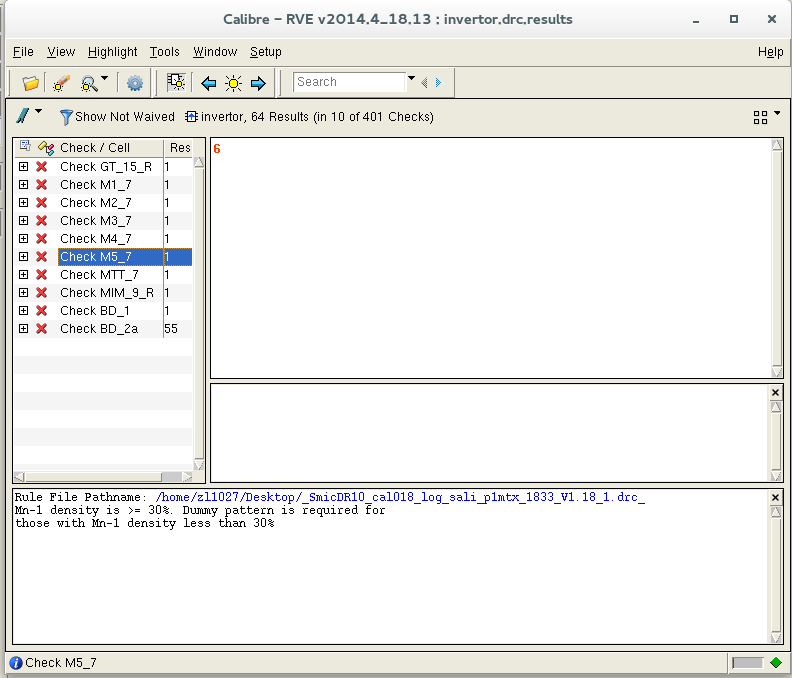

- 运行DRC,根据报错内容修改版图,DRC问题的修改主要参考报错内容以及PDK的Design Rules文档

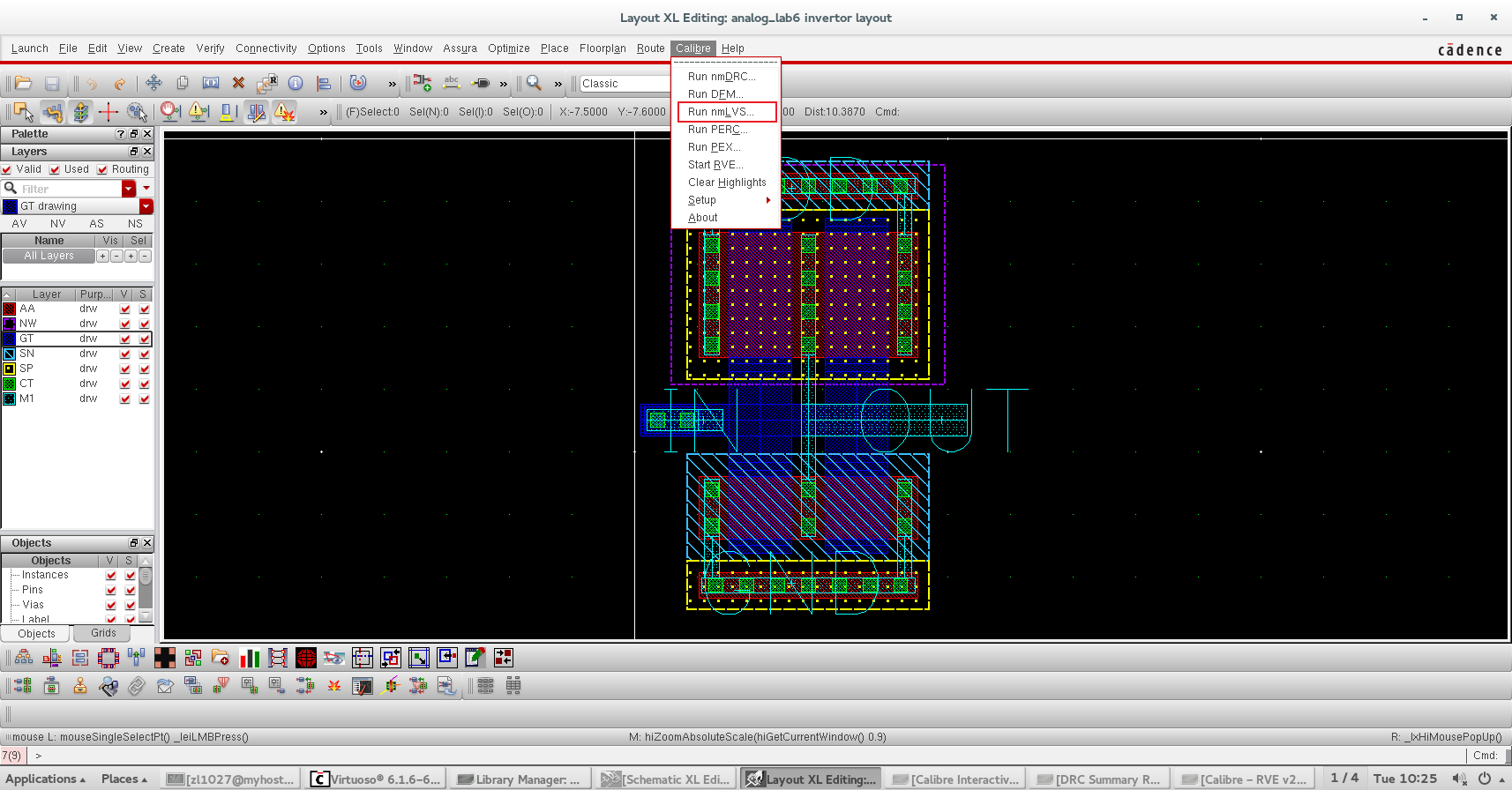

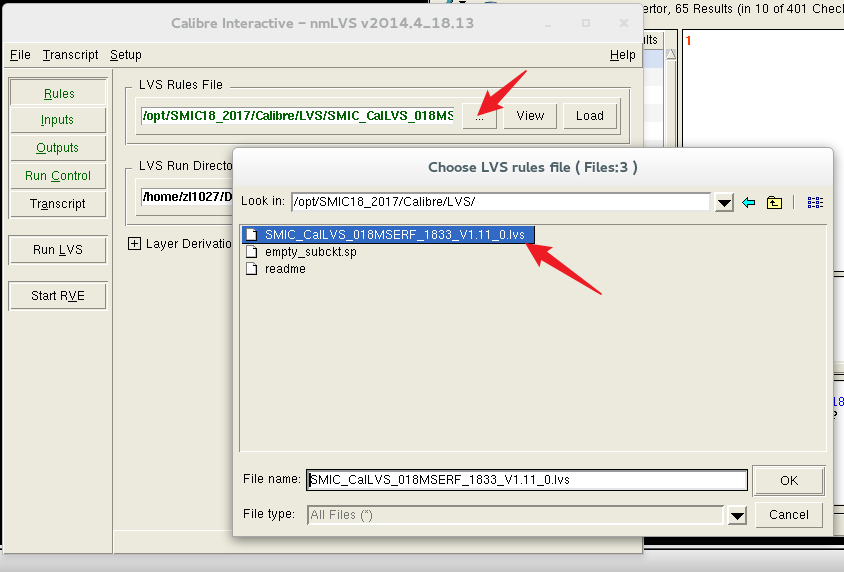

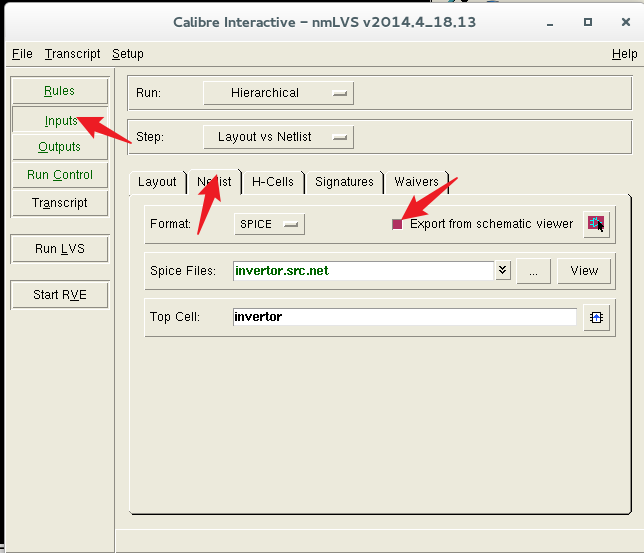

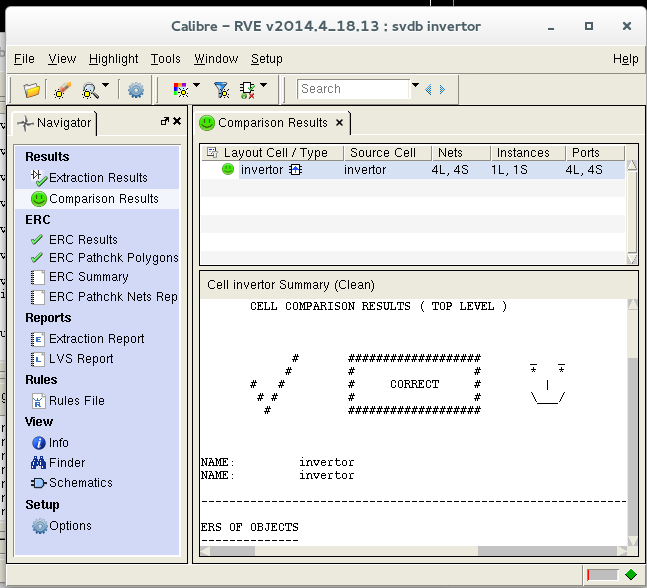

10 .运行LVS,如果原理图和版图是一致的,会显示绿色笑脸😊

6.4 实验分析

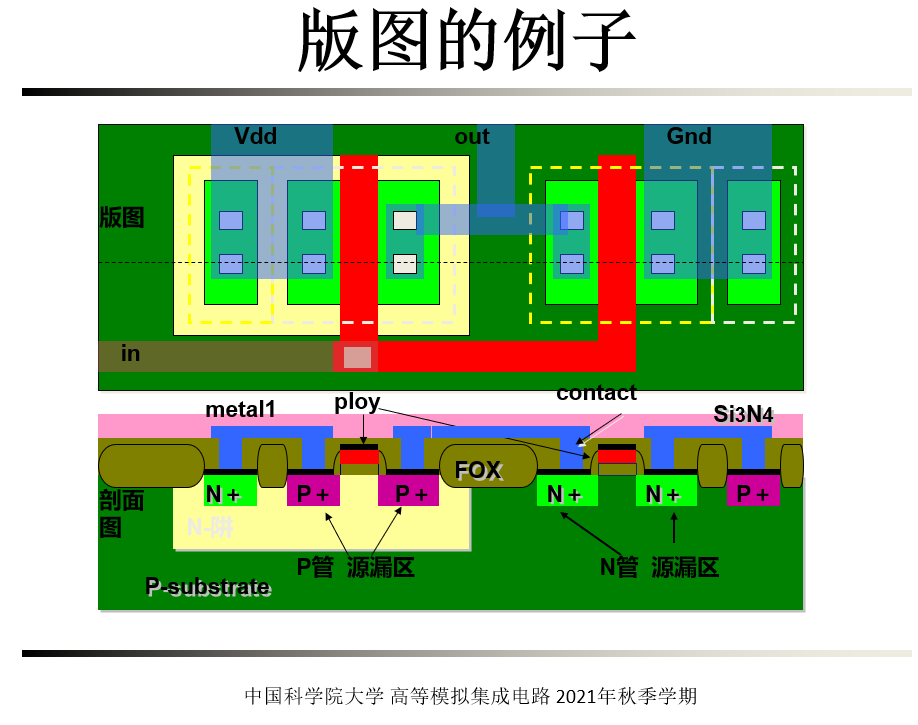

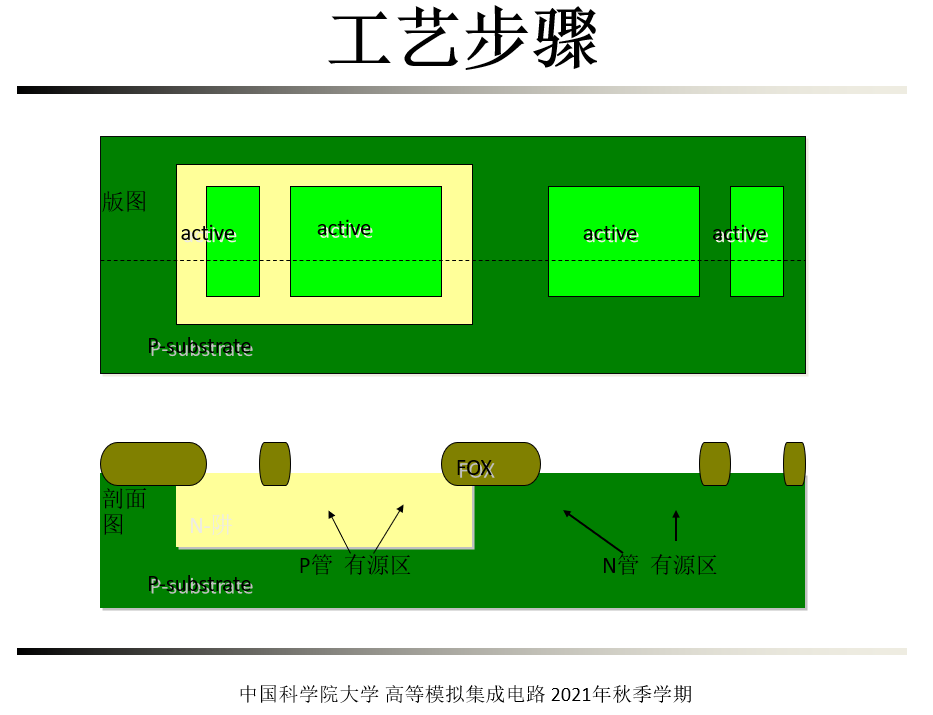

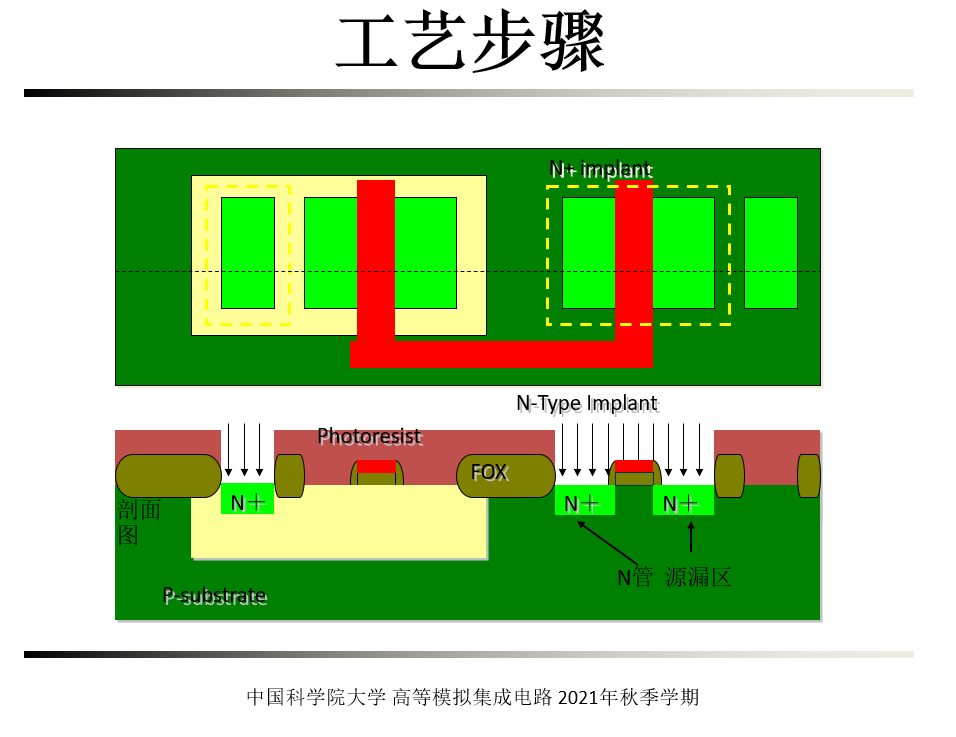

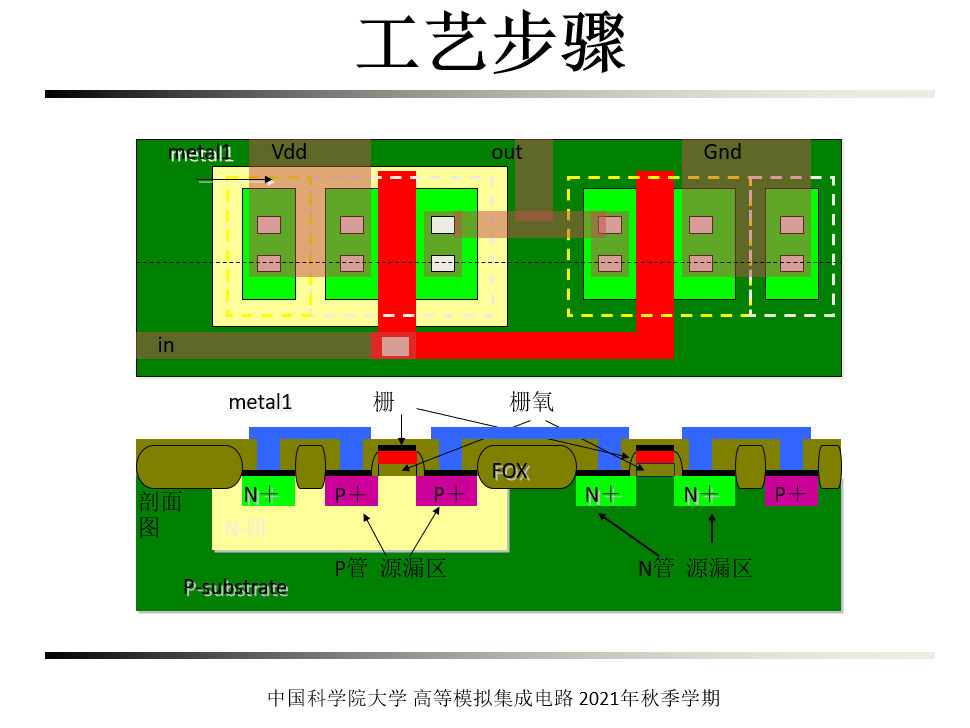

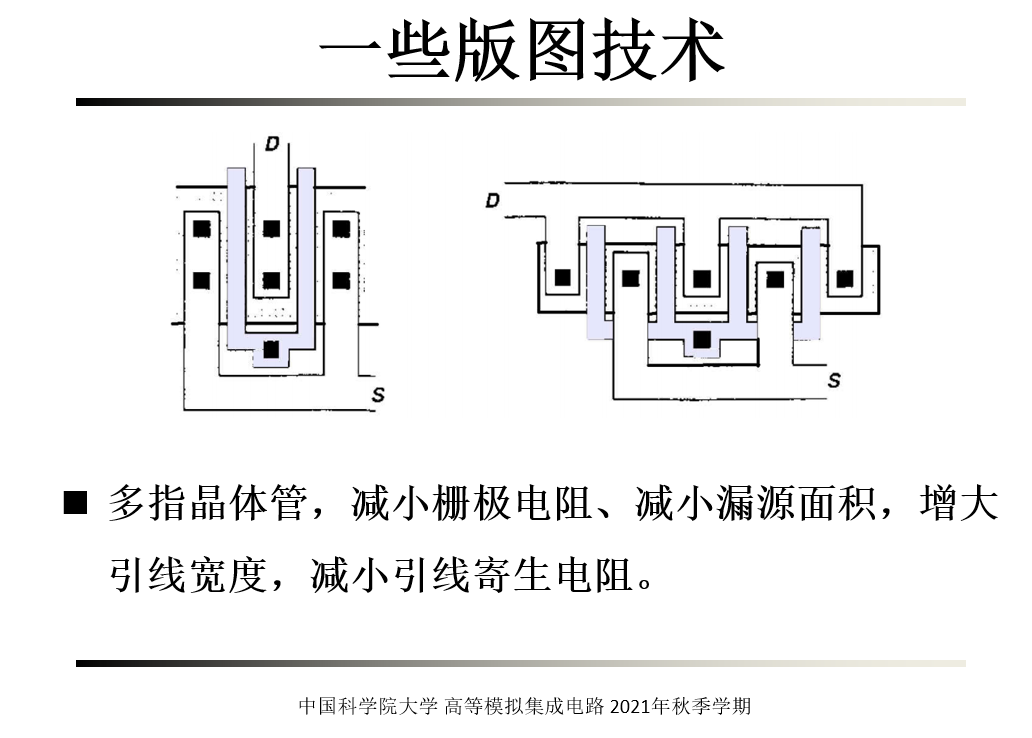

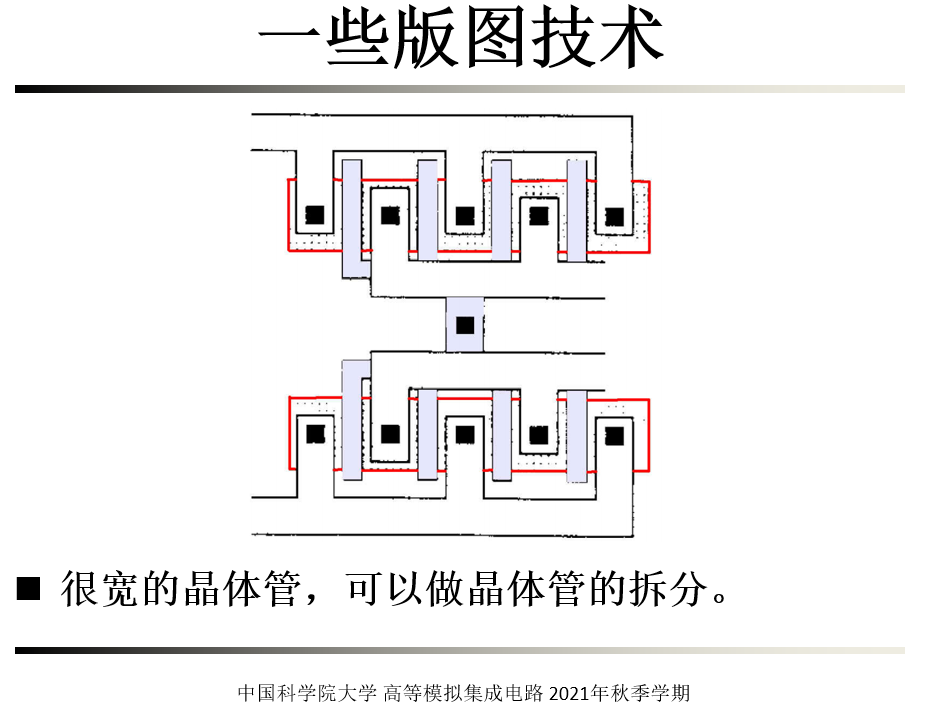

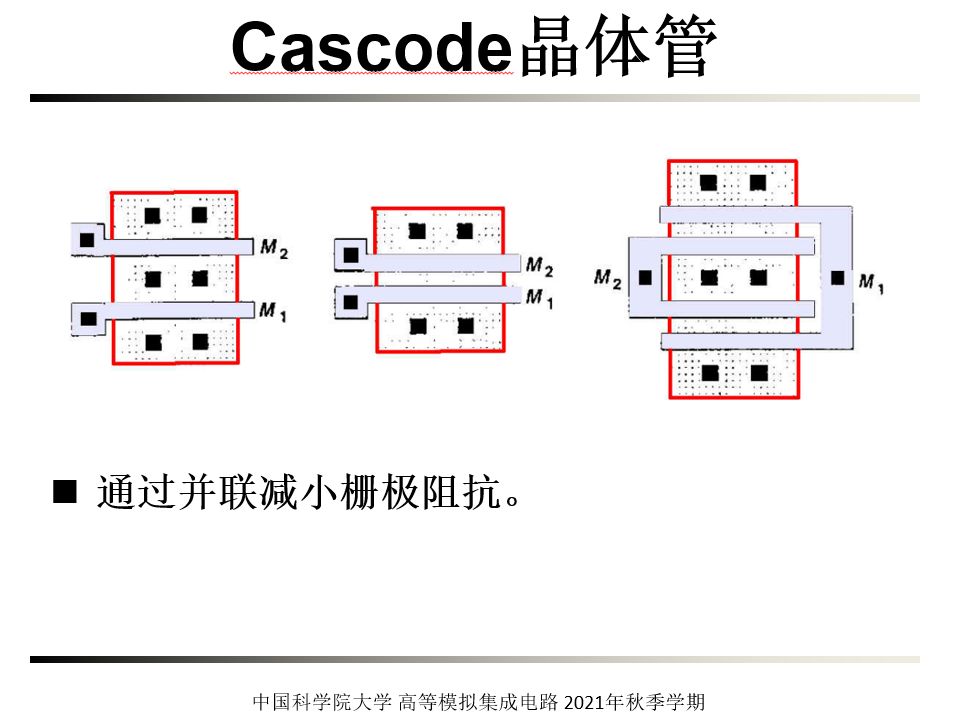

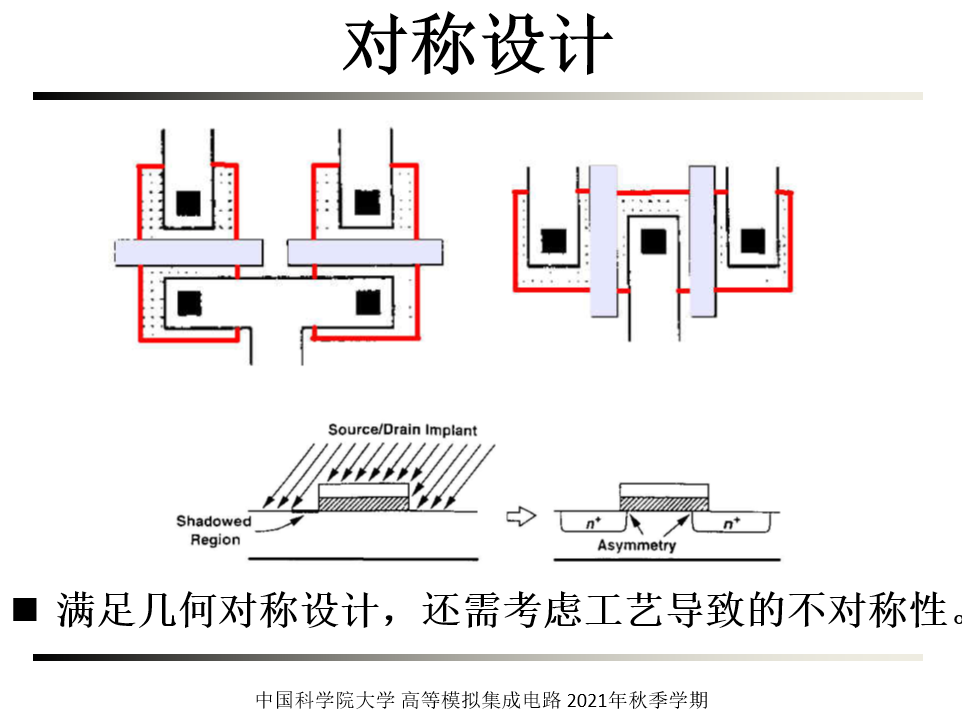

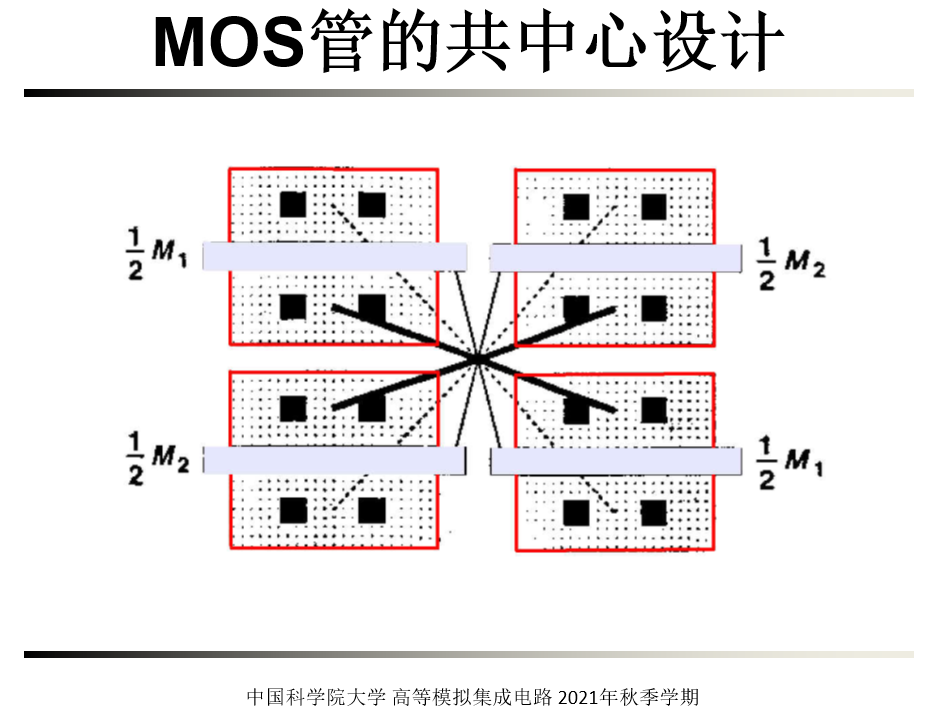

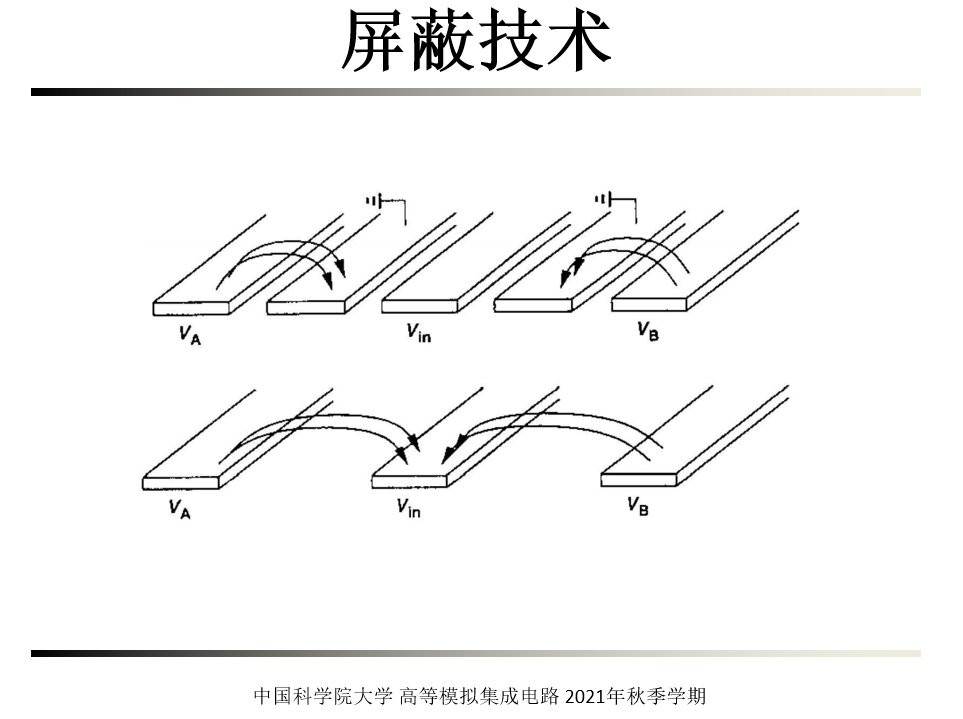

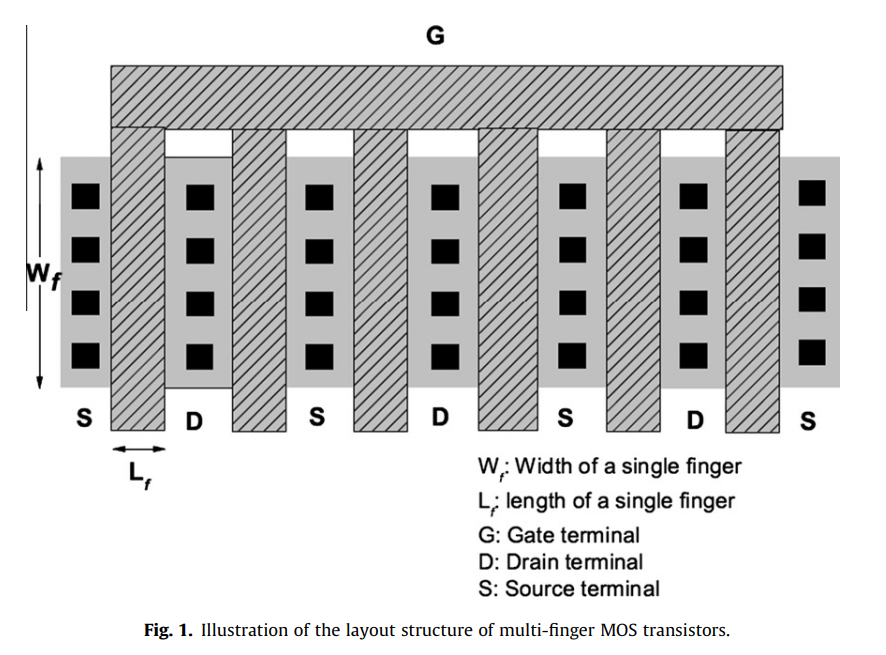

对于W/L很大的晶体管,此时其的栅电阻以及对应的寄生电容都较大,因此在实际设计中会将其设为多 finger 的结构。将其拆分为 finger=2 的 MOS 管后,对应的漏端的结电容 减小了一半。muti-finger晶体管的结构如下:

晶体管的\(W_{total}=W_f\times N_{finger}\),multi-finger晶体管广泛用于Layout技术中。

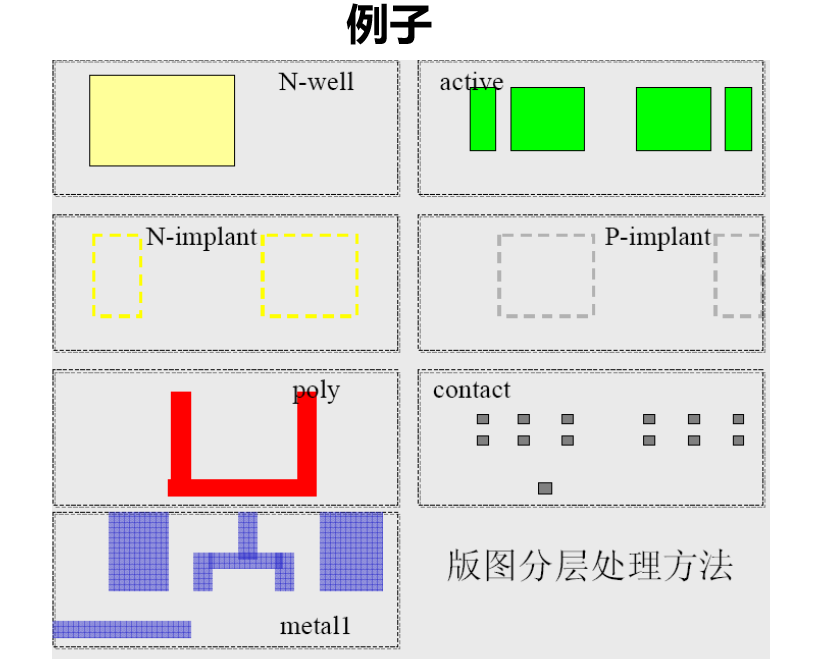

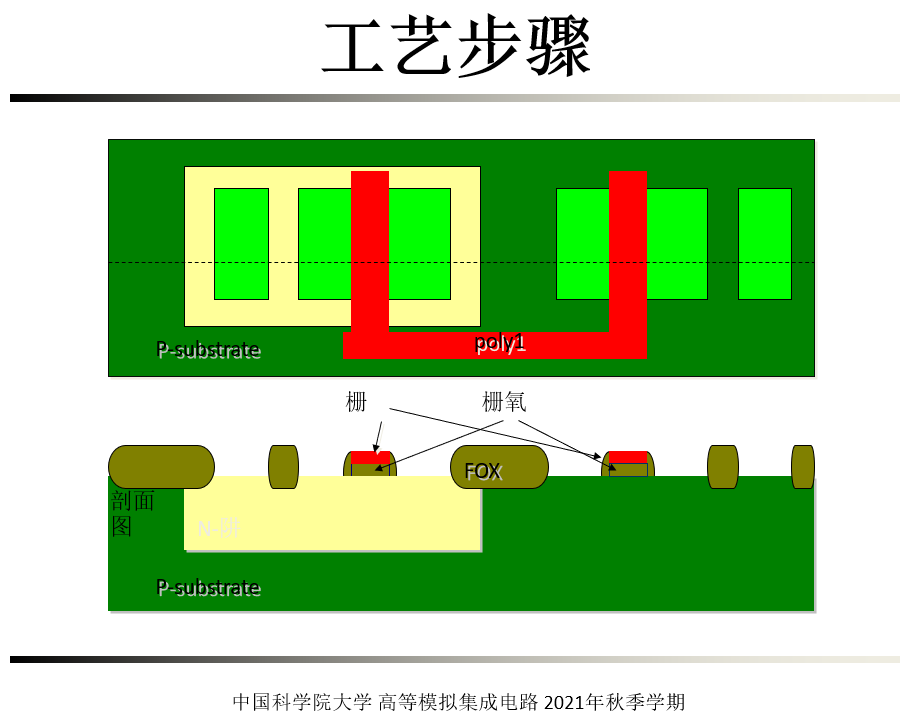

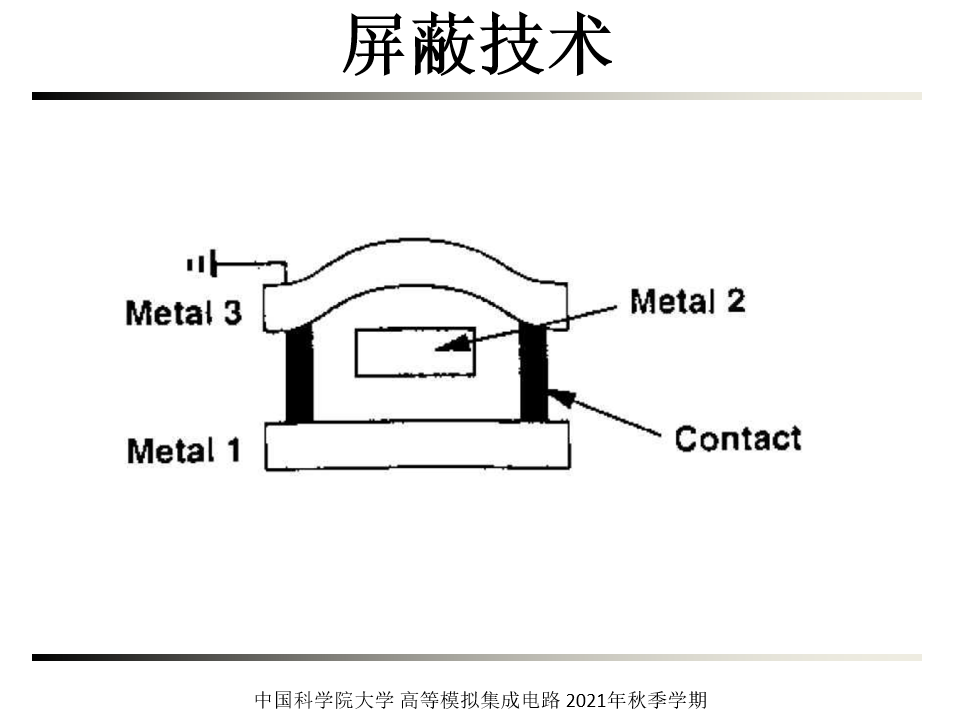

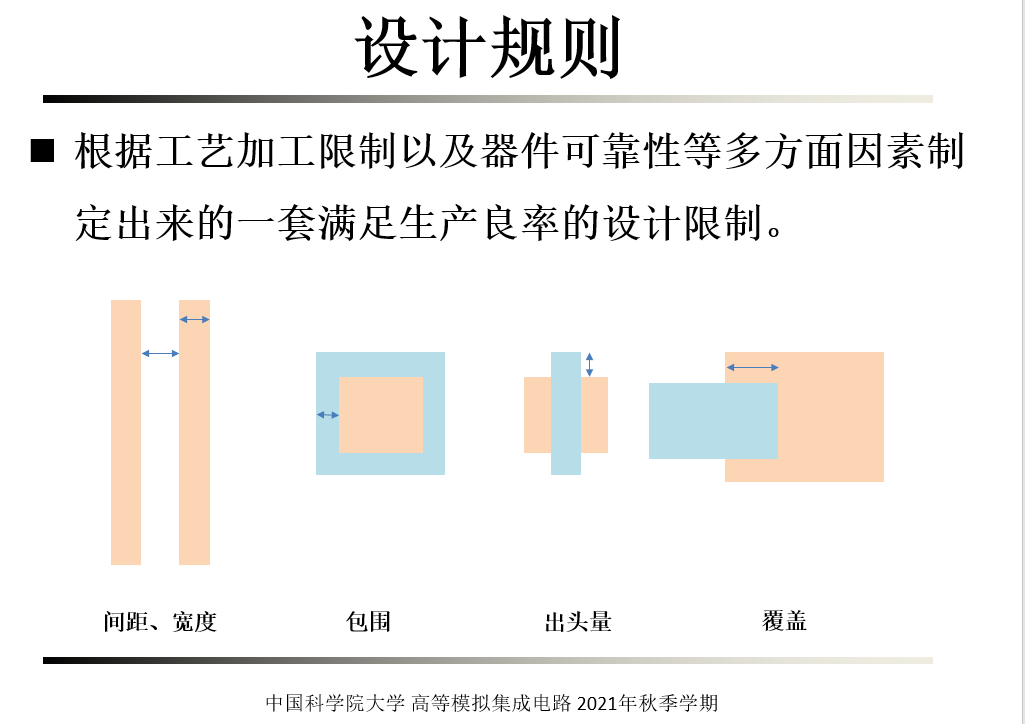

进行Layout时,连线需要在正确的Layer中进行,跨Layer的连接需要依靠通孔。每个Layer的简写和名称的对应关系如下表所示:

| Layer简写 | Layer名称 |

|---|---|

| AA | 有源区(Active Area) |

| NW | N阱(N-Well) |

| GT | 多晶硅栅极(Ploy Gate) |

| SN | N型离子注入区(N+ implant) |

| SP | P型离子注入区(P+ implant) |

| CT | 接触孔(Contact) |

| M1 | 金属层1(Metal-1) |

其他层的说明可以参考PDK的Design Rules文档。

常用快捷键:

-

Save ------- 保存编辑(f2)

-

Fit Edit-------全屏显示所画单元(f)

-

Zoom In -------放大 (Shift+z)

-

Zoom Out ------- 缩小(Ctrl+z)

-

Stretch ------- 伸缩,拉动图形的边或角(s)

-

Copy -------复制编辑 (c)

-

Move ------- 移动(m)

-

Delete ------- 删除编辑(Del)

-

Undo ------- 取消编辑,只能取消一次(u)

-

Properties --------编辑目标属性(q)

-

Instance--------调用单元器件(i)

-

Path -------画等宽线(p)

-

Polygon ------- 编辑多边形图形(Shift+p)

-

Label--------加入文本信息(l)

-

Rectangle -------编辑矩形图形(r)

-

Ruler--------标尺(k)

浙公网安备 33010602011771号

浙公网安备 33010602011771号